---

The AVR32DB28/32/48 devices you have received conform functionally to the current device data sheet ([www.microchip.com/DS40002301](http://www.microchip.com/DS40002301)), except for the anomalies described in this document. The errata described in this document will likely be addressed in future revisions of the AVR32DB28/32/48 devices.

**Notes:**

- This document summarizes all the silicon errata issues from all the silicon revisions, previous and current

- Refer to the Device/Revision ID section in the current device data sheet ([www.microchip.com/DS40002301](http://www.microchip.com/DS40002301)) for more detailed information on Device Identification and Revision IDs for your specific device, or contact your local Microchip sales office for assistance

# 1. Silicon Issue Summary

## Legend

- Erratum is not applicable.

- X Erratum is applicable.

| Peripheral | Short Description                                                                                              | Valid for Silicon Revision |         |

|------------|----------------------------------------------------------------------------------------------------------------|----------------------------|---------|

|            |                                                                                                                | Rev. A1 <sup>(1)</sup>     | Rev. B0 |

| Device     | 2.2.1. Increased Current Consumption May Occur When VDD Drops                                                  | X                          | -       |

|            | 2.2.2. Write Operation Lost if Consecutive Writes to Specific Address Spaces                                   | X                          | X       |

| CLKCTRL    | 2.3.1. The PLL Will Not Run when Using XOSCHF with an External Crystal                                         | X                          | -       |

| DAC        | 2.4.1. DAC Output Buffer Lifetime Drift                                                                        | X                          | -       |

| NVMCTRL    | 2.5.1. Flash Multi-Page Erase Can Erase Write Protected Section                                                | X                          | X       |

|            | 2.5.2. NVM_EEPROM_ERASE Command does Not Respect Write Protect                                                 | X                          | X       |

| TCA        | 2.6.1. Restart Will Reset Counter Direction in NORMAL and FRQ Mode                                             | X                          | -       |

| TCB        | 2.7.1. CCMP and CNT Registers Act as 16-Bit Registers in 8-Bit PWM Mode                                        | X                          | -       |

| TCD        | 2.8.1. Asynchronous Input Events not Working When TCD Counter Prescaler Is Used                                | X                          | -       |

|            | 2.8.2. CMPAEN Controls All WOx for Alternative Pin Functions                                                   | X                          | -       |

|            | 2.8.3. Halting TCD and Waiting for SW Restart Does Not Work if Compare Value A is 0 or Dual Slope Mode is Used | X                          | X       |

| TWI        | 2.9.1. Flush Non-Functional                                                                                    | X                          | X       |

| USART      | 2.10.1. Start-of-Frame Detection Can Unintentionally Be Triggered in Active Mode                               | X                          | -       |

|            | 2.10.2. Receiver Non-Functional after Detection of Inconsistent Synchronization Field                          | X                          | X       |

## Note:

1. This revision is the initial release of the silicon.

## 2. Silicon Errata Issues

### 2.1 Errata Details

- Erratum is not applicable.

- X Erratum is applicable.

### 2.2 Device

#### 2.2.1 Increased Current Consumption May Occur When $V_{DD}$ Drops

The device may experience increased current consumption of approximately 1.5 mA if  $V_{DD}$  drops below 2.1V and is held in the range of 1.9-2.1V. This will only occur if  $V_{DD}$  is originally at a higher level and then drops down to the mentioned voltage range.

##### Work Around

Ensure  $V_{DD}$  is always kept above 2.1V by setting the BOR trigger level to 2.2V to keep the device from executing if  $V_{DD}$  drops towards the affected voltage range. If operation in voltage range 1.9-2.1V is required, make sure  $V_{DD}$  does not rise above 2.1V and then drops down again. Note that the voltage levels given are not absolute values but typical values.

##### Affected Silicon Revisions

|  | Rev. A1 | Rev. B0 |

|--|---------|---------|

|  | X       | -       |

#### 2.2.2 Write Operation Lost if Consecutive Writes to Specific Address Spaces

An ST/STD/STS instruction to address  $\geq 64$  followed by either an ST/STD instruction to address  $< 64$  or a write to the SLPCTRL.CTRLA register will cause a loss of the last write.

##### Work Around

To avoid loss of write operation, use one of the following workarounds depending on address space:

- Insert an NOP instruction before writing to address  $< 64$ , or use the OUT instruction instead of ST/STD

- Insert an NOP instruction before writing to SLPCTRL.CTRLA register

##### Affected Silicon Revisions

|  | Rev. A1 | Rev. B0 |

|--|---------|---------|

|  | X       | X       |

## 2.3 CLKCTRL - Clock Controller

### 2.3.1 The PLL Will Not Run when Using XOSCHF with an External Crystal

When the PLL is configured to run from an external source (SOURCE in CLKCTRL.PLLCTRLA is '1'), the PLL will only run if XOSCHF is configured to use an external clock (SELHF in CLKCTRL.XOSCHFCTRLA is '1'). It will not work with an external crystal.

##### Work Around

None.

##### Affected Silicon Revisions

|  | Rev. A1 | Rev. B0 |

|--|---------|---------|

|  | X       | -       |

## 2.4 DAC - Digital-to-Analog Converter

### 2.4.1 DAC Output Buffer Lifetime Drift

The offset of the DAC output buffer can drift over the device's lifetime if powered with the DAC output buffer disabled.

#### Work Around

Keep the DAC output buffer enabled (OUTEN in DACn.CTRLA is '1') continuously or compensate by measuring the DAC output voltage offset with the ADC and adjust the DAC data register value (DATA[9:0] in DACn.DATA) accordingly.

#### Affected Silicon Revisions

| Rev. A1 | Rev. B0 |

|---------|---------|

| X       | -       |

## 2.5 NVMCTRL - Nonvolatile Memory Controller

### 2.5.1 Flash Multi-Page Erase Can Erase Write Protected Section

When using Flash Multi-Page Erase mode, only the first page in the selected address range is verified to be within a section that is not write-protected. If the address range includes any write-protected Application Data pages, it will erase them.

#### Work Around

None.

#### Affected Silicon Revisions

| Rev. A1 | Rev. B0 |

|---------|---------|

| X       | X       |

### 2.5.2 NVM\_EEPROM\_ERASE Command does Not Respect Write Protect

The NVM\_EEPROM\_ERASE command does not respect the EEPROM Write Protected (EEWP) bit in the Control B (NVMCTRL.CTRLB) register. Content will be erased even though it should not.

#### Work Around

None.

#### Affected Silicon Revisions

| Rev. A1 | Rev. B0 |

|---------|---------|

| X       | X       |

## 2.6 TCA - 16-Bit Timer/Counter Type A

### 2.6.1 Restart Will Reset Counter Direction in NORMAL and FRQ Mode

When the TCA is configured to a NORMAL or FRQ mode (WGMODE in TCAx.CTRLB is '0x0' or '0x1'), a RESTART command or Restart event will reset the count direction to default. The default is counting upwards.

#### Work Around

None.

#### Affected Silicon Revisions

| Rev. A1 | Rev. B0 |

|---------|---------|

| X       | -       |

## 2.7 TCB - 16-Bit Timer/Counter Type B

### 2.7.1 CCMP and CNT Registers Act as 16-Bit Registers in 8-Bit PWM Mode

When the TCB is operating in 8-bit PWM mode (CNTMODE in TCBn.CTRLB is '0x7'), the low and high bytes for the CCMP and CNT registers act as 16-bit registers for read and write. They cannot be read or written independently.

#### Work Around

Use 16-bit register access. Refer to the data sheet for further information.

#### Affected Silicon Revisions

|  | Rev. A1 | Rev. B0 |

|--|---------|---------|

|  | X       | -       |

## 2.8 TCD - 12-Bit Timer/Counter Type D

### 2.8.1 Asynchronous Input Events not Working When TCD Counter Prescaler Is Used

When configuring TCD to use asynchronous input events (CFG in TCDn.EVCTRLx is '0x2') and the TCD Counter Prescaler (CNTPRES in TCDn.CTRLA) is different from '0x0', events can be missed.

#### Work Around

Use the TCD Synchronization Prescaler (SYNCPRES in TCDn.CTRLA) instead of the TCD Counter Prescaler. Alternatively, use synchronous input events (CFG in TCDn.EVCTRLx is not '0x2') if the input events are longer than one CLK\_TCD\_CNT cycle.

#### Affected Silicon Revisions

|  | Rev. A1 | Rev. B0 |

|--|---------|---------|

|  | X       | -       |

### 2.8.2 CMPAEN Controls All WOx for Alternative Pin Functions

When TCD alternative pins are enabled (TCD0 in PORTMUX.TCDROUTEA is not '0x0'), all waveform outputs (WOx) are controlled by Compare A Enable (CMPAEN in TCDnFAULTCTRL).

#### Work Around

None.

#### Affected Silicon Revisions

|  | Rev. A1 | Rev. B0 |

|--|---------|---------|

|  | X       | -       |

### 2.8.3 Halting TCD and Waiting for SW Restart Does Not Work if Compare Value A is 0 or Dual Slope Mode is Used

Halting TCD and waiting for software restart (INPUTMODE in TCDn.INPUTCTRLA is '0x7') does not work if compare value A is 0 (CMPASET in TCDn.CMPASET is '0x0') or Dual Slope mode is used (WGMODE in TCDn.CTRLB is '0x3').

#### Work Around

Configure the compare value A (CMPASET in TCDn.CMPASET) to be different from 0 and do not use Dual Slope mode (WGMODE in TCDn.CTRLB is not '0x3').

#### Affected Silicon Revisions

|  | Rev. A1 | Rev. B0 |

|--|---------|---------|

|  | X       | X       |

## 2.9 TWI - Two-Wire Interface

### 2.9.1 Flush Non-Functional

Issuing a Flush by writing to the FLUSH bit in TWIn.MCTRLB can cause the TWI Host to be stuck in the Unknown bus state (see BUSSTATE in TWIn.MSTATUS).

#### Work Around

Disable and re-enable the Host using the ENABLE bit in TWIn.MCTRLA. An ordinary operation does not require the use of FLUSH.

#### Affected Silicon Revisions

| Rev. A1 | Rev. B0 |

|---------|---------|

| X       | X       |

## 2.10 USART - Universal Synchronous and Asynchronous Receiver and Transmitter

### 2.10.1 Start-of-Frame Detection Can Unintentionally Be Triggered in Active Mode

The Start-of-Frame Detection feature enables the USART to wake up from Standby sleep mode upon data reception. The Start-of-Frame Detector can unintentionally be triggered when the Start-of-Frame Detection Enable (SFDEN) bit in the USART Control B (USARTn.CTRLB) register is set, and the device is in Active mode. If the Receive Data (RXDATA) registers are read while receiving new data, the Receive Complete Interrupt Flag (RXCIF) in the USARTn.STATUS register is cleared. This triggers the Start-of-Frame Detector and falsely detects the next falling edge as a start bit. When the Start-of-Frame Detector detects a start condition, the frame reception is restarted, resulting in corrupt received data. Note that the USART Receive Start Interrupt Flag (RXSIF) always is '0' when in Active mode. No interrupt will be triggered.

#### Work Around

Disable Start-of-Frame Detection by writing '0' to the Start-of-Frame Detection Enable (SFDEN) bit in the USART Control B (USARTn.CTRLB) register when the device is in Active mode. Re-enable it by writing the bit to '1' before transitioning to Standby sleep mode. This work around depends on a protocol preventing a new incoming frame when re-enabling Start-of-Frame Detection. Re-enabling Start-of-Frame Detection, while a new frame is already incoming, will result in corrupted received data.

#### Affected Silicon Revisions

| Rev. A1 | Rev. B0 |

|---------|---------|

| X       | -       |

### 2.10.2 Receiver Non-Functional after Detection of Inconsistent Synchronization Field

The USART Receiver becomes non-functional when the Inconsistent Synchronization Field Interrupt Flag (ISFIF) in the Status (USARTn.STATUS) register is set. The ISFIF interrupt flag is set when the Receiver Mode (RXMODE) bit field in the Control B (USARTn.CTRLB) register is configured to Generic Auto-Baud (GENAUTO) or LIN Constrained Auto-Baud (LINAUTO) mode, and the received synchronization frame does not conform to the conditions described in the data sheet. Clearing the flag does not re-enable the USART Receiver.

#### Work Around

When the ISFIF interrupt flag is set, disable and re-enable the USART Receiver by first writing a '0' and then a '1' to the Receiver Enable (RXEN) bit in the Control B (USARTn.CTRLB) register.

#### Affected Silicon Revisions

| Rev. A1 | Rev. B0 |

|---------|---------|

| X       | X       |

### 3. Data Sheet Clarifications

Note the following typographic corrections and clarifications for the latest version of the device data sheet ([www.microchip.com/DS40002301](http://www.microchip.com/DS40002301)).

**Note:** Corrections are shown in **bold**. Where possible, the original bold text formatting has been removed for clarity.

#### 3.1 Device

##### 3.1.1 Features

A clarification has been made to change the Flash endurance specification in the *Memories* bullet point in the *Features* list.

- Memories

- 32 KB in-system self-programmable Flash memory

- 512B EEPROM

- 4 KB SRAM

- 32B of user row in nonvolatile memory that can keep data during chip-erase and be programmed while the device is locked

- Write/erase endurance

- Flash: **1,000** cycles

- EEPROM: 100,000 cycles

- Data retention: 40 years at 55°C

##### 3.1.2 FUSE - Configuration and User Fuses - SYSCFG0

A clarification of the EEPROM Save During Chip Erase (EESAVE) fuse description in the System Configuration 0 (SYSCFG0, section 8.8.2.4) fuse has been made.

Bit 0 - EESAVE EEPROM Saved During Chip Erase

This bit controls if the EEPROM will be erased or saved during a chip erase.

| Value | Name    | Description                                                                                  |

|-------|---------|----------------------------------------------------------------------------------------------|

| 0     | DISABLE | EEPROM is erased during a chip erase                                                         |

| 1     | ENABLE  | EEPROM is saved during a chip erase <b>regardless of whether the device is locked or not</b> |

#### 3.2 SPI - Serial Peripheral Interface

##### 3.2.1 SPI - Serial Peripheral Interface

A clarification has been made to the *Operation - Client Mode* section. The last sentence is removed.

28.3.2.2 Client Mode

In Client mode, the SPI peripheral receives the SPI clock and Client Select from a Host. Client mode supports three operational modes: One Normal mode and two configurations for the Buffered mode. In Client mode, the control logic will sample the incoming signal on the SCK pin.

##### 3.2.2 SPI - Serial Peripheral Interface

A clarification has been made to the *Operation - Client Mode - Buffer Mode* section.

28.3.2.2.2 Buffer Mode

To avoid data collisions, the SPI peripheral can be configured in Buffered mode by writing a '1' to the Buffer Mode Enable (BUFEN) bit in the Control B (SPIn.CTRLB) register.

In this mode, the SPI has additional interrupt flags and extra buffers. The extra buffers are shown in Figure 28-1. There are two different modes for the Buffer mode, selected with the Buffer mode Wait for Receive (BUFWR) bit. The two different modes are described below with timing diagrams.

**Note: When operating as a client in Buffered mode and the SPI clock is close to maximum frequency, the client may not be able to set up data in time for the first sample edge during back-to-back transfers. Refer to the *Electrical Characteristics - SPI* section for details.**

### 3.3 AC - Analog Comparator

#### 3.3.1 Analog Comparator Interrupt Control

A clarification of the Interrupt Mode (INTMODE) bit field of the AC Interrupt Control (ACn.INTCTRL, section 32.5.5) register has been made.

Table 32-4. Interrupt Generation with Single Comparator

| Value | Name     | Description                                     |

|-------|----------|-------------------------------------------------|

| 0x0   | BOTHEDGE | Positive and negative inputs crosses            |

| 0x1   | -        | Reserved                                        |

| 0x2   | NEGEDGE  | Positive input goes <b>below</b> negative input |

| 0x3   | POSEDGE  | Positive input goes <b>above</b> negative input |

### 3.4 DAC - Digital to Analog Converter

#### 3.4.1 DAC Output

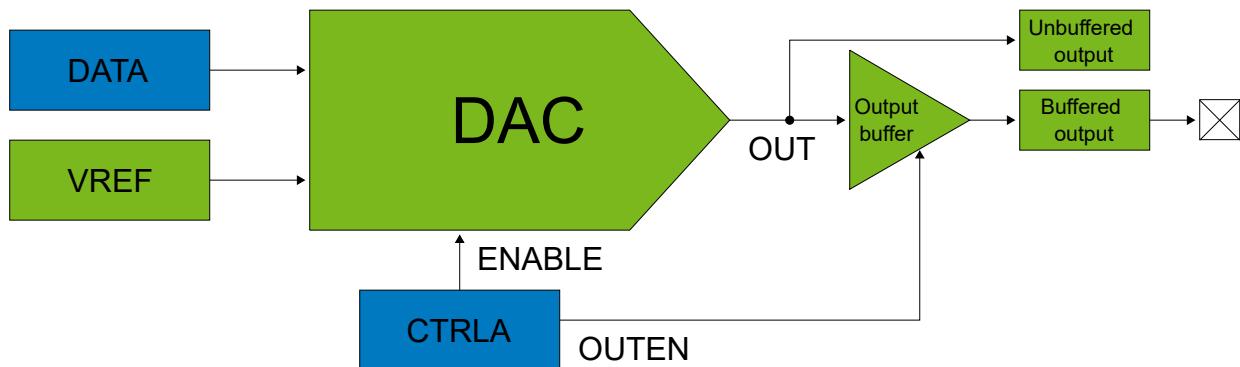

Clarifications of the block diagram and the DAC Output sub-section of the DAC peripheral has been made:

1. The block diagram is updated with clarifications to the output signal routing (buffered/unbuffered) and will replace the original block diagram.

2. Sections 34.3.2.3 (DAC as Source For Internal Peripherals) and 34.3.2.4 (DAC Output on Pin) are replaced by section 34.3.2.3 DAC Output.

Figure 34-1. DAC Block Diagram

#### 34.3.2.3 DAC Output

The DAC can be used as an output to a pin and as an input to the peripherals in the table below.

| DAC Output        | Peripheral Input                                                                                                    | Notes                                                                                                                                   |

|-------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| <b>Unbuffered</b> | <ul style="list-style-type: none"> <li>Analog Comparator (AC)</li> <li>Analog to Digital Converter (ADC)</li> </ul> | The peripheral is connected to the unbuffered DAC output. See section 34.3.2.3.1. Unbuffered Output as Source For Internal Peripherals. |

| <b>Buffered</b>   | <ul style="list-style-type: none"> <li>Analog Signal Conditioning (OPAMP)</li> </ul>                                | The peripheral is connected to the DAC Output pin. See section 34.3.2.3.2. Buffered Output.                                             |

### 34.3.2.3.1 Unbuffered Output as Source For Internal Peripherals

The unbuffered analog output of the DAC can be internally connected to other peripherals when the ENABLE bit in the Control A (DACn.CTRLA) register is written to '1'. When only the DAC unbuffered analog output is used, the Output Buffer Enable (OUTEN) bit in DACn.CTRLA can be '0', freeing the pin to be used by other peripherals.

### 34.3.2.3.2 Buffered Output

The buffered analog output of the DAC can be enabled by writing a '1' to the Output Buffer Enable (OUTEN) bit in the Control A (DACn.CTRLA) register. The pin used by the DAC must have the input disabled from the Port peripheral. Refer to the *Electrical Characteristics* section for information about the drive capabilities of the DAC output buffer.

## 3.5 Electrical Characteristics

### 3.5.1 I/O Pin Characteristics

Some clarifications have been made to the *I/O Pin Characteristics* table. Note that one footnote has been deleted.

**Table 39-7. I/O Pin Characteristics<sup>(1)</sup>**

| Symbol                               | Description                  | Min.                | Typ. $\pm$ | Max.                | Units | Conditions |

|--------------------------------------|------------------------------|---------------------|------------|---------------------|-------|------------|

| Input Low Voltage                    |                              |                     |            |                     |       |            |

| I/O PORT:                            |                              |                     |            |                     |       |            |

| $V_{IL}$                             | With Schmitt Trigger buffer  | —                   | —          | $0.2 \times V_{DD}$ | V     |            |

|                                      | With I <sup>2</sup> C levels | —                   | —          | $0.3 \times V_{DD}$ | V     |            |

|                                      | With SMBus 3.0 levels        | —                   | —          | 0.8                 | V     |            |

|                                      | RESET Pin                    | —                   | —          | $0.2 \times V_{DD}$ | V     |            |

|                                      | TTL level                    | —                   | —          | 0.8                 | V     |            |

| Input High Voltage                   |                              |                     |            |                     |       |            |

| $V_{IH}$                             | I/O PORT:                    |                     |            |                     |       |            |

|                                      | With Schmitt Trigger buffer  | $0.8 \times V_{DD}$ | —          | —                   | V     |            |

|                                      | With I <sup>2</sup> C levels | $0.7 \times V_{DD}$ | —          | —                   | V     |            |

|                                      | With SMBus 3.0 levels        | 1.35                | —          | —                   | V     |            |

|                                      | RESET Pin                    | $0.8 \times V_{DD}$ | —          | —                   | V     |            |

| Input Leakage Current <sup>(2)</sup> |                              |                     |            |                     |       |            |

## .....continued

| Symbol                                                                                                                                                                                                                                            | Description              | Min.         | Typ. $\dagger$ | Max. | Units   | Conditions                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------|----------------|------|---------|--------------------------------------------------------------------------------|

| $I_{IL}$                                                                                                                                                                                                                                          | I/O PORTS <sup>(3)</sup> | —            | <5             | —    | nA      | $GND \leq V_{PIN} \leq V_{DD}$ ,<br>pin at high-impedance, $T_A = 85^\circ C$  |

|                                                                                                                                                                                                                                                   |                          | —            | <5             | —    | nA      | $GND \leq V_{PIN} \leq V_{DD}$ ,<br>pin at high-impedance, $T_A = 125^\circ C$ |

|                                                                                                                                                                                                                                                   | RESET Pin <sup>(4)</sup> | —            | $\pm 50$       | —    | nA      | $GND \leq V_{PIN} \leq V_{DD}$ ,<br>pin at high-impedance, $T_A = 85^\circ C$  |

| Pull-up Current                                                                                                                                                                                                                                   |                          |              |                |      |         |                                                                                |

| $I_{PUR}$                                                                                                                                                                                                                                         |                          | —            | 140            | —    | $\mu A$ | $V_{DD} = 3.0V$ , $V_{PIN} = GND$                                              |

| Output Low Voltage                                                                                                                                                                                                                                |                          |              |                |      |         |                                                                                |

| $V_{OL}$                                                                                                                                                                                                                                          | Standard I/O Ports       | —            | —              | 0.6  | V       | $I_{OL} = 10 \text{ mA}$ , $V_{DD} = 3.0V$                                     |

| Output High Voltage                                                                                                                                                                                                                               |                          |              |                |      |         |                                                                                |

| $V_{OH}$                                                                                                                                                                                                                                          | Standard I/O Ports       | $V_{DD}-0.7$ | —              | —    | V       | $I_{OH} = 6 \text{ mA}$ , $V_{DD} = 3.0V$                                      |

| I/O Slew Rate                                                                                                                                                                                                                                     |                          |              |                |      |         |                                                                                |

| $t_{SR}$                                                                                                                                                                                                                                          | Rising slew rate         | —            | 22             | —    | ns      | <b>PORTCTRL.SRL = 0x00</b>                                                     |

|                                                                                                                                                                                                                                                   | Rising slew rate         | —            | 45             | —    | ns      | <b>PORTCTRL.SRL = 0x01</b>                                                     |

|                                                                                                                                                                                                                                                   | Falling slew rate        | —            | 30             | —    | ns      | <b>PORTCTRL.SRL = 0x01</b>                                                     |

|                                                                                                                                                                                                                                                   | Falling slew rate        | —            | 16             | —    | ns      | <b>PORTCTRL.SRL = 0x00</b>                                                     |

| Pin Capacitance                                                                                                                                                                                                                                   |                          |              |                |      |         |                                                                                |

| $C_{IO}$                                                                                                                                                                                                                                          | OPAMP output             | —            | 9              | —    | pF      |                                                                                |

|                                                                                                                                                                                                                                                   | $V_{REF}$ pin            | —            | 7              | —    | pF      |                                                                                |

|                                                                                                                                                                                                                                                   | XTAL pins                | —            | 4              | —    | pF      |                                                                                |

|                                                                                                                                                                                                                                                   | Other pins               | —            | 4              | —    | pF      |                                                                                |

| <b><math>\dagger</math> Data in the "Typ." column is at <math>T_A = 25^\circ C</math> and <math>V_{DD} = 3.0V</math> unless otherwise specified. These parameters are for design guidance only and are not tested.</b>                            |                          |              |                |      |         |                                                                                |

| <b>Notes:</b>                                                                                                                                                                                                                                     |                          |              |                |      |         |                                                                                |

| 1. These figures are valid for all I/O ports regardless of if they are connected to the $V_{DD}$ or $V_{DDIO2}$ power domain.                                                                                                                     |                          |              |                |      |         |                                                                                |

| 2. The negative current is defined as the current sourced by the pin.                                                                                                                                                                             |                          |              |                |      |         |                                                                                |

| 3. The leakage current numbers for I/O PORTS are valid also when the pin is used as an input to an enabled analog peripheral.                                                                                                                     |                          |              |                |      |         |                                                                                |

| 4. The leakage current on the $\overline{\text{RESET}}$ pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. A higher leakage current may be measured at different input voltages. |                          |              |                |      |         |                                                                                |

### 3.5.2 Electrical Characteristics - Memory Programming Specifications

A clarification has been made to change the Flash memory cell endurance specification in the *Memory Programming Specifications* table.

**Table 39-8. Memory Programming Specifications**

| Symbol                            | Description                             | Min. | Typ | Max. | Units              | Conditions                                    |

|-----------------------------------|-----------------------------------------|------|-----|------|--------------------|-----------------------------------------------|

| Data EEPROM Memory Specifications |                                         |      |     |      |                    |                                               |

| $E_D$                             | Data EEPROM byte endurance              | 100k | —   | —    | Erase/Write cycles | $-40^\circ C \leq T_A \leq +85^\circ C$       |

| $t_{D\_RET}$                      | Characteristic retention                | —    | 40  | —    | Year               | Provided no other specifications are violated |

| $N_{D\_REF}$                      | Total Erase/Write cycles before refresh | 1M   | 4M  | —    | Erase/Write cycles | $-40^\circ C \leq T_A \leq +85^\circ C$       |

| $t_{D\_CE}$                       | Full EEPROM Erase                       | —    | 10  | —    | ms                 |                                               |

.....continued

| Symbol                                                                                                                                                                                   | Description                                | Min.                    | Typ | Max.        | Units              | Conditions                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------|-----|-------------|--------------------|---------------------------------------------------------|

| $V_{D\_RW}$                                                                                                                                                                              | $V_{DD}$ for Read or Erase/Write operation | $V_{DDMIN}$             | —   | $V_{DDMAX}$ | V                  |                                                         |

| $t_{D\_BEW}$                                                                                                                                                                             | Byte Erase and Write cycle time            | —                       | 11  | —           | ms                 |                                                         |

| Program Flash Memory Specifications                                                                                                                                                      |                                            |                         |     |             |                    |                                                         |

| $E_p$                                                                                                                                                                                    | <b>Flash memory cell endurance</b>         | <b>1k</b>               | —   | —           | Erase/Write cycles | $-40^{\circ}\text{C} \leq T_A \leq +85^{\circ}\text{C}$ |

| $t_{P\_RET}$                                                                                                                                                                             | Characteristic retention                   | —                       | 40  | —           | Year               | Provided no other specifications are violated           |

| $V_{P\_RD}$                                                                                                                                                                              | $V_{DD}$ for Read operation                | $V_{DDMIN}$             | —   | $V_{DDMAX}$ | V                  |                                                         |

| $V_{P\_REW}$                                                                                                                                                                             | $V_{DD}$ for Erase/Write operation         | $V_{DD}$ <sup>(2)</sup> | —   | $V_{DDMAX}$ | V                  |                                                         |

| $t_{P\_PE}$                                                                                                                                                                              | Page Erase                                 | —                       | 10  | —           | ms                 |                                                         |

| $t_{P\_CE}$                                                                                                                                                                              | Chip Erase                                 | —                       | —   | —           | ms                 |                                                         |

| $t_{P\_WRD}$                                                                                                                                                                             | Byte/Word Write                            | —                       | 70  | —           | $\mu\text{s}$      |                                                         |

| <b>Notes:</b>                                                                                                                                                                            |                                            |                         |     |             |                    |                                                         |

| 1. These parameters are not tested but ensured by design.                                                                                                                                |                                            |                         |     |             |                    |                                                         |

| 2. During Chip Erase, the Brown-out Detector (BOD) configured with BODLEVEL0 is forced ON. If the supply voltage $V_{DD}$ is below $V_{BOD}$ for BODLEVEL0, the erase attempt will fail. |                                            |                         |     |             |                    |                                                         |

### 3.5.3 Electrical Characteristics - SPI

Some clarifications have been made to the *Timing Specifications in Host Mode* and *Timing Specifications in Client Mode* tables. Note that some rows have been deleted.

**Table 39-20. SPI - Timing Specifications in Host Mode**

| Symbol      | Description         | Min.                    | Typ. †               | Max.             | Unit | Condition |

|-------------|---------------------|-------------------------|----------------------|------------------|------|-----------|

| $f_{SCK}^*$ | SCK clock frequency | —                       | —                    | $f_{CLK\_PER}/2$ | MHz  |           |

| $T_{SCK}^*$ | SCK period          | $2 \times T_{CLK\_PER}$ | —                    | —                | ns   |           |

| $t_{SCKW}$  | SCK high/low width  | —                       | $0.5 \times T_{SCK}$ | —                | ns   |           |

| $t_{MIS}$   | MISO setup to SCK   | —                       | $T_{CLK\_PER}$       | —                | ns   |           |

| $t_{MIH}$   | MISO hold after SCK | —                       | 0                    | —                | ns   |           |

| $t_{MOS}$   | MOSI setup to SCK   | —                       | $0.5 \times T_{SCK}$ | —                | ns   |           |

| $t_{MOH}$   | MOSI hold after SCK | —                       | $0.5 \times T_{SCK}$ | —                | ns   |           |

† Unless otherwise specified, data in the "Typ." column is at  $T_A = 25^{\circ}\text{C}$  and  $V_{DD} = 3.0\text{V}$ . These parameters are not tested and are for design guidance only.

\* These parameters are characterized but not tested in production.

**Table 39-21. SPI - Timing Specifications in Client Mode**

| Symbol        | Description                | Min.                    | Typ. † | Max.             | Unit | Condition |

|---------------|----------------------------|-------------------------|--------|------------------|------|-----------|

| $f_{SSCK}^*$  | Client SCK clock frequency | —                       | —      | $f_{CLK\_PER}/6$ | MHz  |           |

| $T_{SSCK}^*$  | Client SCK period          | $6 \times T_{CLK\_PER}$ | —      | —                | ns   |           |

| $t_{SSCKW}^*$ | SCK high/low width         | $3 \times T_{CLK\_PER}$ | —      | —                | ns   |           |

| $t_{SIS}^*$   | MOSI setup to SCK          | 0                       | —      | —                | ns   |           |

| $t_{SIH}^*$   | MOSI hold after SCK        | $3 \times T_{CLK\_PER}$ | —      | —                | ns   |           |

| $t_{SSS}^*$   | SS setup to SCK            | $T_{CLK\_PER}$          | —      | —                | ns   |           |

| $t_{SSH}^*$   | SS hold after SCK          | $T_{CLK\_PER}$          | —      | —                | ns   |           |

.....continued

| Symbol            | Description             | Min. | Typ. †          | Max. | Unit | Condition                                   |

|-------------------|-------------------------|------|-----------------|------|------|---------------------------------------------|

| t <sub>SOS</sub>  | MISO valid after SCK    | —    | t <sub>SR</sub> | —    | ns   | f <sub>SSCK</sub> ≥ f <sub>CLK_PER</sub> /6 |

|                   |                         |      | —               |      |      | f <sub>SSCK</sub> < f <sub>CLK_PER</sub> /6 |

| t <sub>SOSS</sub> | MISO setup after SS low | —    | t <sub>SR</sub> | —    | ns   |                                             |

| t <sub>SOSH</sub> | MISO hold after SS low  | —    | t <sub>SR</sub> | —    | ns   |                                             |

† Unless otherwise specified, data in the "Typ." column is at T<sub>A</sub> = 25°C and V<sub>DD</sub> = 3.0V. These parameters are not tested and are for design guidance only.

\* These parameters are characterized but not tested in production.

## 4. Document Revision History

**Note:** The document revision is independent of the silicon revision.

### 4.1 Revision History

| Doc. Rev. | Date    | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C         | 02/2024 | <ul style="list-style-type: none"> <li>Document: General editorial updates</li> <li>Added Silicon Revision: B0 <ul style="list-style-type: none"> <li>NVMCTRL: <a href="#">2.5.1. Flash Multi-Page Erase Can Erase Write Protected Section</a></li> <li>TCD: <a href="#">2.8.3. Halting TCD and Waiting for SW Restart Does Not Work if Compare Value A is 0 or Dual Slope Mode is Used</a></li> <li>TWI: <a href="#">2.9.1. Flush Non-Functional</a></li> </ul> </li> <li>Added Errata: <ul style="list-style-type: none"> <li>Device: <a href="#">2.2.2. Write Operation Lost if Consecutive Writes to Specific Address Spaces</a></li> <li>NVMCTRL: <a href="#">2.5.2. NVM_EEPROM_ERASE Command does Not Respect Write Protect</a></li> <li>USART: <a href="#">2.10.2. Receiver Non-Functional after Detection of Inconsistent Synchronization Field</a></li> </ul> </li> <li>Added Data Sheet Clarifications: <ul style="list-style-type: none"> <li>Device: <ul style="list-style-type: none"> <li><a href="#">3.1.1. Features</a></li> <li><a href="#">3.1.2. FUSE - Configuration and User Fuses - SYSCFG0</a></li> </ul> </li> <li>SPI: <ul style="list-style-type: none"> <li><a href="#">3.2.1. SPI - Serial Peripheral Interface</a></li> <li><a href="#">3.2.2. SPI - Serial Peripheral Interface</a></li> </ul> </li> <li>AC: <a href="#">3.3.1. Analog Comparator Interrupt Control</a></li> <li>DAC: <a href="#">3.4.1. DAC Output</a></li> <li>Electrical Characteristics: <ul style="list-style-type: none"> <li><a href="#">3.5.1. I/O Pin Characteristics</a></li> <li><a href="#">3.5.2. Electrical Characteristics - Memory Programming Specifications</a></li> <li><a href="#">3.5.3. Electrical Characteristics - SPI</a></li> </ul> </li> </ul> </li> </ul> |

| B         | 03/2022 | <ul style="list-style-type: none"> <li>Document: General editorial updates.</li> <li>Added Errata: <ul style="list-style-type: none"> <li>DAC: <a href="#">2.4.1. DAC Output Buffer Lifetime Drift</a></li> <li>NVMCTRL: <a href="#">2.5.1. Flash Multi-Page Erase Can Erase Write Protected Section</a></li> <li>TCD: <a href="#">2.8.3. Halting TCD and Waiting for SW Restart Does Not Work if Compare Value A is 0 or Dual Slope Mode is Used</a></li> <li>TWI: <a href="#">2.9.1. Flush Non-Functional</a></li> </ul> </li> <li>Added data sheet clarifications: <ul style="list-style-type: none"> <li>Device: <ul style="list-style-type: none"> <li>Features</li> <li>FUSE - Configuration and User Fuses - SYSCFG0</li> </ul> </li> <li>AC: Analog Comparator Interrupt Control</li> <li>DAC: DAC Output</li> <li>Electrical Characteristics: Memory Programming Specifications</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A         | 02/2021 | Initial document release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## Microchip Information

### The Microchip Website

Microchip provides online support via our website at [www.microchip.com/](http://www.microchip.com/). This website is used to make files and information easily available to customers. Some of the content available includes:

- **Product Support** – Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** – Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- **Business of Microchip** – Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### Product Change Notification Service

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to [www.microchip.com/pcn](http://www.microchip.com/pcn) and follow the registration instructions.

### Customer Support

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: [www.microchip.com/support](http://www.microchip.com/support)

### Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

### Legal Notice

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure

that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at [www.microchip.com/en-us/support/design-help/client-support-services](http://www.microchip.com/en-us/support/design-help/client-support-services).

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, IGaT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2024, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved.

ISBN: 978-1-6683-3866-7

## **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit

[www.microchip.com/quality](http://www.microchip.com/quality).

# Worldwide Sales and Service

| AMERICAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ASIA/PACIFIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ASIA/PACIFIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EUROPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Corporate Office</b><br>2355 West Chandler Blvd.<br>Chandler, AZ 85224-6199<br>Tel: 480-792-7200<br>Fax: 480-792-7277<br>Technical Support:<br><a href="http://www.microchip.com/support">www.microchip.com/support</a><br>Web Address:<br><a href="http://www.microchip.com">www.microchip.com</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>Australia - Sydney</b><br>Tel: 61-2-9868-6733<br><b>China - Beijing</b><br>Tel: 86-10-8569-7000<br><b>China - Chengdu</b><br>Tel: 86-28-8665-5511<br><b>China - Chongqing</b><br>Tel: 86-23-8980-9588<br><b>China - Dongguan</b><br>Tel: 86-769-8702-9880<br><b>China - Guangzhou</b><br>Tel: 86-20-8755-8029<br><b>China - Hangzhou</b><br>Tel: 86-571-8792-8115<br><b>China - Hong Kong SAR</b><br>Tel: 852-2943-5100<br><b>China - Nanjing</b><br>Tel: 86-25-8473-2460<br><b>China - Qingdao</b><br>Tel: 86-532-8502-7355<br><b>China - Shanghai</b><br>Tel: 86-21-3326-8000<br><b>China - Shenyang</b><br>Tel: 86-24-2334-2829<br><b>China - Shenzhen</b><br>Tel: 86-755-8864-2200<br><b>China - Suzhou</b><br>Tel: 86-186-6233-1526<br><b>China - Wuhan</b><br>Tel: 86-27-5980-5300<br><b>China - Xian</b><br>Tel: 86-29-8833-7252<br><b>China - Xiamen</b><br>Tel: 86-592-2388138<br><b>China - Zhuhai</b><br>Tel: 86-756-3210040 | <b>India - Bangalore</b><br>Tel: 91-80-3090-4444<br><b>India - New Delhi</b><br>Tel: 91-11-4160-8631<br><b>India - Pune</b><br>Tel: 91-20-4121-0141<br><b>Japan - Osaka</b><br>Tel: 81-6-6152-7160<br><b>Japan - Tokyo</b><br>Tel: 81-3-6880- 3770<br><b>Korea - Daegu</b><br>Tel: 82-53-744-4301<br><b>Korea - Seoul</b><br>Tel: 82-2-554-7200<br><b>Malaysia - Kuala Lumpur</b><br>Tel: 60-3-7651-7906<br><b>Malaysia - Penang</b><br>Tel: 60-4-227-8870<br><b>Philippines - Manila</b><br>Tel: 63-2-634-9065<br><b>Singapore</b><br>Tel: 65-6334-8870<br><b>Taiwan - Hsin Chu</b><br>Tel: 886-3-577-8366<br><b>Taiwan - Kaohsiung</b><br>Tel: 886-7-213-7830<br><b>Taiwan - Taipei</b><br>Tel: 886-2-2508-8600<br><b>Thailand - Bangkok</b><br>Tel: 66-2-694-1351<br><b>Vietnam - Ho Chi Minh</b><br>Tel: 84-28-5448-2100 | <b>Austria - Wels</b><br>Tel: 43-7242-2244-39<br>Fax: 43-7242-2244-393<br><b>Denmark - Copenhagen</b><br>Tel: 45-4485-5910<br>Fax: 45-4485-2829<br><b>Finland - Espoo</b><br>Tel: 358-9-4520-820<br><b>France - Paris</b><br>Tel: 33-1-69-53-63-20<br>Fax: 33-1-69-30-90-79<br><b>Germany - Garching</b><br>Tel: 49-8931-9700<br><b>Germany - Haan</b><br>Tel: 49-2129-3766400<br><b>Germany - Heilbronn</b><br>Tel: 49-7131-72400<br><b>Germany - Karlsruhe</b><br>Tel: 49-721-625370<br><b>Germany - Munich</b><br>Tel: 49-89-627-144-0<br>Fax: 49-89-627-144-44<br><b>Germany - Rosenheim</b><br>Tel: 49-8031-354-560<br><b>Israel - Ra'anana</b><br>Tel: 972-9-744-7705<br><b>Italy - Milan</b><br>Tel: 39-0331-742611<br>Fax: 39-0331-466781<br><b>Italy - Padova</b><br>Tel: 39-049-7625286<br><b>Netherlands - Drunen</b><br>Tel: 31-416-690399<br>Fax: 31-416-690340<br><b>Norway - Trondheim</b><br>Tel: 47-72884388<br><b>Poland - Warsaw</b><br>Tel: 48-22-3325737<br><b>Romania - Bucharest</b><br>Tel: 40-21-407-87-50<br><b>Spain - Madrid</b><br>Tel: 34-91-708-08-90<br>Fax: 34-91-708-08-91<br><b>Sweden - Gothenberg</b><br>Tel: 46-31-704-60-40<br><b>Sweden - Stockholm</b><br>Tel: 46-8-5090-4654<br><b>UK - Wokingham</b><br>Tel: 44-118-921-5800<br>Fax: 44-118-921-5820 |

| <b>Atlanta</b><br>Duluth, GA<br>Tel: 678-957-9614<br>Fax: 678-957-1455<br><b>Austin, TX</b><br>Tel: 512-257-3370<br><b>Boston</b><br>Westborough, MA<br>Tel: 774-760-0087<br>Fax: 774-760-0088<br><b>Chicago</b><br>Itasca, IL<br>Tel: 630-285-0071<br>Fax: 630-285-0075<br><b>Dallas</b><br>Addison, TX<br>Tel: 972-818-7423<br>Fax: 972-818-2924<br><b>Detroit</b><br>Novi, MI<br>Tel: 248-848-4000<br><b>Houston, TX</b><br>Tel: 281-894-5983<br><b>Indianapolis</b><br>Noblesville, IN<br>Tel: 317-773-8323<br>Fax: 317-773-5453<br>Tel: 317-536-2380<br><b>Los Angeles</b><br>Mission Viejo, CA<br>Tel: 949-462-9523<br>Fax: 949-462-9608<br>Tel: 951-273-7800<br><b>Raleigh, NC</b><br>Tel: 919-844-7510<br><b>New York, NY</b><br>Tel: 631-435-6000<br><b>San Jose, CA</b><br>Tel: 408-735-9110<br>Tel: 408-436-4270<br><b>Canada - Toronto</b><br>Tel: 905-695-1980<br>Fax: 905-695-2078 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |