## PRODUCT / PROCESS CHANGE NOTIFICATION

### 1. PCN basic data

|                      |                                                                                   |                                      |

|----------------------|-----------------------------------------------------------------------------------|--------------------------------------|

| 1.1 Company          |  | STMicroelectronics International N.V |

| 1.2 PCN No.          |                                                                                   | AMS/21/12801                         |

| 1.3 Title of PCN     |                                                                                   | Changes Notification on STGAP2S.     |

| 1.4 Product Category |                                                                                   | Motion Control&Automation            |

| 1.5 Issue date       |                                                                                   | 2021-06-07                           |

### 2. PCN Team

|                           |                          |

|---------------------------|--------------------------|

| 2.1 Contact supplier      |                          |

| 2.1.1 Name                | ROBERTSON HEATHER        |

| 2.1.2 Phone               | +1 8475853058            |

| 2.1.3 Email               | heather.robertson@st.com |

| 2.2 Change responsibility |                          |

| 2.2.1 Product Manager     | Domenico ARRIGO          |

| 2.1.2 Marketing Manager   | Fabio CHELLI             |

| 2.1.3 Quality Manager     | Alessandro PLATINI       |

### 3. Change

| 3.1 Category | 3.2 Type of change                                                                        | 3.3 Manufacturing Location        |

|--------------|-------------------------------------------------------------------------------------------|-----------------------------------|

| Transfer     | Product transfer from one site to another site, even if test or process line is qualified | ASSY plant: ASE<br>FT plant: MUAR |

### 4. Description of change

|                                                                                        | Old                                                                                               | New                                                                                      |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 4.1 Description                                                                        | IP FE ISOLATION: 1.7KV<br>ASSY plant: SHENZHEN (BOM 1F137576)<br>FT plant: AGRATE<br>DS version 1 | IP FE ISOLATION: 6KV<br>ASSY plant: ASE (BOM 1F142589)<br>FT plant: MUAR<br>DS version 2 |

| 4.2 Anticipated Impact on form, fit, function, quality, reliability or processability? | No Impact                                                                                         |                                                                                          |

### 5. Reason / motivation for change

|                      |                                                                                                                         |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|

| 5.1 Motivation       | The listed changes are qualified and implemented to guarantee the quality improvement of the impacted product: STGAP2S. |

| 5.2 Customer Benefit | QUALITY IMPROVEMENT                                                                                                     |

### 6. Marking of parts / traceability of change

|                 |         |

|-----------------|---------|

| 6.1 Description | New FGs |

|-----------------|---------|

### 7. Timing / schedule

|                                     |              |

|-------------------------------------|--------------|

| 7.1 Date of qualification results   | 2021-02-17   |

| 7.2 Intended start of delivery      | 2021-09-24   |

| 7.3 Qualification sample available? | Upon Request |

### 8. Qualification / Validation

|                                                    |                            |            |            |

|----------------------------------------------------|----------------------------|------------|------------|

| 8.1 Description                                    | 12801 RR002220CS6080_3.pdf |            |            |

| 8.2 Qualification report and qualification results | Available (see attachment) | Issue Date | 2021-06-07 |

**9. Attachments (additional documentations)**

12801 Public product.pdf

12801 RR002220CS6080\_3.pdf

**10. Affected parts**

| <b>10. 1 Current</b>           |                                | <b>10.2 New (if applicable)</b> |

|--------------------------------|--------------------------------|---------------------------------|

| <b>10.1.1 Customer Part No</b> | <b>10.1.2 Supplier Part No</b> | <b>10.1.2 Supplier Part No</b>  |

|                                | STGAP2SCM                      |                                 |

|                                | STGAP2SCMTR                    |                                 |

|                                | STGAP2SMTR                     |                                 |

**IMPORTANT NOTICE – PLEASE READ CAREFULLY**

Subject to any contractual arrangement in force with you or to any industry standard implemented by us, STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics – All rights reserved

## Public Products List

Public Products are off the shelf products. They are not dedicated to specific customers, they are available through ST Sales team, or Distributors, and visible on ST.com

**PCN Title :** Changes Notification on STGAP2S.

**PCN Reference :** AMS/21/12801

**Subject :** Public Products List

Dear Customer,

Please find below the Standard Public Products List impacted by the change.

|            |             |          |

|------------|-------------|----------|

| STGAP2SMTR | STGAP2SCMTR | STGAP2SM |

| STGAP2SCM  |             |          |

### **IMPORTANT NOTICE – PLEASE READ CAREFULLY**

Subject to any contractual arrangement in force with you or to any industry standard implemented by us, STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics – All rights reserved

# Reliability Evaluation Report

## RR002220CS6080

(New Product)

| General Information    |                                                  | Traceability    |                                     |

|------------------------|--------------------------------------------------|-----------------|-------------------------------------|

| Product Line           | : MY1D                                           | Diffusion Plant | : Catania (U1SD) +<br>Agrate (U1SF) |

| Product Description    | : Galvanically Isolated 4A single<br>gate driver | Assembly Plant  | : ASE CL                            |

| Reliability Assessment |                                                  |                 |                                     |

| Silicon Technology     | : U1SD (BCD6s) + U1SF (BCD6s)                    | Pass            | <input checked="" type="checkbox"/> |

|                        |                                                  | Fail            | <input type="checkbox"/>            |

**Note:** this report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the electronic device conformance to its specific mission profile. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics or under the approval of the author (see below).

| Version | Content description                           | Date        | Author              | Function             |

|---------|-----------------------------------------------|-------------|---------------------|----------------------|

| 1.0     | Initial Revision                              | 29-Jun-2020 | Gianfranco D'Angelo | Reliability Engineer |

| 1.1     | Update Test Plan and narrow<br>package option | 17-Feb-2021 | Gianfranco D'Angelo | Reliability Engineer |

### APPROVED BY:

| Function                     | Location | Name               |

|------------------------------|----------|--------------------|

| Division Reliability Manager | Italy    | Alceo Paratore     |

| Division Quality Manager     | Italy    | Alessandro Platini |

## TABLE OF CONTENTS

|                                                        |           |

|--------------------------------------------------------|-----------|

| <b>1 RELIABILITY EVALUATION OVERVIEW .....</b>         | <b>3</b>  |

| 1.1 OBJECTIVE .....                                    | 3         |

| 1.2 RELIABILITY STRATEGY.....                          | 3         |

| 1.3 CONCLUSION .....                                   | 4         |

| <b>2 PRODUCT OR TEST VEHICLE CHARACTERISTICS .....</b> | <b>5</b>  |

| 2.1 PRODUCT DESCRIPTION .....                          | 5         |

| 2.2 PIN CONNECTION .....                               | 6         |

| 2.3 BLOCK DIAGRAM .....                                | 7         |

| 2.4 BONDING DIAGRAM .....                              | 8         |

| 2.5 TRACEABILITY .....                                 | 9         |

| 2.5.1 <i>Wafer fab information.</i> .....              | 9         |

| 2.5.2 <i>Assembly information.</i> .....               | 10        |

| 2.5.3 <i>Reliability information.</i> .....            | 11        |

| <b>3 TESTS RESULTS SUMMARY .....</b>                   | <b>12</b> |

| 3.1 LOT INFORMATION .....                              | 12        |

| 3.2 TEST PLAN AND RESULTS SUMMARY.....                 | 13        |

| <b>4 APPLICABLE AND REFERENCE DOCUMENTS .....</b>      | <b>16</b> |

| <b>5 GLOSSARY .....</b>                                | <b>17</b> |

## 1 RELIABILITY EVALUATION OVERVIEW

### 1.1 Objective

This report contains the reliability evaluation of MY1D device diffused in Catania (U1SD) + Agrate (U1SF) and assembled in SO8W and SO8N in ASE CL.

### 1.2 Reliability Strategy

Reliability trials performed as part of this reliability evaluation are in agreement with **ST 0061692** specification and are listed in below Test Plan. For details on test conditions, generic data used and specifications references, refer to test results summary in section 3.

## 1.3 Conclusion

All reliability tests have been completed with positive results.

Based on the overall results obtained, MY1D product in Catania (U1SD) + Agrate (U1SF) and assembled in SO8W and SO8N in ASE CL, has positively passed reliability evaluation.

## 2 PRODUCT OR TEST VEHICLE CHARACTERISTICS

### 2.1 Product Description

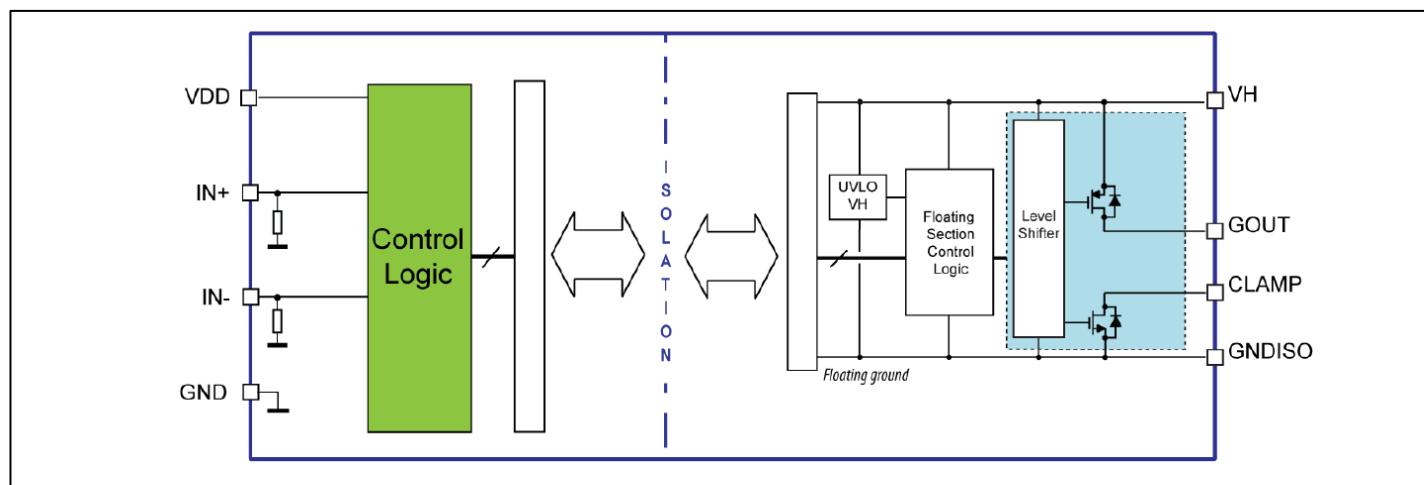

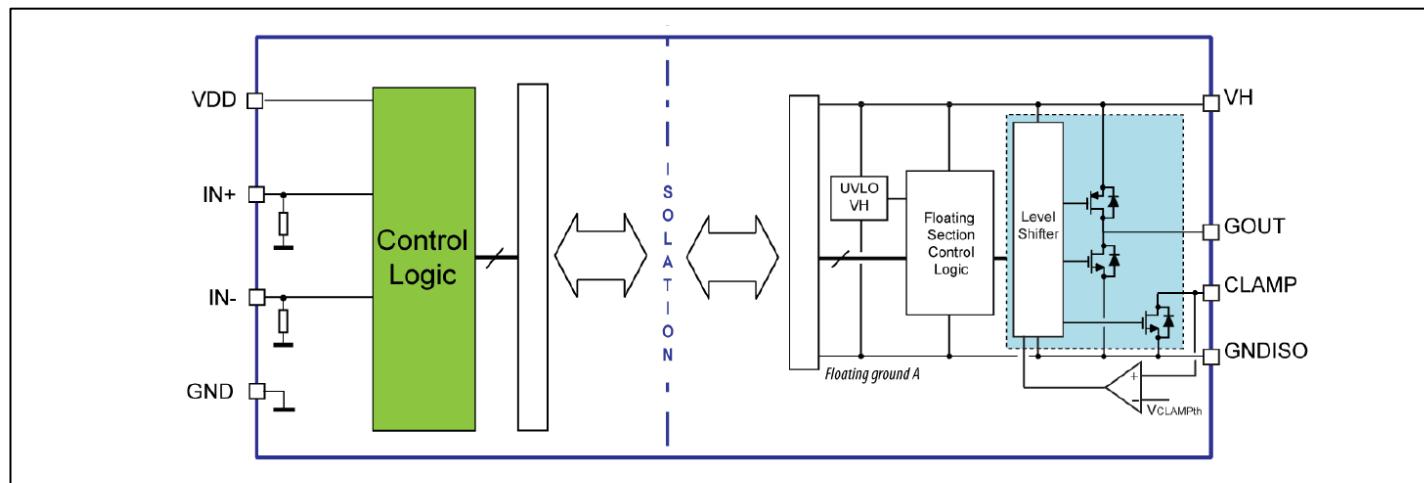

The MY1D device is a single gate driver which provides galvanic isolation between the gate driving channel and the low voltage control and interface circuitry.

The gate driver is characterized by 4A capability and rail-to-rail output, making the device also suitable for mid and high-power applications such as power conversion and motor driver inverters in industrial applications.

## 2.2 Pin connection

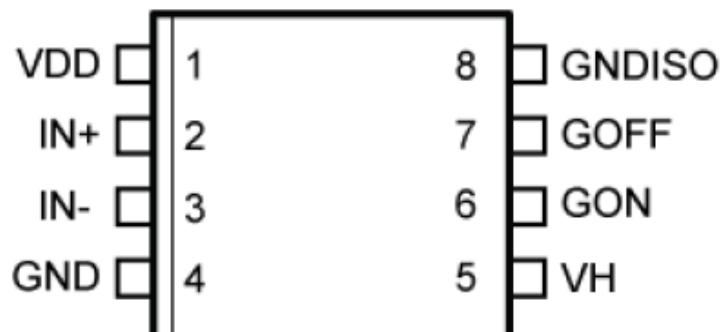

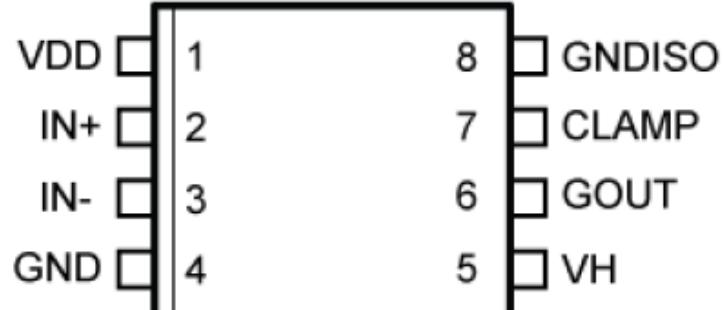

Figure 1. Pin connection with Separated Output option

Figure 2. Pin connection with Single Output and Miller CLAMP option

## 2.3 Block diagram

Figure 3. Block Diagram with Separate output

Figure 4. Block Diagram with Single Output and Miller Clamp

## 2.4 Bonding diagram

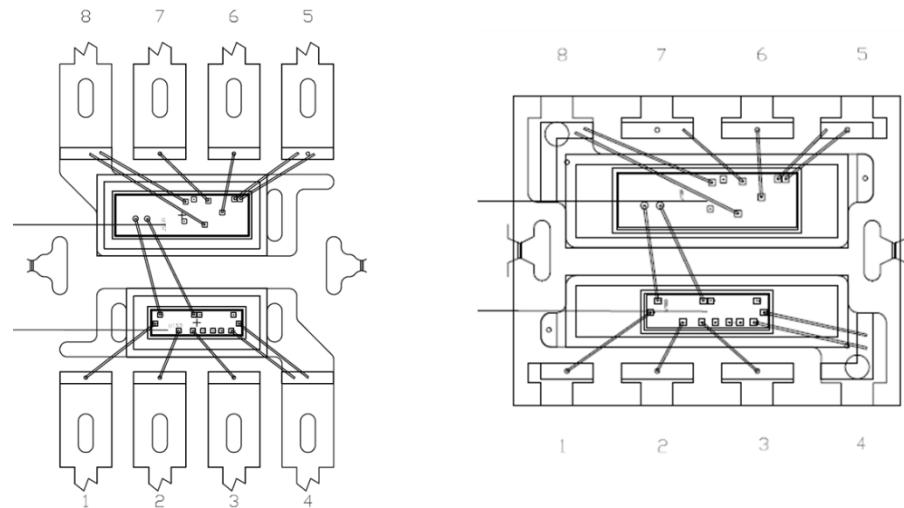

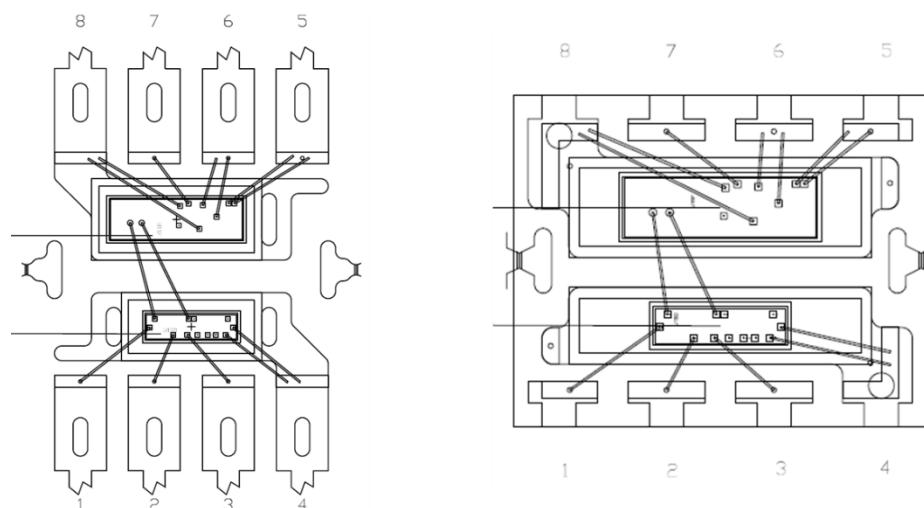

Figure 5. Bonding Diagram with Separate Output in package wide (left) and narrow (right)

Figure 6. Bonding Diagram with Single Output and Miller Clamp in package wide (left) and narrow (right)

## 2.5 Traceability

### 2.5.1 Wafer fab information

**Table 1**

| Wafer fab information ( U1SD )         |                        |

|----------------------------------------|------------------------|

| FAB1                                   |                        |

| Wafer fab location                     | Catania                |

| Wafer diameter (inches)                | 8 inches               |

| Die thickness (µm)                     | 280+/-20 UM            |

| Silicon process technology             | BCD6s                  |

| Die finishing front side (passivation) | TEOS/SiN/Polyimide     |

| Die finishing back side                | Cr/Ni/Au               |

| Die area (X,Y) (µm)                    | 1679,552 UM            |

| Metal levels                           | 3                      |

| Wafer fab information ( U1SF )         |                        |

| FAB1                                   |                        |

| Wafer fab location                     | Agrate                 |

| Wafer diameter (inches)                | 8 inches               |

| Die thickness (µm)                     | 280+/-20 UM            |

| Silicon process technology             | BCD6s                  |

| Die finishing front side (passivation) | SiN/TEOS/SiN/Polyimide |

| Die finishing back side                | Cr/NiV/Au              |

| Die area (X,Y) (µm)                    | 816,2393 UM            |

| Metal levels                           | 4                      |

## 2.5.2 Assembly information

**Table 2**

| Assembly Information            |              |

|---------------------------------|--------------|

| <b>Package 1 – SO8W – SO8N</b>  |              |

| Assembly plant location         | ASE CHUNG LI |

| Lead frame finishing (material) | Sn           |

| Die attach material             | EN4900G      |

| Wire bonding material/diameter  | Au 1.0 mils  |

| Molding compound material       | EME-G631H    |

### 2.5.3 Reliability information

**Table 3**

| <b>Reliability Information</b>         |                   |

|----------------------------------------|-------------------|

| Reliability laboratory name / location | Cornaredo (Italy) |

Note: ST is ISO 9001 certified. This induces certification of all internal and subcontractor labs.

ST certification document can be downloaded under the following link:

[http://www.st.com/content/st\\_com/en/support/quality-and-reliability/certifications.html](http://www.st.com/content/st_com/en/support/quality-and-reliability/certifications.html)

### 3 TESTS RESULTS SUMMARY

#### 3.1 Lot Information

**Table 4**

| Lot # | Diffusion Lots                     | Trace Code | Die Revision | Package       | Note                           |

|-------|------------------------------------|------------|--------------|---------------|--------------------------------|

| 1     | 5832X8K (U1SD)<br>A838461T01(U1SF) | AA008AJV   | ABA          | SO8 WIDE      | <i>Miller clamp option</i>     |

| 2     | 5832X8K (U1SD)<br>A838461T01(U1SF) | AA004ADU   | ABA          | SO8 WIDE      | <i>Miller clamp option</i>     |

| 3     | 5832X8K (U1SD)<br>A838461T01(U1SF) | AA008AJV   | ABA          | SO8 WIDE      | <i>Miller clamp option</i>     |

| 4     | 5832X8K (U1SD)<br>A930425 (U1SF)   | AA037ADS   | ACA          | SO8<br>NARROW | <i>Miller clamp option</i>     |

| 5     | 5832X8K (U1SD)<br>A930425 (U1SF)   | AA037ADS   | ACA          | SO8<br>NARROW | <i>Miller clamp option</i>     |

| 6     | 5832X8K (U1SD)<br>A930425 (U1SF)   | AA037ADS   | ACA          | SO8<br>NARROW | <i>Miller clamp option</i>     |

| 7     | 5832X8K (U1SD)<br>A930425 (U1SF)   | AA022AEA   | ACA          | SO8<br>NARROW | <i>Separated Output option</i> |

### 3.2 Test plan and results summary

**Table 5 – ACCELERATED LIFETIME SIMULATION TESTS**

| Test code | Stress method | Stress Conditions                                                                                                                                                                                                                | Lots | S.S. | Total | Results/ Lot Fail/S.S.          | Comments: (N/A =Not Applicable) |

|-----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|---------------------------------|---------------------------------|

| HTOL      | JESD22 A108   | TJ=150°C<br>VH=26V, VDD=5.5V,<br>GNDISO=1700V<br><br>Duration= 1000hrs<br><br><input checked="" type="checkbox"/> After PC<br><input type="checkbox"/> Assy on Chip Board<br><input checked="" type="checkbox"/> Testing at Room | 2    | 77   | 154   | Lot 1: 0 / 77<br>Lot 5 : 0 / 77 | -                               |

All samples (excluded samples on chipboard) have been submitted at Partial Discharge (Method B) test at ATE before and after reliability stress test with positive results

Table 6 – ACCELERATED ENVIRONMENT STRESS TESTS

| Test code | Stress method | Stress Conditions                                                                                                                                                                                                                                                                                                        | Lots | S.S. | Total | Results/ Lot<br>Fail/S.S.                                                                                | Comments:<br>(N/A =Not Applicable)                       |

|-----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| PC        | J-STD-020     | 24h bake@125°C,<br>MSL3 (192h@30C/60%RH)<br>3x Reflow simulation<br>Peak Reflow Temp= 260°C                                                                                                                                                                                                                              | 6    | -    | 833   | Lot 1: 0 / 211<br>Lot 2: 0 / 115<br>Lot 3: 3 / 115<br>Lot 4: 0 / 135<br>Lot 5: 0 / 122<br>Lot 6: 0 / 135 | -                                                        |

| THB       | JESD22 A101   | Ta=85°C, 85%RH,<br>VH=26V, VDD=5.5V,<br>GNDISO=0V (1)<br>Duration= 1000hrs<br><br>Ta=85°C, 85%RH<br>VH=26V, VDD=5.5V,<br>GNDISO=1500V (2)<br>Duration= 1000hrs<br><br><input checked="" type="checkbox"/> After PC<br><input type="checkbox"/> Assy on Chip Board<br><input checked="" type="checkbox"/> Testing at Room | 6    | 25   | 150   | Lot 1: 0/25<br>Lot 2: 0/25<br>Lot 3: 0/25<br>Lot 4: 0/25<br>Lot 5: 0/25<br>Lot 6: 0/25                   | (1) only wide package option<br>(2) both package options |

| TC        | JESD22-A104   | Ta= -55°C to + 150°C<br>Duration= 1000cyc<br><br><input checked="" type="checkbox"/> After PC<br><input checked="" type="checkbox"/> Testing at Room                                                                                                                                                                     | 5    | 25   | 125   | Lot 1: 0/25<br>Lot 2: 0/25<br>Lot 3: 0/25<br>Lot 4: 0/45<br>Lot 6: 0/45                                  | -                                                        |

| uHAST     | JESD22-A118   | Ta=130°C, RH=85%<br>Duration = 96hrs<br><br><input checked="" type="checkbox"/> After PC<br><input checked="" type="checkbox"/> Testing at Room                                                                                                                                                                          | 3    | 25   | 75    | Lot 1: 0/25<br>Lot 2: 0/25<br>Lot 3: 0/25                                                                | -                                                        |

| AC        | JESD22 A102   | P=2.08atm Ta=121°C,<br>Duration = 96hrs<br><br><input checked="" type="checkbox"/> After PC<br><input checked="" type="checkbox"/> Testing at Room                                                                                                                                                                       | 2    | 25   | 50    | Lot 4: 0/45<br>Lot 6: 0/45                                                                               | -                                                        |

| HTSL      | JESD22 A103   | Ta= 150°C<br>Duration= 1000hrs<br><br><input type="checkbox"/> After PC<br><input checked="" type="checkbox"/> Testing at Room                                                                                                                                                                                           | 5    | 25   | 125   | Lot 1: 0/25<br>Lot 2: 0/25<br>Lot 3: 0/25<br>Lot 4: 0/45<br>Lot 6: 0/45                                  | -                                                        |

All samples (excluded samples on chipboard) have been submitted at Partial Discharge (Method B) test at ATE before and after reliability stress test with positive results

**Table 7 – ELECTRICAL VERIFICATION TESTS**

| Test code | Stress method         | Stress Conditions                                                                                                                                                                               | Lots | S.S. | Total | Results Fail/S.S.            | Comments: (N/A =Not Applicable) |

|-----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------------|---------------------------------|

| HBM       | ANSI/ESDA/JEDEC JS001 | HBM=+/-2kV<br><input checked="" type="checkbox"/> Testing at Room                                                                                                                               | 1    | 3    | 3     | Lot 1: 0 / 3                 |                                 |

| CDM       | ANSI/ESDA/JEDEC JS001 | CDM=+/-750V on corner pins; +/-500V all others<br><input checked="" type="checkbox"/> Testing at Room                                                                                           | 2    | 3    | 6     | Lot 1: 0 / 3<br>Lot 4: 0 / 3 |                                 |

| LU        | JESD78                | Current Injection<br>Class II - Level A (+/- 100mA)<br><br>Overvoltage<br>Class II - Level A (1,5 x Vmax)<br><br>T <sub>dut</sub> =125°C<br><input checked="" type="checkbox"/> Testing at Room | 2    | 6    | 12    | Lot 1: 0 / 6<br>Lot 7: 0 / 6 |                                 |

Note: Test method revision reference is the one active at the date of reliability trial execution.

## 4 APPLICABLE AND REFERENCE DOCUMENTS

| Reference   | Short description                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------|

| AEC-Q100    | Failure Mechanism Based Stress Test Qualification for Integrated Circuits in automotive applications |

| JESD47      | Stress-Test-Driven Qualification of Integrated Circuits                                              |

| DMS 0061692 | Reliability Tests and Criteria for Product Qualification                                             |

## 5 GLOSSARY

*List update based on applicable items.*

|         |                                                          |

|---------|----------------------------------------------------------|

| AC      | Autoclave                                                |

| ACBV    | AC Blocking Voltage                                      |

| ASER    | Accelerated Soft Error Rate                              |

| AST     | Adhesion Shear Test                                      |

| BI      | Burn-In                                                  |

| BT3P    | Board 3 points Bending Test                              |

| BT4P    | Board 4 points Bending Test                              |

| CA      | Constant Acceleration                                    |

| CDM     | Electrostatic Discharge - Charged Device Model           |

| ConA    | Construction Analysis                                    |

| CVS     | Constant Voltage Stress                                  |

| DBT     | Dead Bug Test                                            |

| DPA     | Destructive Physical Analysis                            |

| DROP    | Package drop                                             |

| DS      | Die Shear                                                |

| DTb     | Drop Test on Board                                       |

| EDR     | NVM Program/Erase Endurance & Data Retention Stress Test |

| ELFR    | Early Life Failure Rate                                  |

| EMC     | Electromagnetic Compatibility                            |

| EOS     | Electrical Overstress characterization                   |

| ESeq    | Environmental sequence                                   |

| EV      | External Visual                                          |

| GFF     |                                                          |

| GFL     | Gross/Fine Leak                                          |

| GL      | Electro-thermally Induced Gate Leakage                   |

| GStress | Gate Stress                                              |

| GUN     | Electrostatic Discharge - System Level Test              |

| H3TRB   | High Humidity High Temperature Reverse Bias              |

| HAST    | Biased HAST (Highly Accelerated Stress Test)             |

| HBM     | Electrostatic Discharge - Human Body Model               |

| HER     | Hermeticity                                              |

| HMM     | Electrostatic Discharge - Human Metal Model              |

| HTFB    | High Temperature Forward Bias                            |

| HTGB    | High Temperature Gate Bias                               |

| HTHHB   | High Temperature High Humidity Bias                      |

| HTOL    | High Temperature Operating Life                          |

| HTRB    | High Temperature Reverse Bias.                           |

| HTSL    | High Temperature Storage Life                            |

| IOL     | Intermittent Operating Life                              |

| IWV     | Internal Water Vapor                                     |

| LF      | Lead Free                                                |

| LI      | Lead Integrity                                           |

| LT      | Lid Torque                                               |

| LTOL    | Low Temperature Operating Life                           |

| LTSI    | Low Temperature Storage Life                             |

| LU      | Latch-Up                                                 |

| MM      | Electrostatic Discharge - Machine model                  |

|        |                                                   |

|--------|---------------------------------------------------|

| MR     | Multiple Reflow                                   |

| MS     | Mechanical Shock                                  |

| MSeq   | Mechanical sequence                               |

| MSL    | Moisture Sensitivity Level                        |

| NVM    | Non Volatile Memory                               |

| PC     | Preconditioning                                   |

| PD     | Physical Dimensions                               |

| PTC    | Power Temperature Cycling                         |

| RS     | Repetitive Surge Test                             |

| TSH    | Resistance to Solder Heat                         |

| RTSER  | Real-Time Soft Error Rate                         |

| SAM    | Scanning Acoustic Microscopy                      |

| SBP    | Solder Ball Pull                                  |

| SBS    | Solder Ball Shear                                 |

| SC     | Short Circuit Characterization                    |

| SCCSS  | Smartcard - Constant Supply Stress                |

| SCMCMs | Smartcard - MasterCard Mechanical Stress          |

| SCMF   | Smartcard - Magnetic Field Stress                 |

| SCPOOS | Smartcard - Power Off/On Stress                   |

| SCRFC  | Smartcard - RF On/Off Cyclic Stress               |

| SCRFS  | Smartcard - RF On Static Stress                   |

| ScrT   | Screw Test                                        |

| SCSA   | Smartcard - Salt Atmosphere                       |

| SCUV   | Smartcard - UV Test                               |

| SCXRAY | Smartcard - XRAY Test                             |

| SD     | Solderability                                     |

| SSOP   | Steady State Operational                          |

| STb    | Shock Test on Board                               |

| TC     | Temperature Cycling                               |

| TCDT   | Temperature Cycling Delamination Test             |

| TCHT   | Temperature Cycling Hot Test                      |

| TCoB   | Temperature Cycling on Board                      |

| THB    | Temperature Humidity Bias                         |

| THS    | Temperature Humidity Storage                      |

| TLp    | Electrostatic Discharge - Transmission Line Pulse |

| TS     | Thermal Shocks                                    |

| TStr   | Terminal Strength                                 |

| Tumb   | Tumbler Test                                      |

| UHAST  | Unbiased HAST (Highly Accelerated Stress Test)    |

| VToB   | Vibration Test on Board                           |

| VFV    | Variable Frequency Vibration                      |

| WAT    | Tin (Sn) Whisker Acceptance Testing               |

| WBI    | Wire Bond Integrity                               |

| WBP    | Wire Bond Pull                                    |

| WBS    | Wire Bond Shear                                   |

| WBSt   | Wire Bond Strength                                |

| XRAY   | X ray inspection                                  |

## **CONFIDENTIALITY OBLIGATIONS**

This document contains confidential information; its distribution is submitted to ST authorization.

Disclosure of this document to any non-authorized party must be previously authorized by ST only under the provision of a signed NDA between ST and Customer and must be treat as strictly confidential.

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

Information in this document is intended as support for authorized communication between ST and Customer only, for internal discussions purposes.

In no event the information disclosed by ST to Customer hereunder can be used against ST, or in a claim brought in front of any Court or Jurisdiction.

At all times you will comply with the following securities rules:

- Do not copy or reproduce all or part of this document

- Keep this document locked away

- Further copies can be provided on a "need to know basis", Please contact your local ST Sales Office or document writer

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a trademark of STMicroelectronics International NV and/or its affiliates, registered in the U.S. and other countries

© 2018 STMicroelectronics International NV and/or its affiliates – All Rights Reserved

[www.st.com](http://www.st.com)