## PRODUCT / PROCESS CHANGE INFORMATION

### 1. PCI basic data

|                      |                                                                                                                        |

|----------------------|------------------------------------------------------------------------------------------------------------------------|

| 1.1 Company          |  STMicroelectronics International N.V |

| 1.2 PCI No.          | ADG/22/13726                                                                                                           |

| 1.3 Title of PCI     | L9026 (UR5V): Datasheet update                                                                                         |

| 1.4 Product Category | L9026-B03N-TR, L9026-YO-TR                                                                                             |

| 1.5 Issue date       | 2022-12-21                                                                                                             |

### 2. PCI Team

|                           |                          |

|---------------------------|--------------------------|

| 2.1 Contact supplier      |                          |

| 2.1.1 Name                | ROBERTSON HEATHER        |

| 2.1.2 Phone               | +1 8475853058            |

| 2.1.3 Email               | heather.robertson@st.com |

| 2.2 Change responsibility |                          |

| 2.2.1 Product Manager     | Maurizio GALLINARI       |

| 2.2.2 Marketing Manager   | Aldo OCCHIPINTI          |

| 2.2.3 Quality Manager     | Marcello Donato MENCHISE |

### 3. Change

| 3.1 Category             | 3.2 Type of change                           | 3.3 Manufacturing Location |

|--------------------------|----------------------------------------------|----------------------------|

| General Product & Design | Modification of datasheet : Errata/error fix | NA                         |

### 4. Description of change

|                                                                                       | Old        | New        |

|---------------------------------------------------------------------------------------|------------|------------|

| 4.1 Description                                                                       | Revision 6 | Revision 7 |

| 4.2 Anticipated Impact on form,fit, function, quality, reliability or processability? | No Impact  |            |

### 5. Reason / motivation for change

|                      |                    |

|----------------------|--------------------|

| 5.1 Motivation       | Typo correction    |

| 5.2 Customer Benefit | SERVICE CONTINUITY |

### 6. Marking of parts / traceability of change

|                 |                                                                   |

|-----------------|-------------------------------------------------------------------|

| 6.1 Description | Datasheet available on <a href="http://www.st.com">www.st.com</a> |

|-----------------|-------------------------------------------------------------------|

### 7. Timing / schedule

|                                     |                |

|-------------------------------------|----------------|

| 7.1 Date of qualification results   | 2022-10-19     |

| 7.2 Intended start of delivery      | 2022-11-30     |

| 7.3 Qualification sample available? | Not Applicable |

### 8. Qualification / Validation

|                                                    |                            |            |

|----------------------------------------------------|----------------------------|------------|

| 8.1 Description                                    | 13726 DS_L9026_rev7.pdf    |            |

| 8.2 Qualification report and qualification results | Available (see attachment) | Issue Date |

### 9. Attachments (additional documentations)

|                                                                          |

|--------------------------------------------------------------------------|

| 13726 Public product.pdf<br>13726 DS_L9026_rev7.pdf<br>13726 Details.pdf |

|--------------------------------------------------------------------------|

| 10. Affected parts      |                         |                          |

|-------------------------|-------------------------|--------------------------|

| 10. 1 Current           |                         | 10.2 New (if applicable) |

| 10.1.1 Customer Part No | 10.1.2 Supplier Part No | 10.1.2 Supplier Part No  |

|                         | L9026-YO-TR             |                          |

**IMPORTANT NOTICE – PLEASE READ CAREFULLY**

Subject to any contractual arrangement in force with you or to any industry standard implemented by us, STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics – All rights reserved

## PRODUCT/PROCESS CHANGE INFORMATION

|                           |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| <b>TITLE</b>              | <b>L9026 (UR5V): Datasheets Update</b>                                                |

| <b>IMPACTED PRODUCTS</b>  | <ul style="list-style-type: none"><li>- L9026-B03N-TR</li><li>- L9026-YO-TR</li></ul> |

| <b>CHANGE TYPE</b>        | Datasheet Update                                                                      |

| <b>CHANGE REASON</b>      | Service Continuity                                                                    |

| <b>CHANGE DESCRIPTION</b> | <p>Typo correction.</p> <p>Details available on revision history of the document</p>  |

| <b>REPORT</b>             | L9026 - DS13397 - Rev 7 - October 2022                                                |

## Automotive configurable multi-channel relay driver 2HS + 6HS/LS

### Features

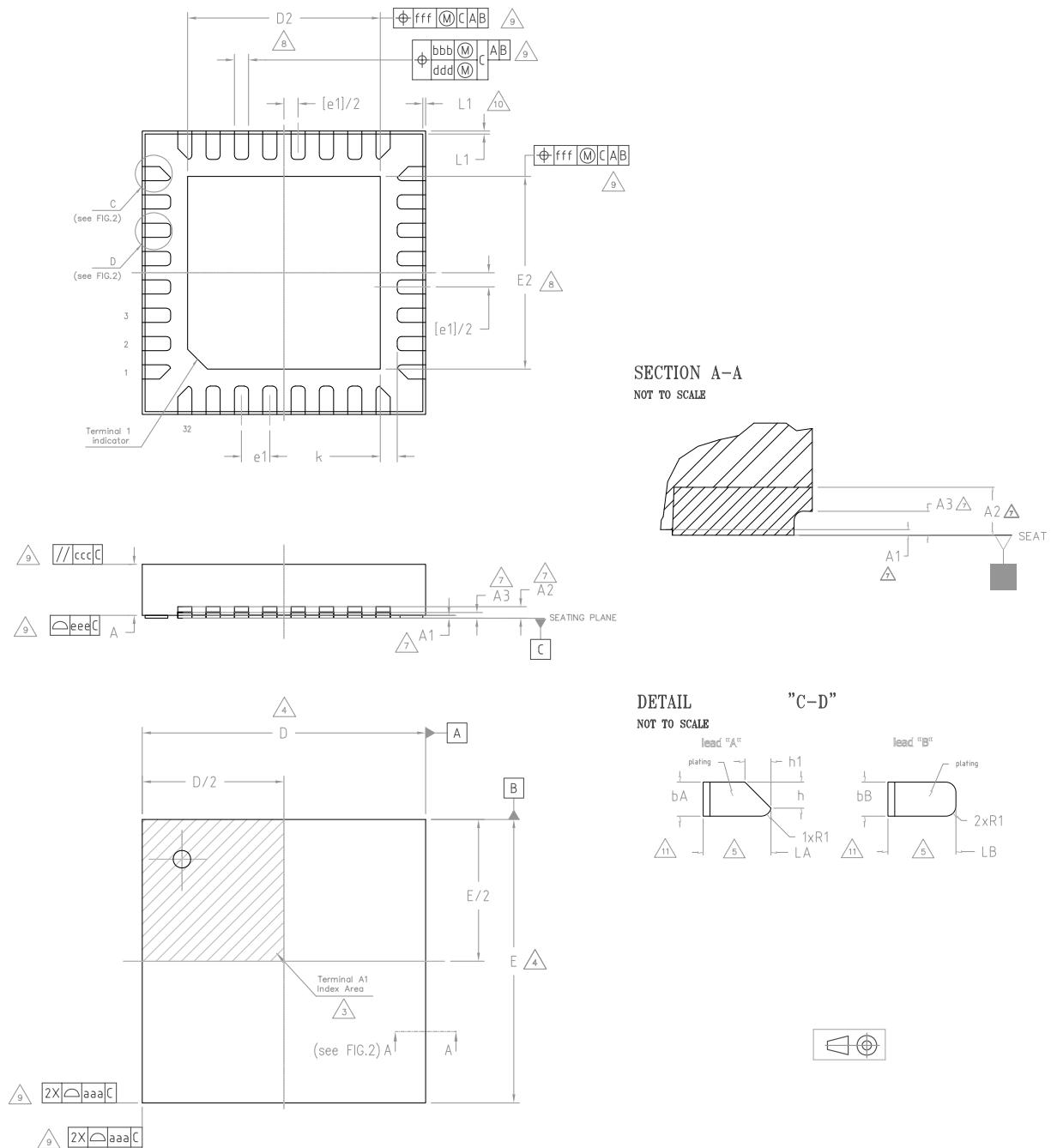

VFQFPN32 exposed pad down

(5x5x1 mm)

HTSSOP24 exposed pad down

(7.8x6.4x1 mm)

- AEC-Q100 qualified

- Six Configurable LS/HS drivers

- Two High Side drivers

- 2 parallel input pins with Input Mapping functionality

- Cranking capability down to VBATT = 3 V

- Digital supply voltage compatible with 3.3 V and 5 V microcontroller

- Reverse battery protection on VBATT and on drain pins without external components

- Bulb Inrush Mode (BIM) to drive lamps and electronic loads

- 2 Internal PWM Generator for microcontroller offload

- Very low quiescent current (with usage of IDLE pin)

- Limp Home mode (with usage of IDLE and IN pins)

- Green Product (RoHS compliant)

- Safety features

- Temperature Sensor and Monitoring

- Serial communications using address feedback, 1 parity bit, frame counter & short frame detection

- 16-bit serial peripheral interface for control and diagnosis

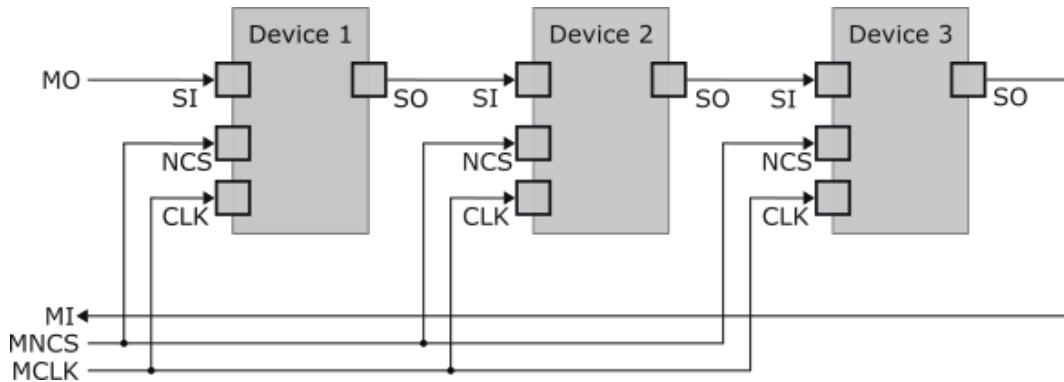

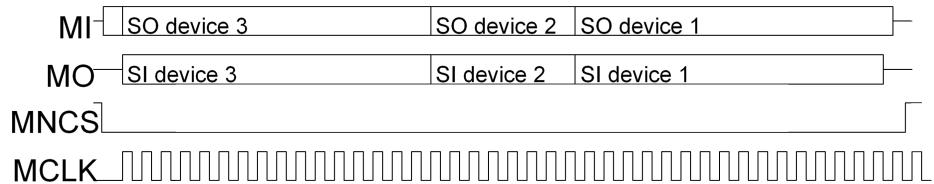

- Daisy Chain capability SPI, also compatible with 8-bit SPI devices

- Package options: HTSSOP24, VFQFPN32

- Full ISO26262 compliant, ASIL-B systems ready

#### Product status link

[L9026](#)

#### Product summary

|            |               |

|------------|---------------|

| Order code | L9026-B03N-TR |

| Package    | VFQFPN32      |

| Packing    | Tape & Reel   |

| Order code | L9026-Y0-TR   |

| Package    | HTSSOP24      |

| Packing    | Tape & Reel   |

### Description

The L9026 is an eight-channel IC, with 2 fixed HS drivers and 6 configurable HS/LS drivers designed for Automotive applications (LEDs and Relays) and compatible with resistive, inductive and capacitive loads. The device offers advanced diagnostic and protection functionalities such as: short to GND, open load, overcurrent, over-temperature detections. The 8 output channels can be either driven by SPI or by 2 dedicated parallel inputs. Limp home functionality is also featured, which allows using 2 selected drivers in particularly faulty conditions, such as SPI fault, micro fault or supply UV. Daisy chain compatible even with 8bit SPI is available. The device is able to guarantee operations under cranking scenario down to VBATT = 3 V and guarantees very low quiescent current under RESET condition.

A serial peripheral interface (SPI) is used for control and configuration of the loads as well as of the device; besides, status feedback of all diagnostic functions is provided. For direct control and PWM there are two input pins available: these are connected to two defined outputs by default, but additional or different output mapping can be controlled by SPI.

The device is available in two package versions: HTSSOP24 and VFQFPN32. Only for the QFN package 2 additional pins are available for safety reasons. In details, the NRES pin is used to reset internal registers to their default values and the DIS pin is used to disable all channels.

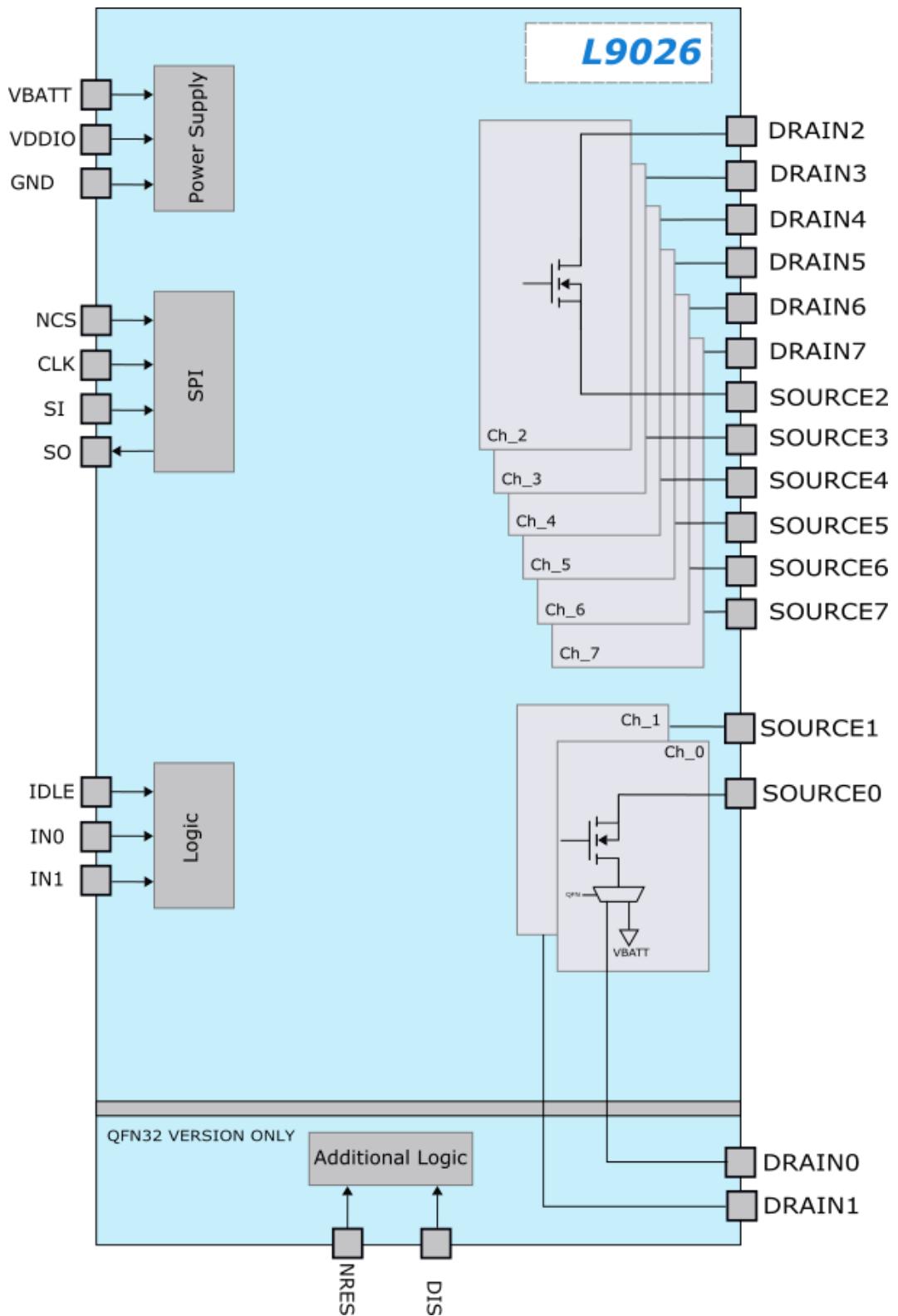

## 1 Block diagram

Figure 1. Block diagram

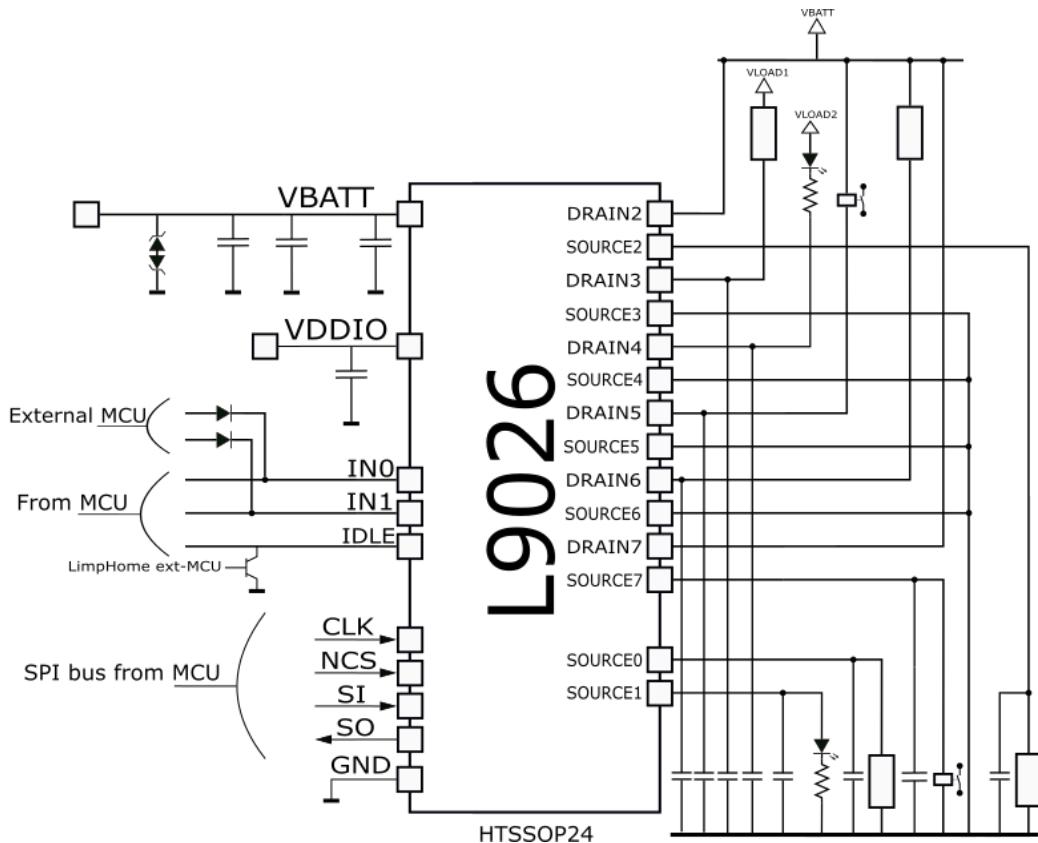

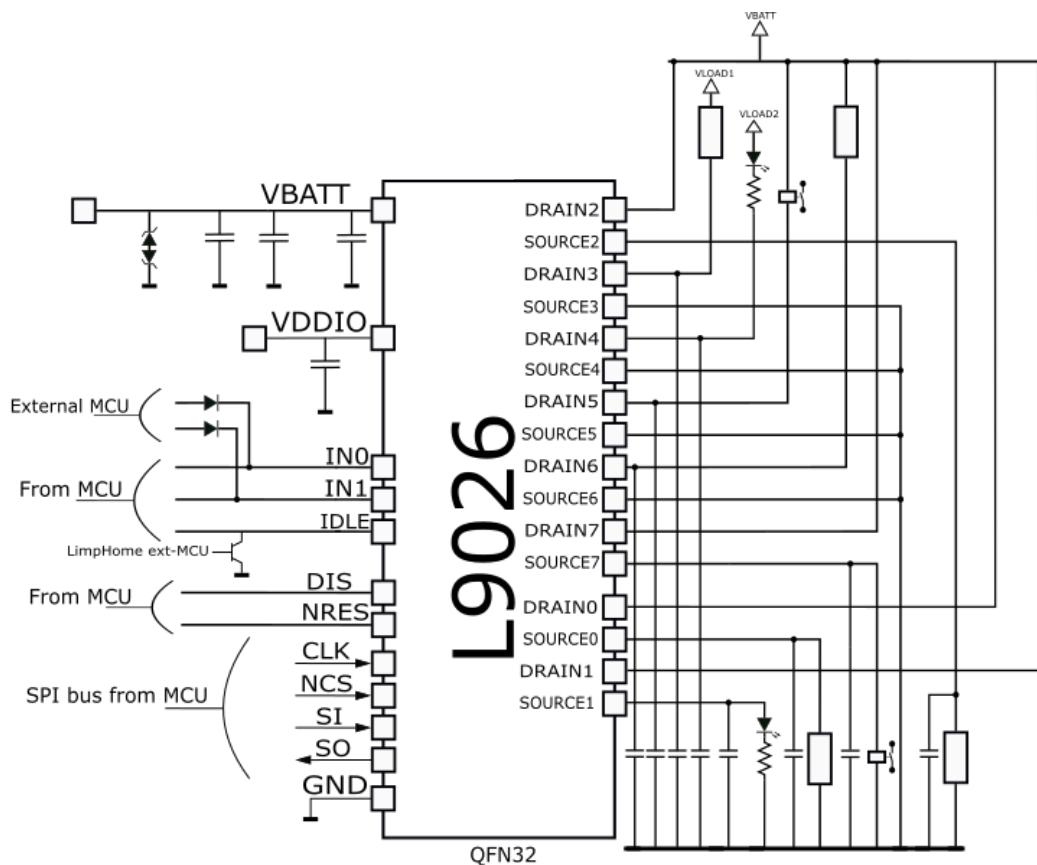

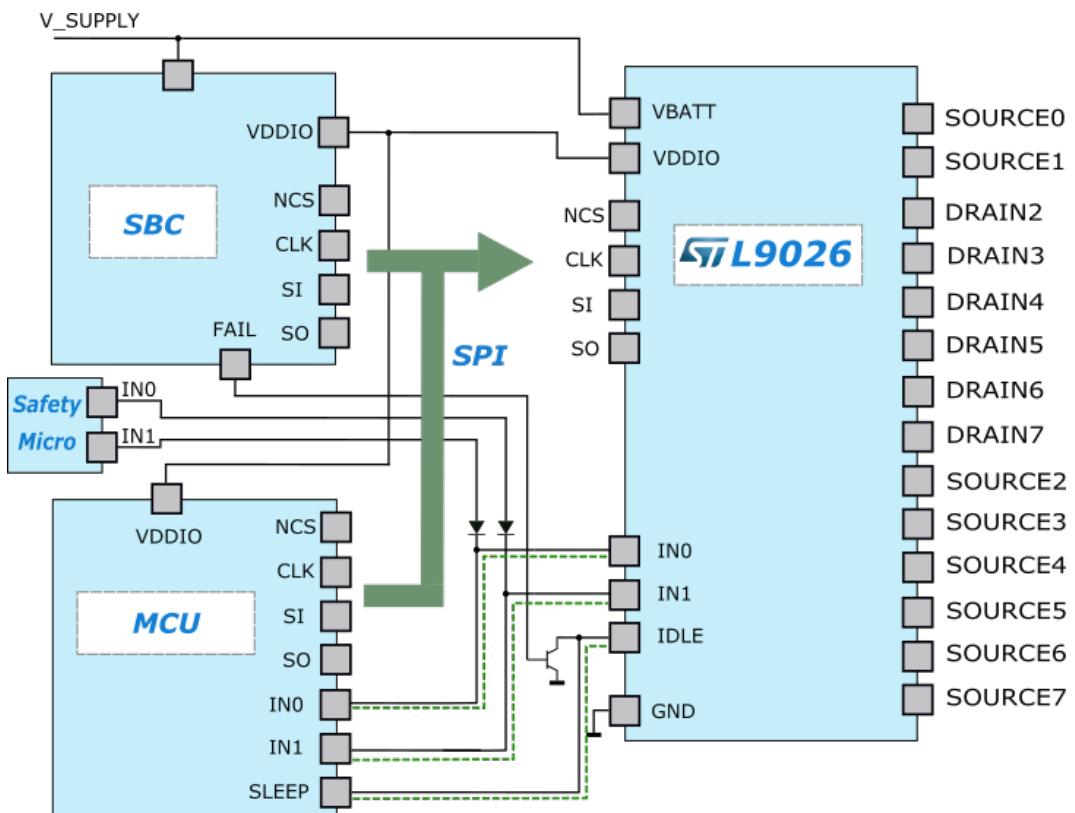

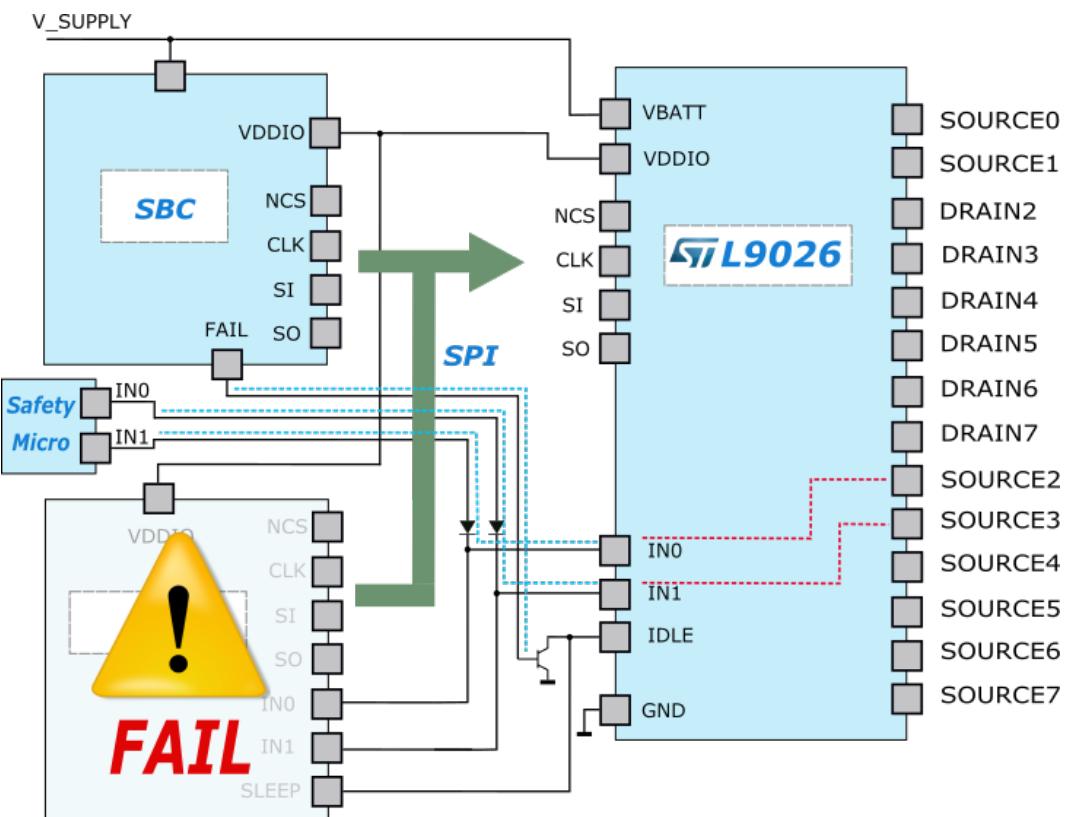

## 2 Application circuit

Here below two general application circuits:

- [Figure 2](#) reports L9026 with the HTSSOP24 version package

- [Figure 3](#) shows the application of L9026 with the VFQFPN32 version package

In the list of external components, the different parts are marked following the items reported below:

1. mandatory components for L9026 functionality

2. recommended components for EMC robustness

3. recommended components for ESD trials

4. recommended System component

**Note:** *recommended components may depend on the requirements at system levels and shall be confirmed by specific tests on the final application.*

**Figure 2. HTSSOP24 Application schematic**

Figure 3. VFQFPN32 Application schematic

Table 1. External components list for L9026 application circuit

| Pin             | External components |     |     |     |         | Requirement | Comment                                                                                                          |

|-----------------|---------------------|-----|-----|-----|---------|-------------|------------------------------------------------------------------------------------------------------------------|

|                 | Type                | Min | Typ | Max | Unit    |             |                                                                                                                  |

| VBATT           | Capacitor           | -   | 120 | -   | nF      | (2), (3)    | Tolerance $\pm 20\%$ 50 V                                                                                        |

|                 | Capacitor           | -   | 100 | -   | $\mu$ F | (2)         | 50 V, Transient and load dump protection                                                                         |

|                 | TVS                 | -15 | -   | 38  | V       | (4)         | Transient voltage suppressor                                                                                     |

|                 | Capacitor           | -   | 10  | -   | $\mu$ F | (2), (3)    | Tolerance $\pm 20\%$<br>50 V, Transient and load dump protection                                                 |

| VDDIO           | Capacitor           | -   | 100 | -   | nF      | (2)         | Tolerance $\pm 10\%$ 50 V                                                                                        |

| DRAIN2 DRAIN7   | Capacitor           | -   | -   | 12  | nF      | (3)         | Maximum total capacitance value at output load<br>(channel configured as low side)                               |

| DRAIN0 DRAIN7   |                     | 47  | -   | -   |         | (4)         | Minimum capacitance value at load supply (channel<br>configured as high side, DRAIN0 and DRAIN1 if<br>available) |

| SOURCE0 SOURCE7 | Capacitor           | -   | -   | 12  | nF      | (3)         | Maximum total capacitance value as output load<br>(channel configured as high side)                              |

3 Pins description

**Figure 4. HTSSOP-24 pinout diagram**

| positive      | negative | pin name |    | pin name | negative | positive |

|---------------|----------|----------|----|----------|----------|----------|

| 42V           | -0.3 V   | VBATT    | 1  |          |          |          |

| VOUT_D + 0.3V | -16 V    | SOURCE0  | 2  |          |          |          |

| 42V           | -0.3 V   | DRAIN7   | 3  |          |          |          |

| VOUT_D + 0.3V | -16 V    | SOURCE7  | 4  |          |          |          |

| 42V           | -0.3 V   | DRAIN6   | 5  |          |          |          |

| VOUT_D + 0.3V | -16 V    | SOURCE6  | 6  |          |          |          |

| 42V           | -0.3 V   | DRAIN5   | 7  |          |          |          |

| VOUT_D + 0.3V | -16 V    | SOURCE5  | 8  |          |          |          |

| VDDIO + 0.3   | -0.3 V   | IN1      | 9  |          |          |          |

| 20V           | -0.3 V   | IN0      | 10 |          |          |          |

| 0.3 V         | -0.3 V   | GND      | 11 |          |          |          |

| 20V           | -0.3 V   | IDLE     | 12 |          |          |          |

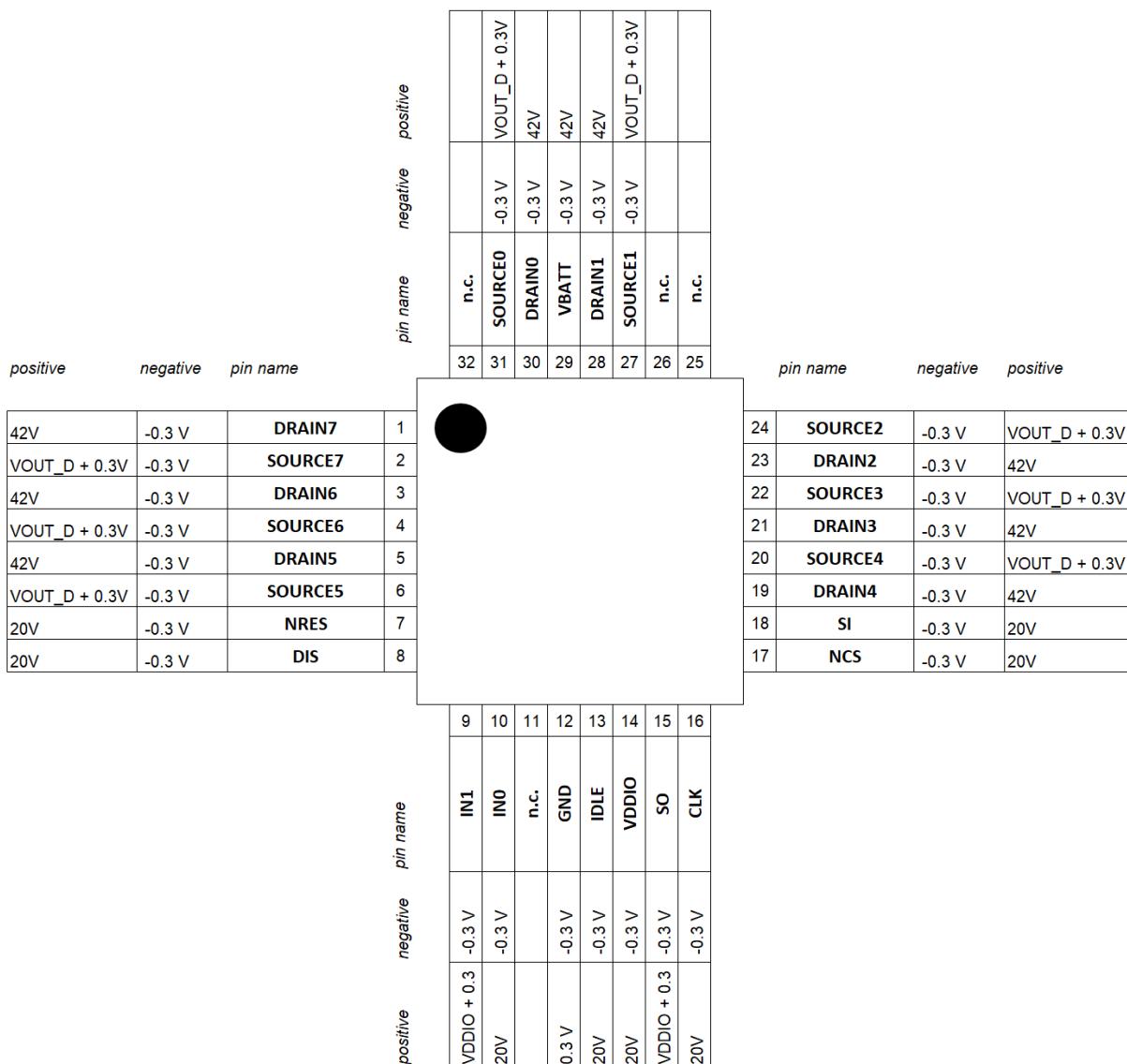

**Figure 5. VFQFPN32 pinout diagram**

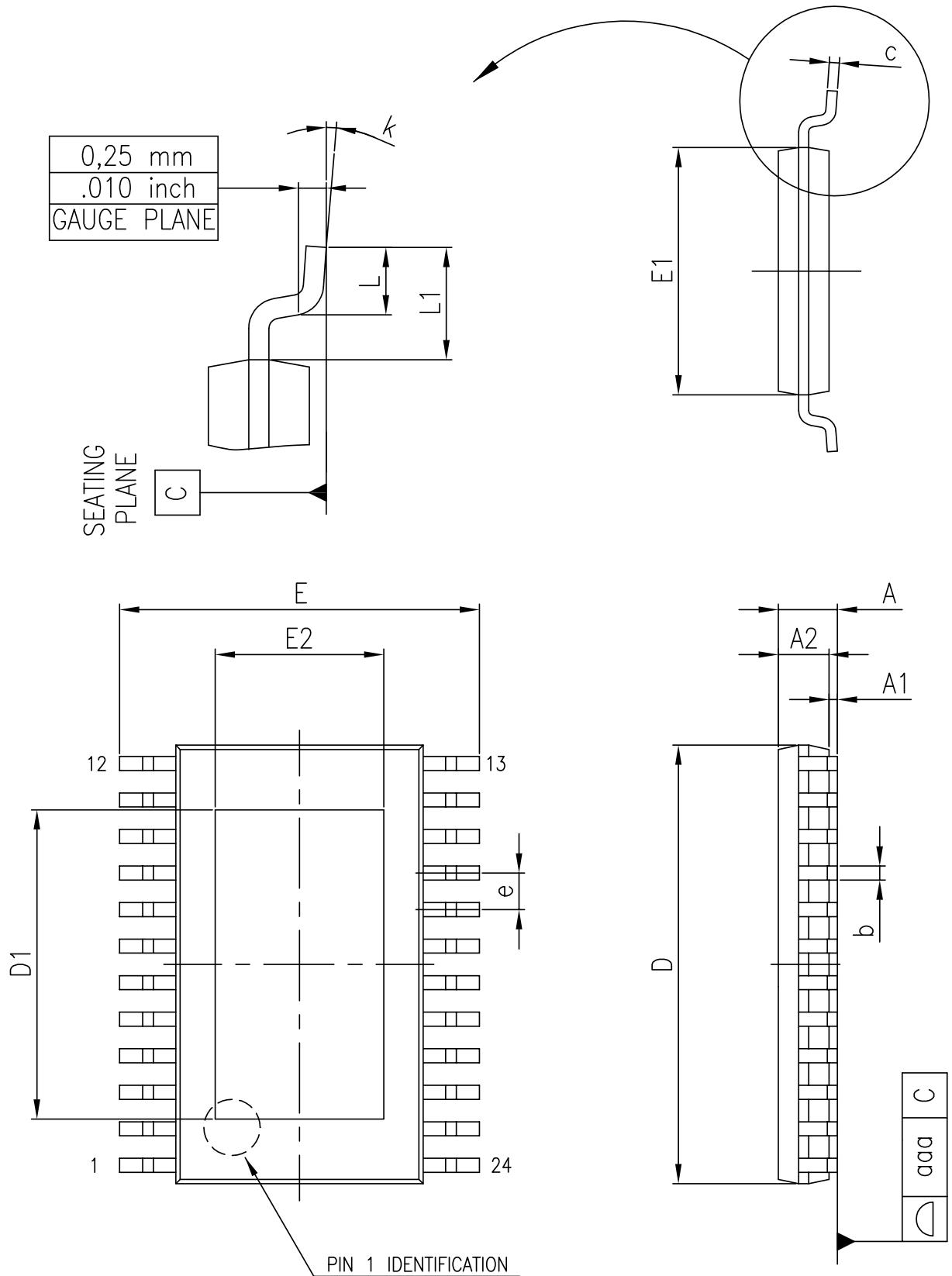

**Table 2. HTSSOP-24 pins list**

| Pin number | Symbol  | Function                 |

|------------|---------|--------------------------|

| 1          | VBATT   | Battery voltage          |

| 2          | SOURCE0 | HS Source 0              |

| 3          | DRAIN7  | LS/HS Drain 7            |

| 4          | SOURCE7 | LS/HS Source 7           |

| 5          | DRAIN6  | LS/HS Drain 6            |

| 6          | SOURCE6 | LS/HS Source 6           |

| 7          | DRAIN5  | LS/HS Drain 5            |

| 8          | SOURCE5 | LS/HS Source 5           |

| 9          | IN1     | Parallel command input 1 |

| 10         | IN0     | Parallel command input 0 |

| 11         | GND     | Ground pin               |

| 12         | IDLE    | Idle function            |

| 13         | VDDIO   | IO supply                |

| 14         | SO      | SPI output stream        |

| 15         | CLK     | SPI clock                |

| 16         | NCS     | SPI Chip Select          |

| 17         | SI      | SPI input stream         |

| 18         | DRAIN4  | LS/HS Drain 4            |

| 19         | SOURCE4 | LS/HS Source 4           |

| 20         | DRAIN3  | LS/HS Drain 3            |

| 21         | SOURCE3 | LS/HS Source 3           |

| 22         | DRAIN2  | LS/HS Drain 2            |

| 23         | SOURCE2 | LS/HS Source 2           |

| 24         | SOURCE1 | HS Source 1              |

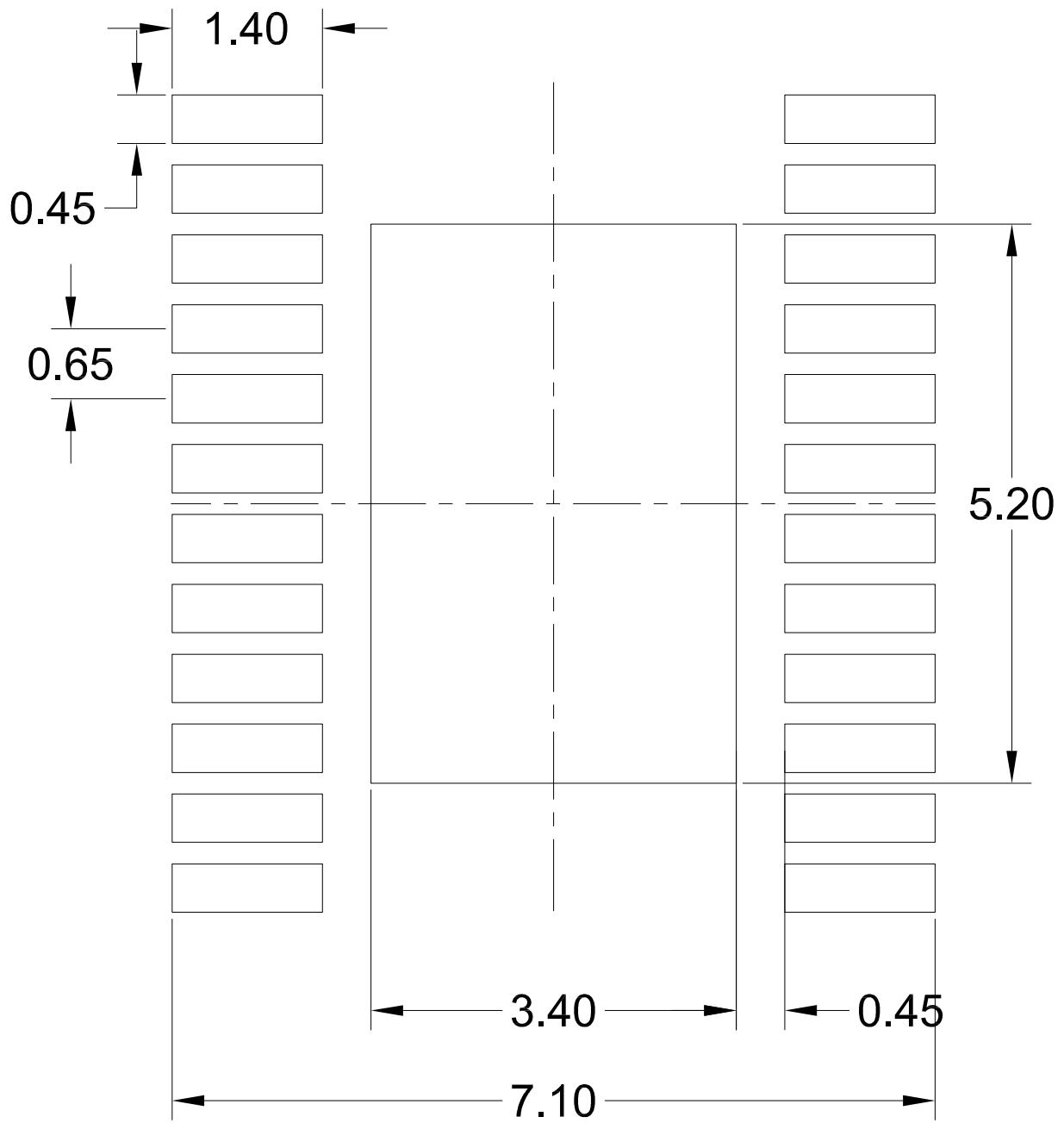

Table 3. VFQFPN32 pins list

| Pin number QFN32 | Symbol  | Function                                             |

|------------------|---------|------------------------------------------------------|

| 1                | DRAIN7  | LS/HS Drain 7                                        |

| 2                | SOURCE7 | LS/HS Source 7                                       |

| 3                | DRAIN6  | LS/HS Drain 6                                        |

| 4                | SOURCE6 | LS/HS Source 6                                       |

| 5                | DRAIN5  | LS/HS Drain 5                                        |

| 6                | SOURCE5 | LS/HS Source 5                                       |

| 7                | NRES    | NRES function – available only in VFQFPN32 package   |

| 8                | DIS     | Channel disable – available only in VFQFPN32 package |

| 9                | IN1     | Parallel command input 1                             |

| 10               | IN0     | Parallel command input 0                             |

| 11               | N.C.    | -                                                    |

| 12               | GND     | Ground pin                                           |

| 13               | IDLE    | Idle function                                        |

| 14               | VDDIO   | IO supply                                            |

| 15               | SO      | SPI output stream                                    |

| 16               | CLK     | SPI clock                                            |

| 17               | NCS     | SPI Chip Select                                      |

| 18               | SI      | SPI input stream                                     |

| 19               | DRAIN4  | LS/HS Drain 4                                        |

| 20               | SOURCE4 | LS/HS Source 4                                       |

| 21               | DRAIN3  | LS/HS Drain 3                                        |

| 22               | SOURCE3 | LS/HS Source 3                                       |

| 23               | DRAIN2  | LS/HS Drain 2                                        |

| 24               | SOURCE2 | LS/HS Source 2                                       |

| 25               | N.C.    | -                                                    |

| 26               | N.C.    | -                                                    |

| 27               | SOURCE1 | HS Source 1                                          |

| 28               | DRAIN1  | HS Drain 1                                           |

| 29               | VBATT   | Battery voltage                                      |

| 30               | DRAIN0  | HS Drain 0                                           |

| 31               | SOURCE0 | HS Source 0                                          |

| 32               | N.C.    | -                                                    |

Note:

- In case of VFQFPN32 package, CFG\_0.DIS\_EN and bit CFG\_0.NRES\_N need to be set through SPI.

- In case of HTSSOP24 package, NRES and DIS pins are not available; CFG\_0.DIS\_EN and bit CFG\_0.NRES\_N must be considered as reserved, kept at '0'.

- For both package options the exposed pad must be left floating to guarantee the reverse battery protection feature.

## 4 Product characteristics

### 4.1

#### Absolute maximum ratings

This part may be irreparably damaged if taken outside the specified Absolute Maximum Ratings. Operation above the Absolute Maximum Ratings may also cause a decrease in reliability.

The operating junction temperature range is -40 °C to +150 °C. The maximum junction temperature must not be exceeded. All voltages are referred to analog ground pin GND.

**Table 4. Absolute maximum rating capability**

| Symbol                  | Type   | Test condition                                                                                   | Min                      | Typ | Max                               | Unit | Pin type |

|-------------------------|--------|--------------------------------------------------------------------------------------------------|--------------------------|-----|-----------------------------------|------|----------|

| VBATT                   | Global | ton = 400 ms; ton/toff = 10 %; limited to 100 pulses                                             | -0.3                     | -   | 42                                | V    | S        |

| VDDIO                   | Local  | -                                                                                                | -0.3                     | -   | 20                                | V    | S        |

| -VBATT <sub>(REV)</sub> | Global | Reverse polarity voltage T = 25 °C, t < 2min, RL=70 Ω on all channels, with exposed pad floating | -                        | -   | 16                                | V    | S        |

| V <sub>OUT_S</sub>      | Global | Power transistor source voltage                                                                  | -16                      | -   | Min[V <sub>OUT_D</sub> + 0.3, 42] | V    | O        |

| V <sub>OUT_D</sub>      | Global | Power transistor drain voltage (V <sub>OUT_S</sub> ≥ 0 V)                                        | V <sub>OUT_S</sub> - 0.3 | -   | 42                                | V    | O        |

| V <sub>IDLE</sub>       | Local  | -                                                                                                | -0.3                     | -   | 20                                | V    | I        |

| V <sub>IN0</sub>        | Local  | -                                                                                                | -0.3                     | -   | 20                                | V    | I        |

| V <sub>IN1</sub>        | Local  | -                                                                                                | -0.3                     | -   | Min[V <sub>DDIO</sub> + 0.3, 20]  | V    | I        |

| V <sub>NCS</sub>        | Local  | -                                                                                                | -0.3                     | -   | 20                                | V    | I        |

| V <sub>CLK</sub>        | Local  | -                                                                                                | -0.3                     | -   | 20                                | V    | I        |

| V <sub>SI</sub>         | Local  | -                                                                                                | -0.3                     | -   | 20                                | V    | I        |

| V <sub>SO</sub>         | Local  | -                                                                                                | -0.3                     | -   | Min[V <sub>DDIO</sub> + 0.3, 20]  | V    | O        |

| V <sub>IN</sub>         | Local  | Applies to : V <sub>NRES</sub> V <sub>DIS</sub>                                                  | -0.3                     | -   | 20                                | V    | I        |

### 4.2

#### Latchup trials

Latch-up tests performed according to JEDEC 78 class 2 Level A

## 4.3 Temperature range

Table 5. Temperature range

| Symbol | Description                            | Test condition                                                          | Min | Typ | Max | Unit |

|--------|----------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| Ta     | Operating ambient temperature          | -                                                                       | -40 | -   | 125 | °C   |

| Tj     | Junction temperature                   | -                                                                       | -40 | -   | 150 | °C   |

| Tstg   | Storage temperature                    | -                                                                       | -55 | -   | 150 | °C   |

| RTHj-a | Thermal resistance junction to ambient | - Package: HTSSOP - 2s2p (4L) board <sup>(1)</sup> - Natural convection | -   | 38  | -   | °C/W |

| RTHj-c | Thermal resistance junction to case    |                                                                         | -   | 1   | -   |      |

| RTHj-b | Thermal resistance junction to board   |                                                                         | -   | 20  | -   |      |

| RTHj-a | Thermal resistance junction to ambient | - Package: VFQFPN - 2s2p (4L) board <sup>(1)</sup> - Natural convection | -   | 36  | -   | °C/W |

| RTHj-c | Thermal resistance junction to case    |                                                                         | -   | 4   | -   |      |

| RTHj-b | Thermal resistance junction to board   |                                                                         | -   | 18  | -   |      |

1. JESD51-7

All parameters are guaranteed, and tested, in the temperature range Tj -40 ÷ 150 °C (unless otherwise specified).

## 5 Input/Output

### 5.1 Parallel inputs (IN0, IN1)

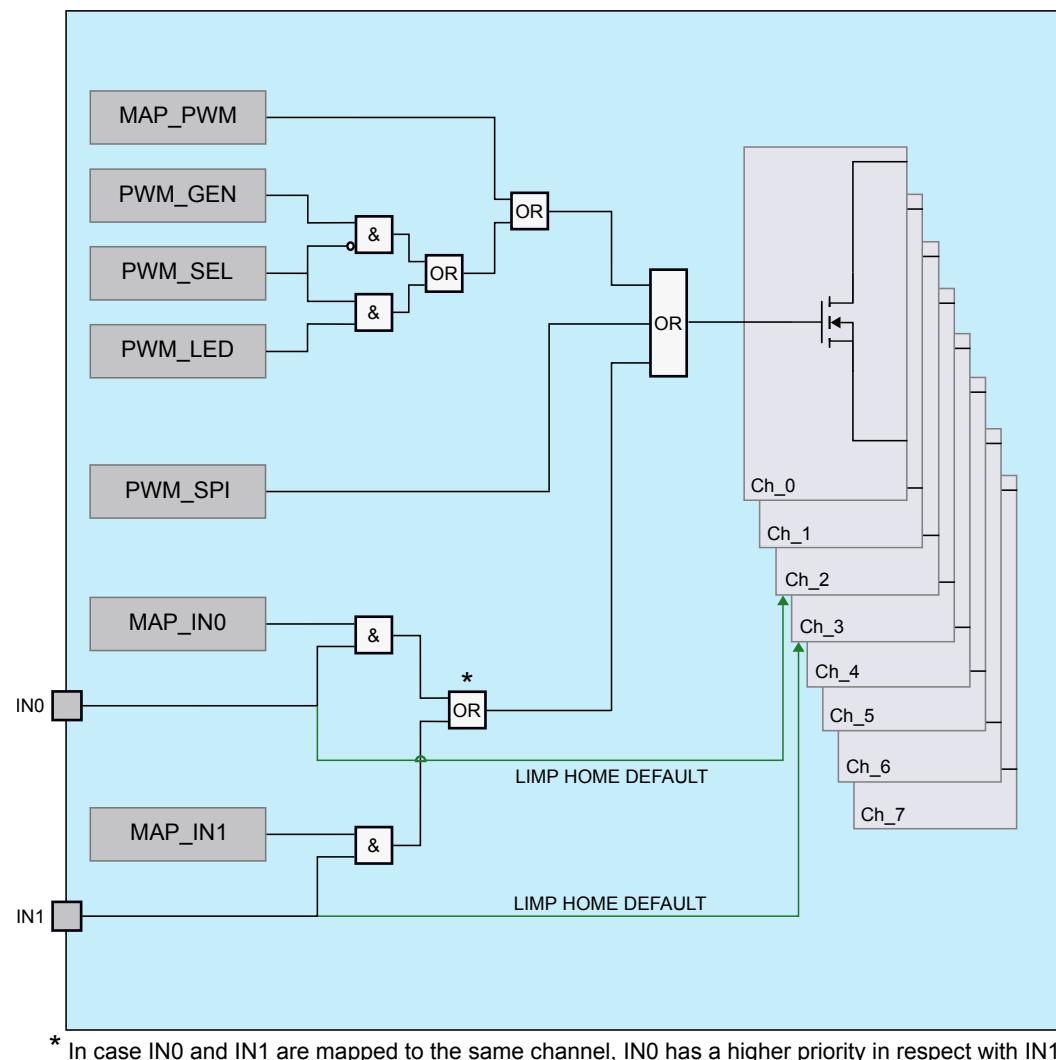

Device has two input pins available. Each input pin is connected by default to one channel (IN0 to channel 2, IN1 to channel 3). Input Mapping Registers MAP\_IN0 and MAP\_IN1 can be programmed to connect different channels to each input pin. The signals driving the channels are an OR combination between PWM\_SPI register status, PWM Generators (according to PWM Generator Output Mapping status), IN0 and IN1 (according to Input Mapping registers status). See [Section 11 SPI](#) for further details.

The logic level of the input pins can be monitored via the status register STA\_0. The Input Status Monitor is operative also when device is in Limp Home mode. If one of the Input pins is set to "high" and the IDLE pin is set to "low", the device switches into Limp Home mode and activates the channel mapped by default to the input pins.

### 5.2 Idle pin (IDLE)

The IDLE pin is used to bring the device into Sleep mode operation when is set to "low" together with IN0, IN1 input pins being at "low" state. When IDLE pin is set to "low" while one of the input pins is set to "high" the device enters Limp Home mode.

To ensure a proper mode transition, IDLE pin must be set for at least  $t_{IDLEFLT\_max}$  (transition from "high" to "low" or from "low" to "high").

Setting the IDLE pin to "low", with both IN0 and IN1 also at "low" value, has the following consequences:

- Device goes in SLEEP MODE

- All registers in the SPI are reset to default values

- VDDIO and VBATT Under voltage detection circuits are disabled to decrease current consumption

- No SPI communication is allowed: SO pin remains in high impedance state also when NCS pin is active.

### 5.3 Reset pin (NRES, only in VFQFPN32 package option)

The NRES pin, available only for VFQFPN32 version, is the reset input for the device. The function uses the inverse logic, if the NRES pin is low, the device is held in an internal reset state, all outputs channels are disabled, and all registers are reset to their default values. An internal pull down will hold the NRES pin asserted in case of pin open. As default, the state of NRES pin is masked by the logic. The user must send a specific SPI frame to force the logic to take into account the state of NRES pin.

### 5.4 Enable (DIS, only in VFQFPN32 package option)

The DIS pin, available only for VFQFPN32 version, is used to enable / disable the output stages. When DIS pin is high, all channels are disabled if the pin is not masked. An internal pull up will hold the DIS pin asserted in case of pin open.

When DIS pin is set low, all channels are enabled based on their configuration settings. As default, the DIS pin is masked by the logic. The user needs to send a specific SPI frame to force the logic to take into account the state of DIS pin. The status of DIS pin can be monitored reading the STA\_0 register.

The DIS pin can be connected to a general purpose output pin of the microcontroller or to an alternative safety circuit.

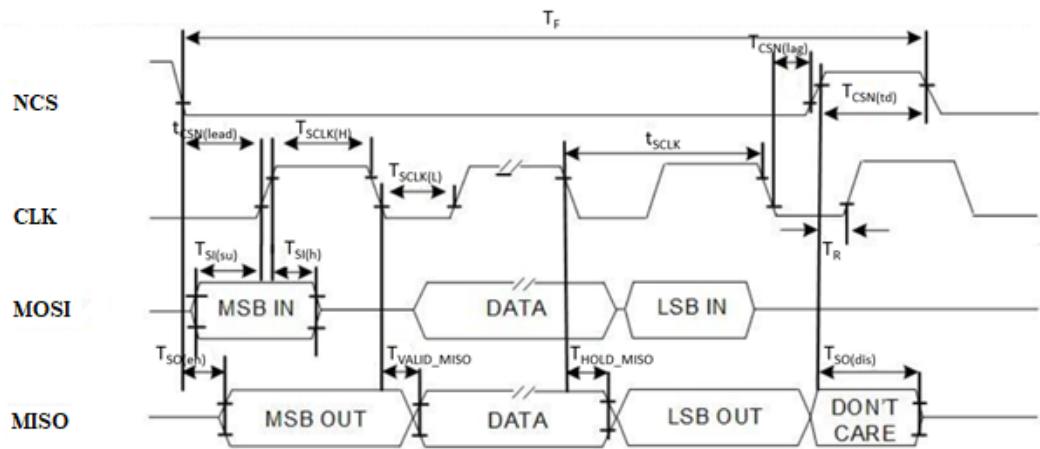

### 5.5 SPI communications (NCS, CLK, SI & SO)

The NCS, CLK, SI & SO pins provide serial communications between the device and the microcontroller. See [Section 11 SPI](#) for details on SPI features, device register functions and electrical characteristics.

## 5.6

## Input / output electrical specifications

$3 \text{ V} \leq \text{VDDIO} \leq 5.5 \text{ V}$ ;  $6 \text{ V} \leq \text{VBATT} \leq 18 \text{ V}$ ;  $-40 \text{ }^{\circ}\text{C} \leq \text{Tj} \leq 150 \text{ }^{\circ}\text{C}$  unless otherwise specified. All voltages are referred to GND pin.

Table 6. Digital input/output electrical performance

| Parameter            | Description                                 | Test condition                                                  | Min | Typ | Max | Unit       | Pin     |

|----------------------|---------------------------------------------|-----------------------------------------------------------------|-----|-----|-----|------------|---------|

| $V_{\text{IDLE(L)}}$ | L-input level                               | -                                                               | -   | -   | 0.8 | V          | IDLE    |

| $V_{\text{IDLE(H)}}$ | H-input level                               | -                                                               | 2   | -   |     | V          | IDLE    |

| $R_{\text{IDLE}}$    | Input pull-down resistor at IDLE pin        | $\text{VDDIO} = 5 \text{ V}$ ; $V_{\text{DIS}} = 2 \text{ V}$   | 60  |     | 125 | k $\Omega$ | IDLE    |

| $V_{\text{IN(L)}}$   | L-input level                               | -                                                               | -   | -   | 0.8 | V          | IN0-IN1 |

| $V_{\text{IN(H)}}$   | H-input level                               | -                                                               | 2   |     |     | V          | IN0-IN1 |

| $R_{\text{IN}}$      | Input pull-down resistor at IN0 and IN1 pin | $\text{VDDIO} = 5 \text{ V}$ ; $V_{\text{DIS}} = 2 \text{ V}$   | 60  | -   | 125 | k $\Omega$ | IN0-IN1 |

| $V_{\text{NRES(L)}}$ | L-input level                               | -                                                               | -   | -   | 0.8 | V          | NRES    |

| $V_{\text{NRES(H)}}$ | H-input level                               | -                                                               | 2   | -   |     | V          | NRES    |

| $R_{\text{NRES}}$    | Input pull-down resistor at NRES pin        | $\text{VDDIO} = 5 \text{ V}$ ; $V_{\text{DIS}} = 2 \text{ V}$   | 50  | -   | 140 | k $\Omega$ | NRES    |

| $V_{\text{DIS(L)}}$  | L-input level                               | -                                                               | -   | -   | 0.8 | V          | DIS     |

| $V_{\text{DIS(H)}}$  | H-input level                               | -                                                               | 2   | -   |     | V          | DIS     |

| $R_{\text{DIS}}$     | Input pull-up resistor at DIS pin           | $\text{VDDIO} = 5 \text{ V}$ ; $V_{\text{DIS}} = 0.8 \text{ V}$ | 40  | -   | 95  | k $\Omega$ | DIS     |

## 6 Power supply

### 6.1 Overview

The L9026 is fed by two supply voltages:

- VBATT (general supply for analog and digital part)

- VDDIO (supply for digital and output buffers)

The supply lines are monitored against under voltage: in case under voltage condition is detected the IC reacts as per the following:

- An under voltage on VBATT supply voltage prevents the activation of the power stages.

- An under voltage on VDDIO supply prevents any SPI communication and SPI read/write registers are reset to default values.

The combination of the different under voltage conditions is reported in [Table 7](#).

**Table 7. Supply ranges**

|                                  | $VDDIO \leq VDDIO_{(UV)}$                                                | $VDDIO > VDDIO_{(UV)}$                     |

|----------------------------------|--------------------------------------------------------------------------|--------------------------------------------|

| VBATT $\leq$ VBATT <sub>UV</sub> | channels cannot be controlled                                            | channels cannot be controlled              |

|                                  | SPI registers reset                                                      | SPI registers available                    |

|                                  | SPI communication not available                                          | SPI communication possible                 |

|                                  | Limp Home mode not available                                             | Limp Home mode available(channels are OFF) |

| VBATT $>$ VBATT <sub>UV</sub>    | channels cannot be controlled by SPI (INn functionality still available) | channels can be switched ON and OFF        |

|                                  | SPI registers reset                                                      | SPI registers available                    |

|                                  | SPI communication not available                                          | SPI communication possible                 |

### 6.2 Battery supply (VBATT)

This pin is the general supply for analog and digital part unless an undervoltage condition is detected on VBATT. In this case, provided VDDIO is still in range, the logic is supplied by the VDDIO itself. The [Table 8](#) summarizes the functional ranges dependent on battery supply voltage.

**Table 8. VBATT electrical performance**

| Symbol            | Parameter                                          | Test condition                                   | Min | Typ | Max | Unit |

|-------------------|----------------------------------------------------|--------------------------------------------------|-----|-----|-----|------|

| VBATT             | Supply Voltage Range for normal operations         | $3 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$ | 6   | -   | 18  | V    |

| VBATT             | Upper Supply Voltage Range for extended operations | $3 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$ | 18  | -   | 28  | V    |

| VBATT Low Voltage | Low Voltage Range Cranking <sup>(1)</sup>          | $3 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$ | 3   | -   | 6   | V    |

1. Possible degradation of electrical parameters linked to battery line. Full functional operation will resume without operator intervention when battery voltage returns to Normal Operating Voltage Range.

The device operates on 12 V system. Transient operation for these systems can reach 40 V maximum. Particular care has to be taken in PCB manufacturing to keep thermal dissipation to a reasonable level.

- For  $\text{VBATT} < \text{VBATT}_{(UV)}$  the device is in a safety state (internal circuitries are on but all the outputs are off).

- For  $\text{VBATT}$  up to 40 V all the functions are granted with increased power dissipation and no reset is asserted during transient.

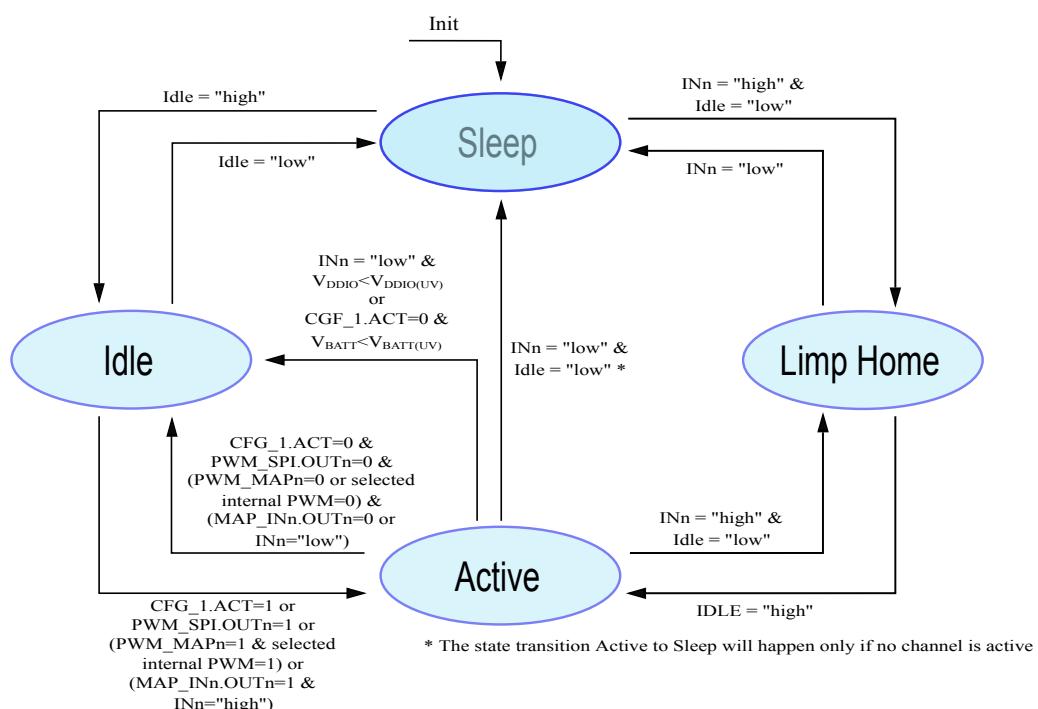

## 6.3 Operating modes

The L9026 has 4 operative modes as per below:

- Sleep mode

- Idle mode

- Active mode

- Limp Home mode

The transition between operation modes is determined according to the following levels and states:

- logic level at IDLE pin

- logic level at INn pins

- PWM\_SPI.OUTn bits state

- CFG\_1.ACT bit state

- MAP\_PWM.OUTn and PWM\_SEL.OUTn bits state

The Figure 6 represents the possible transitions in the state diagram. The description is valid if the digital POR signal is de-asserted (indicated as POR\_N in the register map). In case of POR = 0 transitions from Active to idle and from Limp Home to Sleep do not guarantee switch off behavior with functional timings. A POR condition is traced in a clear on read register in the STA\_1.POR bit. The behavior of the device as well as some parameters may change depending on the operating mode of the device. Furthermore, due to the under voltage detection circuitry which monitors VBATT and VDDIO supply voltages, some changes within the same operation mode can be seen accordingly.

In case of  $VBATT < VBATT(UV_L)$  and  $IDLE = IN0 = IN1 = \text{high}$  device doesn't go from IDLE state to ACTIVE state.

Starting from Active state the conditions to reach Sleep state are  $IDLE = '0'$  and  $INn = '0'$  and drivers turn OFF that is guaranteed through SW reset.

There are different options to observe the operation mode of the device:

- status of output channels

- status of SPI registers

- current consumption at VBATT pin (IVBATT)

Figure 6. State diagram

The default operation mode to switch ON the loads is Active mode. If the device is not in Active mode and a request to switch ON one or more outputs occur (via SPI or via Input pins), it will switch into Active or Limp Home mode, according to IDLE pin status. Due to the time needed for such transitions, output turn-on time  $t_{ON}$  will be extended due to the mode transition latency.

Table 9 shows the correlation between device operation modes, VBATT and VDDIO supply voltages, and state of device functions (channels operability, SPI communication and SPI registers).

**Table 9. Functions availability in different supply conditions**

| Operating mode | Function      | Under voltage condition on VBATT |                               | VBATT not in under voltage       |                               |

|----------------|---------------|----------------------------------|-------------------------------|----------------------------------|-------------------------------|

|                |               | VDDIO $\leq$ VDDIO <sub>UV</sub> | VDDIO $>$ VDDIO <sub>UV</sub> | VDDIO $\leq$ VDDIO <sub>UV</sub> | VDDIO $>$ VDDIO <sub>UV</sub> |

| Sleep          | Channels      | not available                    | not available                 | not available                    | not available                 |

|                | SPI comm.     | not available                    | not available                 | not available                    | not available                 |

|                | SPI registers | reset                            | reset                         | reset                            | reset                         |

| Idle           | Channels      | not available                    | not available                 | not available                    | not available                 |

|                | SPI comm.     | not available                    | available                     | not available                    | available                     |

|                | SPI registers | reset                            | available                     | reset                            | available                     |

| Active         | Channels      | not available                    | not available                 | available (IN pins only)         | available                     |

|                | SPI comm.     | not available                    | available                     | not available                    | available                     |

|                | SPI registers | reset                            | available                     | reset                            | available                     |

| Limp Home      | Channels      | not available                    | not available                 | available (IN pins only)         | available (IN pins only)      |

|                | SPI comm.     | not available                    | available (read-only)         | not available                    | available (read-only)         |

|                | SPI registers | reset                            | available (read-only)         | reset                            | available (read-only)         |

## 6.4 Analog & Digital supply (VBATT)

The VBATT is used to supply the internal logic, analog and digital, in normal condition (no under voltage on VBATT) and the output loads.

In case the voltage drops below VBATT<sub>(UV\_L)</sub> the under voltage mechanism is triggered and the bit STA\_1.VS\_UV is reported via SPI. Once the faulty condition disappears (VBATT  $>$  VBATT<sub>(UV\_H)</sub>), the bit remains latched until its status is acknowledged by the microcontroller via SPI.

Under voltage condition on VBATT influences the status of the channels as described in Table 7.

## 6.5 I/O Supply (VDDIO)

VDDIO is the supply for all pins that interface with the external microcontroller and also work as feed for the internal logic if VBATT is in under voltage condition.

In case the voltage drops below VDDIO<sub>(UV)</sub> the under voltage mechanism is triggered and the bit STA\_1.VDD\_UV is reported via SPI. This is valid if digital POR\_N is '1'. For all conditions that generate a POR\_N=0, a dedicated clear on read STA\_1.POR\_N bit is set. Once the faulty condition disappears, the bit remains latched until its status is acknowledged by the microcontroller via SPI.

## 6.6 Power up

The IC performs Power-up procedure when VBATT is applied to the device and the INn or IDLE pins are set to "high".

To complete power-up procedure VBATT  $>$  6 V (min Supply Voltage Range for normal operations) shall be applied, no matter which voltage is present on VDDIO, that may also be left disconnected.

Only after power completion, the device is fully able to guarantee the behavior as described in the Table 7 and Table 9.

## 6.7

### Sleep mode

When device is in Sleep mode, all outputs are OFF and the SPI registers are reset, independently of the supply voltages. The current consumption is reduced to the IVDDIO(SLEEP) and IVBATT(SLEEP).

## 6.8

### Idle mode

In Idle mode, the current consumption of the device reaches the parameters IVDDIO(IDLE) and IVBATT(IDLE). The internal voltage regulator is still working. ON diagnosis functions are not available. The output channels are switched OFF, independently of the supply voltages. When VDDIO is available, the SPI registers are working and SPI communication is possible. In Idle mode the DIAG\_OVC\_OVT bits are not cleared.

## 6.9

### Active mode

Active mode is the normal operation mode when no Limp Home condition is set and it is necessary to drive some or all loads. Voltage levels of VDDIO and VBATT influence the behavior as described in detail in [Section 6.1 Overview](#). Device current consumption is specified with IVDDIO(ACTIVE) and IVBATT(ACTIVE).

In case CFG\_1.ACT is set to “1”, the device enters in Active mode and remains in this state independently on the status of input pins, of internal PWM generators and PWM\_SPI.OUTn bits.

Otherwise, in case the bit CFG\_1.ACT is not set, in order to move the device in Active mode all conditions below are needed:

- the IDLE pin set to “high”

- the outputs configured as driven either by external pins (through MAPIN0, MAPIN1 registers) or by SPI (at least one PWM\_SPI.OUTn bit is set to “1”) or by the internal PWM generators (through MAP\_PWM)

- at least one channel enabled

In this scenario, the device returns to Idle mode as soon as IDLE pin is set to “low”, all inputs pins are set to “low”, all PWM\_SPI.OUTn bits are set to “0” and all the internal pwm generators are OFF.

Being the IDLE pin asserted high, an under voltage condition on VDDIO supply brings the device into Idle mode once all INn input pins are set to “low”, on top of the setting of the bit CFG\_1.ACT.

## 6.10 Limp Home mode

Device enters Limp Home mode when IDLE pin is “low” and one of the input pins is set to “high”, switching ON the channel connected to it. SPI communication is possible but in read-only mode (SPI registers can be read but cannot be written).

More in detail, Limp Home mode has the following effects:

- IN0 is mapped as channel 2 input command, IN1 is mapped as channel 3 input command

- MODE bits are set to “01B” (Limp Home mode)

- Overload and Over temperature diagnostics on channel 2 and 3 are available and the related DIAG\_OVC\_OVT bits can be read.

Entering Limp Home mode from sleep means that all other registers are set to their default value and cannot be programmed as long as the device is in Limp Home mode (SPI is in read only mode) so far a special feature for Channel 2 and 3 is implemented and channels are able of auto-configuring as LS or HS depending on the configuration of the external load.

Open in ON diagnosis is not performed in Limp Home mode. This is true also if Limp Home mode has been entered from Active mode and DIAG\_OPL\_ON\_EN.OUTn bits are set to ‘1’. In this case, the diagnostic cycles will be performed only when back in ACTIVE mode.

See [Table 9](#) for a detailed overview of supply voltage conditions required to switch ON channels 2 and 3 during Limp Home. All other channels are kept OFF.

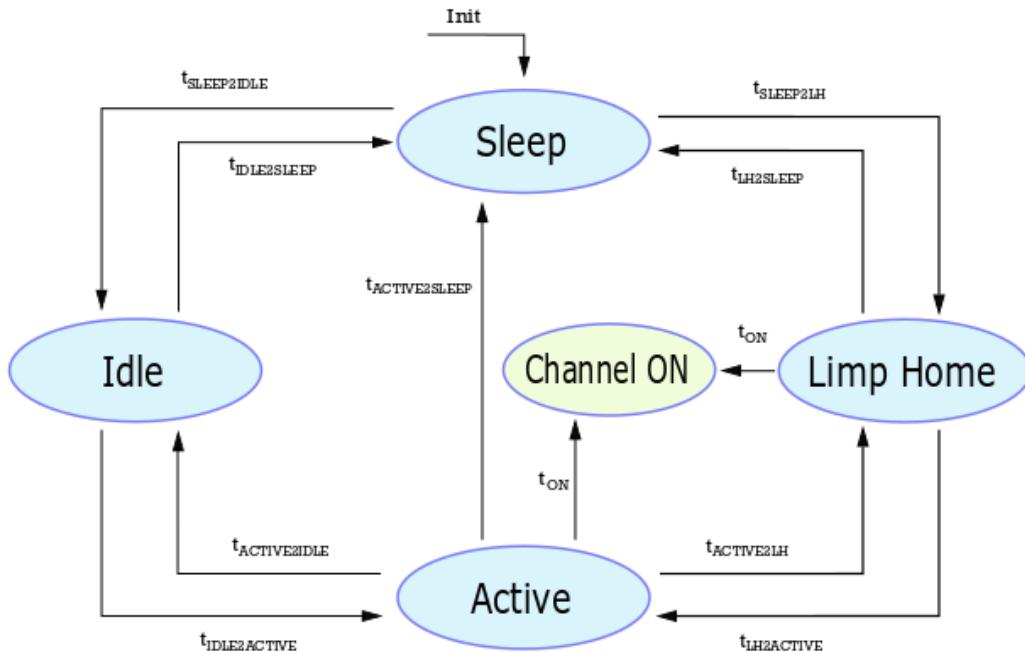

## 6.11 Power supply transition

The channel turn-ON time is defined by parameter  $t_{ON}$  when device is in Active mode or in Limp Home mode. In all other cases, it is necessary to add the transition time required to reach one of the two above mentioned Power Supply modes, as reported in [Figure 7](#).

**Figure 7. Transition times block diagram**

## 6.12 Reset

One of the following 4 conditions reset the SPI read/write registers to the default value:

- VDDIO not present or below the undervoltage threshold VDDIO(UV)

- IDLE pin is set to "low" with both INn "low"

- A software reset (CFG\_1.RST set to "1") is commanded

- NRES pin is asserted (only available in VFQFPN32 package option and configured to sense the pin status)

When the SPI registers are reset, all channels (except 2,3) are switched OFF and the Input Mapping configuration is also reset. This means channels 2, 3 are still commanded by IN0, IN1 respectively.

For functional safety register DIAG\_OVC\_OVT and STA\_1.VDDIO\_UV, STA\_1.VBATT\_UV bits are not cleared by a reset command.

One of the following conditions resets the whole internal logic:

- General internal supply failure (internal supply 3.3 V in UV or bandgap reference not correct)

- VDDIO < VDDIO(UV) and IN1 = 0 and IN0 = 0

## 6.13 Power supply electrical specifications

3V ≤ VDDIO ≤ 5.5 V; 6 V ≤ VBATT ≤ 18 V; -40 °C ≤ Tj ≤ 150 °C unless otherwise specified. All voltages are referred to GND pin.

**Table 10. Power supply electrical parameters**

| Parameter               | Description                                                                                                            | Test condition                                                                                                                                                                                             | Min  | Typ  | Max | Unit |

|-------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| VBATT pin               |                                                                                                                        |                                                                                                                                                                                                            |      |      |     |      |

| VBATT(UV_L)             | Analog supply undervoltage low threshold                                                                               | -                                                                                                                                                                                                          | 2.65 | 2.8  | 3   | V    |

| VBATT(UV_H)             | Analog supply undervoltage high threshold                                                                              | -                                                                                                                                                                                                          | 2.7  | 2.85 | 3.1 | V    |

| IVBATT(SLEEP)           | Analog supply current consumption in Sleep mode                                                                        | V <sub>IDLE</sub> = 0; V <sub>INn</sub> = 0; VDDIO = 5 V; TJ ≤ 85 °C                                                                                                                                       | -    | -    | 12  | µA   |

| IVBATT(SLEEP)           | Analog supply current consumption in Sleep mode                                                                        | V <sub>IDLE</sub> = 0; V <sub>INn</sub> = 0; VDDIO = 5 V; TJ ≤ 175 °C                                                                                                                                      | -    | -    | 14  | µA   |

| IVBATT(IDLE)            | Analog supply current consumption in Idle mode                                                                         | V <sub>IDLE</sub> = 5 V; V <sub>INn</sub> = 0; VDDIO = 5 V; f <sub>CLK</sub> = 0 MHz; CFG_1.ACT = 0 <sub>B</sub> ; PWM_SPI.OUTn = 0 <sub>B</sub> ; DIAG_OFF_EN.OUTn = 0 <sub>B</sub>                       | -    | -    | 20  | mA   |

| IVBATT(IDLE_COR)        | Analog supply current consumption in Idle Mode with VBATT lower than VDDIO (device supplied by VDDIO)                  | V <sub>IDLE</sub> = 5 V; V <sub>INn</sub> = 0; VDDIO = 5 V; f <sub>CLK</sub> = 0 MHz; CFG_1.ACT = 0 <sub>B</sub> ; PWM_SPI.OUTn = 0 <sub>B</sub> ; DIAG_OFF_EN.OUTn = 0 <sub>B</sub> ; VBATT = VDDIO - 1 V | -0.1 | -    | 0.1 | mA   |

| IVBATT(ACTIVE)          | Analog supply current consumption in Active mode - channels OFF                                                        | V <sub>IDLE</sub> = 5 V; V <sub>INn</sub> = 0; VDDIO = 5 V; f <sub>CLK</sub> = 0 MHz; CFG_1.ACT = 1 <sub>B</sub> ; PWM_SPI.OUTn = 0 <sub>B</sub> ; DIAG_OFF_EN.OUTn = 0 <sub>B</sub>                       | -    | 14   | 20  | mA   |

| IVBATT(ACTIVE_COR)      | Analog supply current consumption in Active mode - channels OFF with VBATT lower than VDDIO (device supplied by VDDIO) | V <sub>IDLE</sub> = 5 V; V <sub>INn</sub> = 0; VDDIO = 5 V; f <sub>CLK</sub> = 0 MHz; CFG_1.ACT = 1 <sub>B</sub> ; PWM_SPI.OUTn = 0 <sub>B</sub> ; DIAG_OFF_EN.OUTn = 0 <sub>B</sub> ; VBATT = VDDIO - 1 V | 0    | -    | 0.6 | mA   |

| t <sub>VBATTUVFLT</sub> | VBATT undervoltage filter                                                                                              | Covered bySCAN                                                                                                                                                                                             | 9    | 14   | 19  | µs   |

| Parameter                      | Description                                                     | Test condition                                                                                                                                                                            | Min  | Typ  | Max                | Unit |

|--------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------------------|------|

| <b>VDDIO pin</b>               |                                                                 |                                                                                                                                                                                           |      |      |                    |      |

| VDDIO <sub>(OP)</sub>          | Logic Supply Operating range voltage                            | $f_{CLK} = 8$ MHz                                                                                                                                                                         | 3    | -    | 5.5                | V    |

| VDDIO <sub>(UV_RECOVERY)</sub> | Analog supply threshold for recovery after battery undervoltage | MISO from “low” to high impedance                                                                                                                                                         | 2.7  | 2.85 | 3                  | V    |

| VDDIO <sub>(UV)</sub>          | Undervoltage shutdown                                           | MISO from “low” to high impedance                                                                                                                                                         | 2.65 | 2.8  | 2.95               | V    |

| I <sub>VDDIO(SLEEP)</sub>      | Logic supply current in Sleepmode                               | $V_{IDLE} = 0$ ; $V_{INn} = 0$ ; $VDDIO = 5$ VTJ $\leq 85$ °C                                                                                                                             | -    | -    | 1                  | µA   |

| I <sub>VDDIO(SLEEP)</sub>      | Logic supply current in Sleep mode                              | $V_{IDLE} = 0V$ ; $V_{INn} = 0$ V; $VDDIO = 5$ VTJ $\leq 150$ °C                                                                                                                          | -    | -    | 2                  | µA   |

| I <sub>VDDIO(IDLE)</sub>       | Logic supply current in Idle Mode                               | $V_{IDLE} = 5$ V; $V_{INn} = 0$ V; $VDDIO = 5$ V; $f_{CLK} = 0$ MHz; CFG_1.ACT = 0 <sub>B</sub> ; PWM_SPI.OUTn = 0 <sub>B</sub> ; DIAG_OFF_EN.OUTn = 0 <sub>B</sub>                       | -    | -    | 1.2                | mA   |

| I <sub>VDDIO(IDLE)</sub>       | Logic supply current in Idle mode (COR)                         | $V_{IDLE} = 5$ V; $V_{INn} = 0$ V; $VDDIO = 5$ V; $f_{CLK} = 0$ MHz; CFG_1.ACT = 0 <sub>B</sub> ; PWM_SPI.OUTn = 0 <sub>B</sub> ; DIAG_OFF_EN.OUTn = 0 <sub>B</sub> ; VBATT = VDDIO - 1 V | 2    | -    | 16                 | mA   |

| I <sub>VDDIO(ACTIVE)</sub>     | Logic supply current in Active mode – channels OFF              | $V_{IDLE} = 5$ V; $V_{INn} = 0$ V; $VDDIO = 5$ V; $f_{CLK} = 0$ MHz; CFG_1.ACT = 1 <sub>B</sub> ; PWM_SPI.OUTn = 0 <sub>B</sub> ; DIAG_OFF_EN.OUTn = 0 <sub>B</sub>                       | -    | 0.95 | 1.5                | mA   |

| I <sub>VDDIO(ACTIVE_COR)</sub> | Logic supply current in Active mode – channels OFF (COR)        | $V_{IDLE} = 5$ V; $V_{INn} = 0$ V; $VDDIO = 5$ V; $f_{CLK} = 0$ MHz; CFG_1.ACT = 1 <sub>B</sub> ; PWM_SPI.OUTn = 0 <sub>B</sub> ; DIAG_OFF_EN.OUTn = 0 <sub>B</sub> ; VBATT = VDDIO - 1 V | 12   | -    | 20                 | mA   |

| t <sub>VDDIOUVFLT</sub>        | VDDIO undervoltage filter                                       | Covered bySCAN                                                                                                                                                                            | 9    | 14   | 19                 | µs   |

| <b>Timings</b>                 |                                                                 |                                                                                                                                                                                           |      |      |                    |      |

| t <sub>IDLEFLT</sub>           | Idle filter time                                                | -                                                                                                                                                                                         | 5    | 7    | 10                 | µs   |

| t <sub>SLEEP2IDLE</sub>        | Sleep to Idle delay                                             | -                                                                                                                                                                                         | -    | -    | 10                 | µs   |

| t <sub>IDLE2SLEEP</sub>        | Idle to Sleep delay                                             | from IDLE pin to sleep<br>External pull-down MISO to GND required                                                                                                                         | -    | -    | 10                 | µs   |

| t <sub>IDLE2ACTIVE</sub>       | Idle to Active delay                                            | from INn or NCS pins to MODE = 11 <sub>B</sub>                                                                                                                                            | -    | -    | 1                  | µs   |

| t <sub>ACTIVE2IDLE</sub>       | Active to Idle delay                                            | from INn or NCS pins to MODE = 10 <sub>B</sub>                                                                                                                                            | -    | -    | 150                | µs   |

| t <sub>SLEEP2LH</sub>          | Sleep to Limp Home delay                                        | from INn pins to VDS = 10 % VBATT                                                                                                                                                         | -    | -    | 10+t <sub>ON</sub> | µs   |

| t <sub>LH2SLEEP</sub>          | Limp Home to Sleep delay                                        | from INn pins to MODE = 00 <sub>B</sub><br>External pull-down MISO to GND required.                                                                                                       | -    | -    | 150                | µs   |

| t <sub>LH2ACTIVE</sub>         | Limp Home to Active delay                                       | from IDLE pin to MODE = 11 <sub>B</sub>                                                                                                                                                   | -    | -    | 10                 | µs   |

| t <sub>ACTIVE2LH</sub>         | Active to Limp Home delay                                       | from IDLE pin to MODE = 01 <sub>B</sub>                                                                                                                                                   | -    | -    | 10                 | µs   |

| t <sub>ACTIVE2SLEEP</sub>      | Active to Sleep delay                                           | from IDLE pin to MODE = 00 <sub>B</sub><br>External pull-down MISO to GND required.                                                                                                       | -    | -    | 150                | µs   |

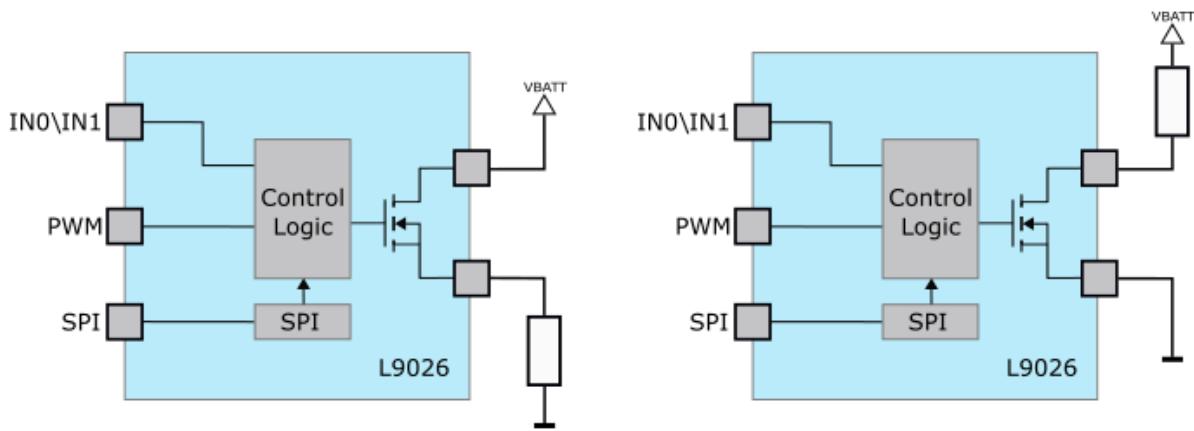

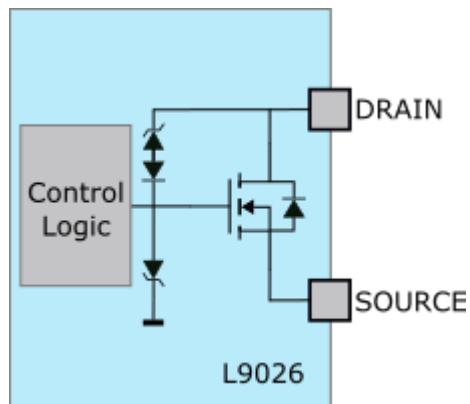

## 7 Power stages

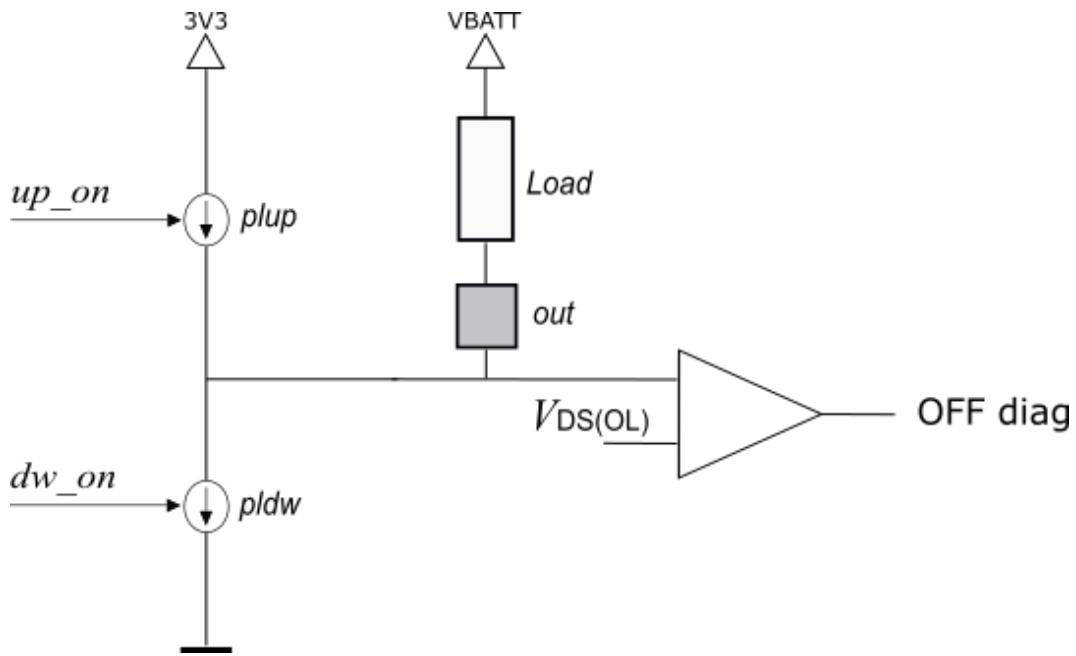

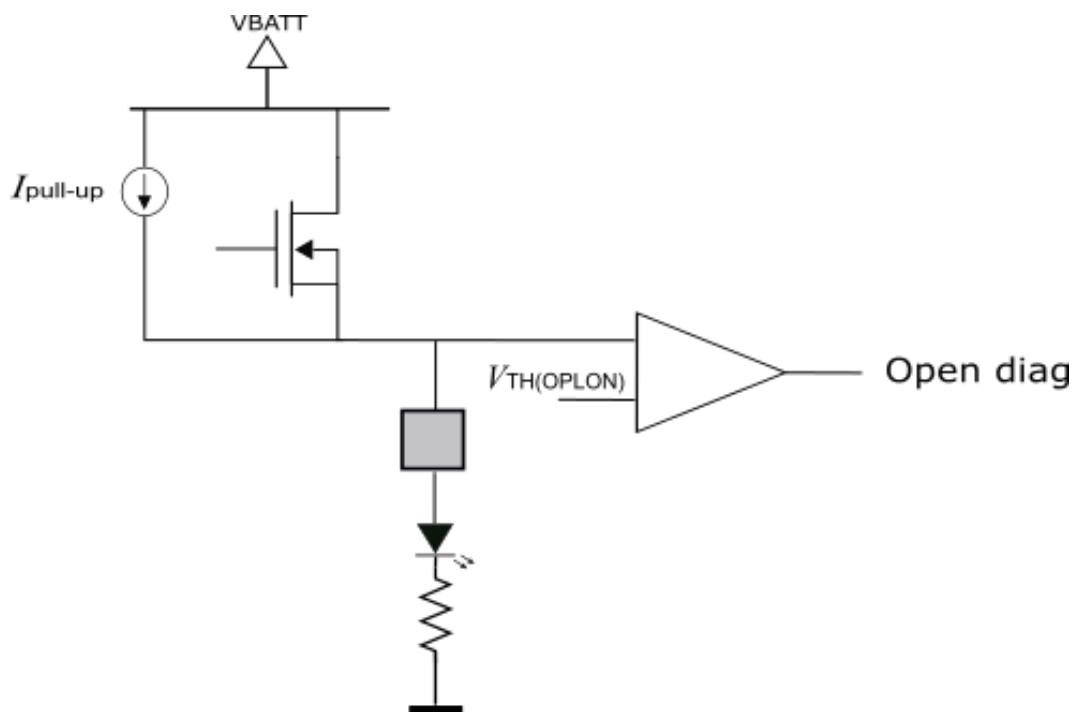

There are two fixed high-side channels and six channels which can be used either as low-side or as high-side switches. During the diagnosis in OFF State, the sequences of operations (pull-up or pull-down current source activation) are determined according to the SPI settings of CFG\_0 register.

For the configurable channels, when in high-side configuration, the load is connected between ground and source of the power transistor (pins SOURCEn, n = 2...7) while the drains (pins DRAINn, n = 2...7) can be connected to any potential between ground and VBATT.

In low-side configuration, the source of the power transistors must be connected to GND pin potential (either directly or through a reverse current blocking diode).

The configuration can be chosen for each of these configurable channels individually via SPI.

Figure 8. HS driver (left) and LS driver (right) configuration

### 7.1 Operating modes

The ON-state resistance  $R_{DS(ON)}$  depends on the supply voltage as well as the junction temperature  $T_J$ .

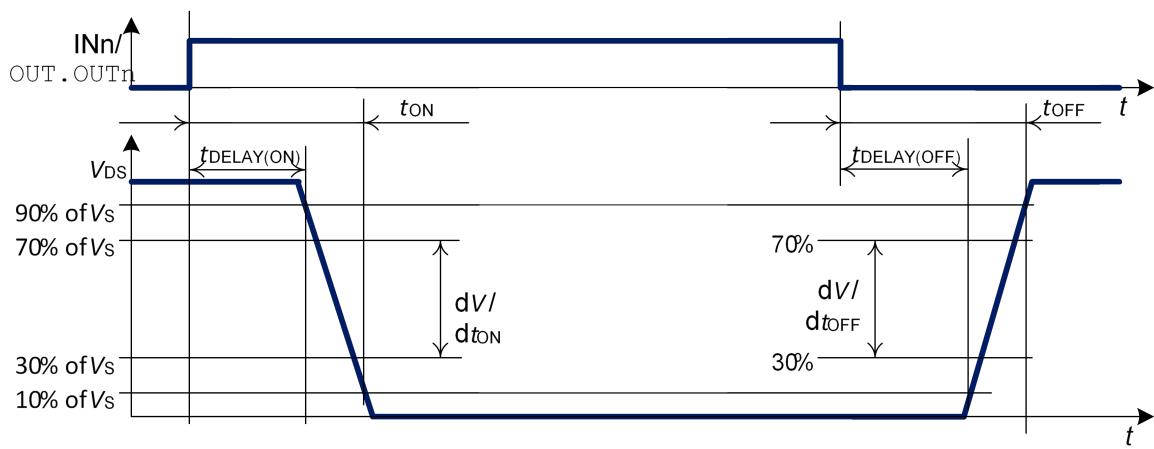

#### 7.1.1 Switching resistive modes

When switching resistive loads, the following switching times and slew rates can be considered.

Figure 9. Switching resistive loads

## 7.1.2

## Inductive output clamp

When switching off inductive loads, the voltage across the power switch rises to  $V_{DS(CL)}$  potential, because the inductance intends to continue driving the current. In case of HS configuration, the potential at Output pin is not allowed to go below  $V_{OUT\_S(CL)}$ . The voltage clamping is necessary to prevent device destruction.

To clarify this idea Figure 10 shows a concept drawing of the implementation.

Nevertheless, the maximum allowed load inductance is limited by the max energy. The clamping structure protects the device in all operative modes (Sleep, Idle, Active, Limp Home).

**Figure 10. Output clamp concept**

### 7.1.3

## Maximum load inductance

During demagnetization of inductive loads, energy has to be dissipated by the device. Eq. (1) shows how to calculate the energy for low-side switches, while Eq. (2) can be used for high-side switches (auto-configurable switches can use all equations, depending on the load position):

$$E = V_{DS(CL)} \cdot \left[ \frac{V_S - V_{DS(CL)}}{R_L} \cdot I_n \cdot \left( 1 - \frac{R_L \cdot I_L}{V_S - V_{DS(CL)}} \right) + I_L \right] \cdot \frac{L}{R_L} \quad (1)$$

$$E = (V_S - V_{DS(CL)}) \cdot \left[ \frac{V_{OUTS(CL)}}{R_L} \cdot I_n \cdot \left( 1 - \frac{R_L \cdot I_L}{V_{OUTS(CL)}} \right) + I_L \right] \cdot \frac{L}{R_L} \quad (2)$$

The maximum energy, which is converted into heat, is limited by the thermal design of the component. The  $E_{AR}$  value provided in Table 14 assumes that all channels can dissipate the same energy when the inductances connected to the outputs are demagnetized at the same time.

7.2

## Inverse current behavior

Inverse current ( $V_{OUTn_S} > V_{OUTn_D}$ ) in high-side configuration may occur with channels in ON or in OFF state. A reverse current applied to a specific channel has no impact on the general functionality (switch ON and OFF, protection, diagnostic) of unaffected channels.

Parameter deviations are possible for the switching capability of the affected channel, while protection against Over Load and off state diagnostic are not available. Reliability in Limp Home condition for the unaffected channels remains unchanged.

7.3

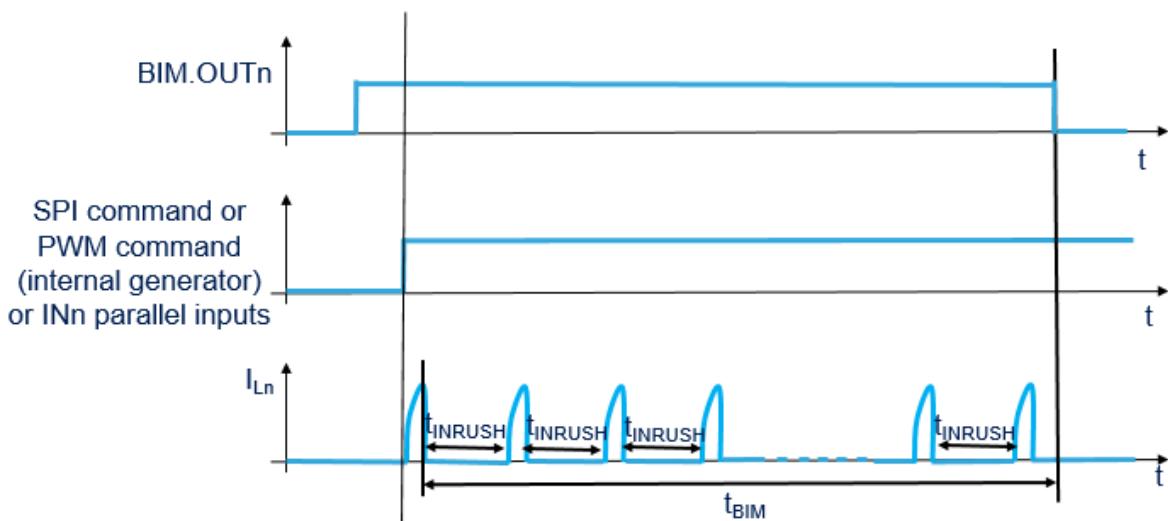

## Bulb inrush mode

Although device is optimized for relays and LED, it may be necessary to use one or more of the outputs as high-side switches to drive small lamps or electronic loads with a big input capacitor. In such a case the inrush current at startup may trigger the overload diagnostic, switching the channel OFF.

In normal operation in order to re-engage the channels from an overload condition, an SPI command to clear the latches (register `DIAG_OVC_OVT`) is needed, to allow the channel turning ON again; for some applications this re-engagement procedure takes too long to transfer enough energy to activate the load.

The IC provides the means to overcome this issue by setting BIM.OUTn bit to "1".

Once this feature is enabled, in case the channel reaches the overload current threshold and latches OFF, it restarts automatically after a time  $t_{INRUSH}$ , allowing the load to go out of the inrush phase. The automatic re-engagement of the faulty channels lasts for a BIM time ( $t_{BIM}$ ). Once the  $t_{BIM}$  counter is started, it is reset only once the  $t_{BIM}$  is expired, unless a reset condition occurs (VDDIO\_uv, hardware or software reset).

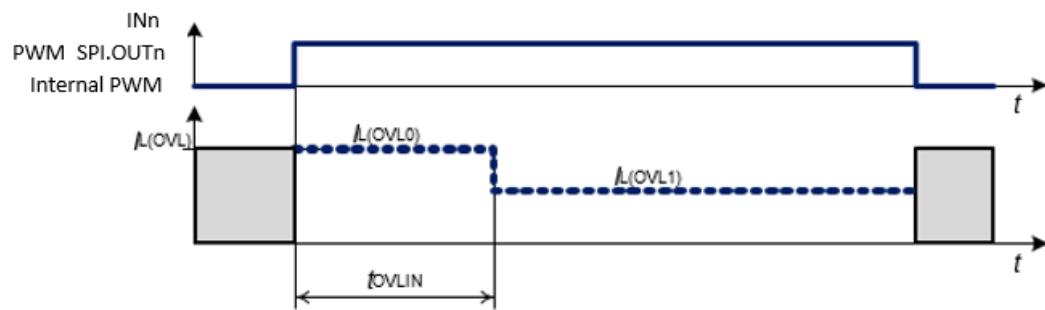

A time diagram is shown in Figure 11. The channel configured with BIM option can be either driven by an SPI command, PWM command (internal generator) or INn parallel input. Once programmed to "1" via SPI, the BIM.OUTn bit is set back to "0" at the end of BIM time ( $t_{BIM}$ ), unless a reset condition occurs (VDDIO\_uv, hardware or software reset): an eventual switch off of the channel commanded by the user has no impact on BIM.OUTn configuration.

Figure 11. Bulb inrush mode

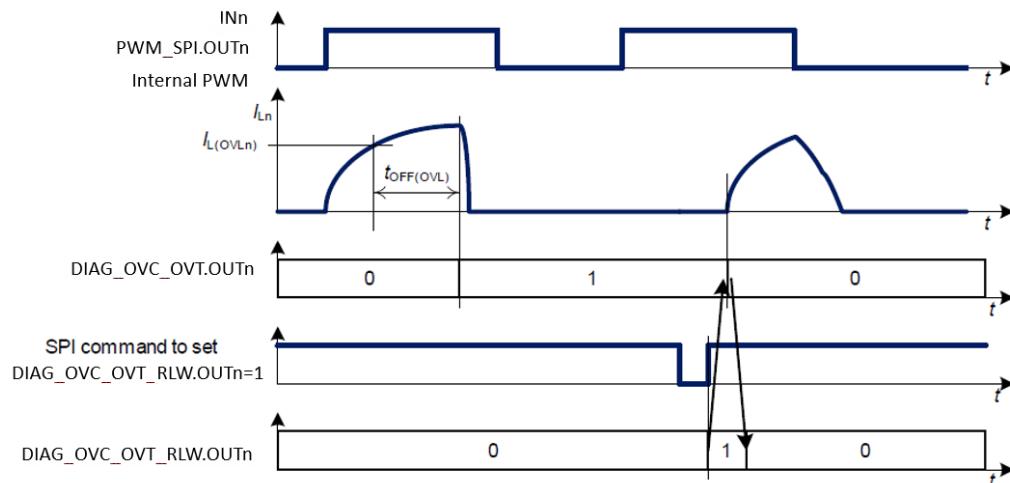

When BIM.OUTn are set to "1", eventual overcurrent/overtemperature conditions will flag DIAG\_OVC\_OVT.OUTn bit, but the affected channels will not be permanently switched OFF. Once asserted, eventual SPI attempt to clear DIAG\_OVC\_OVT.OUTn will be ignored, until the BIM counter is expired. In order to resume the normal behavior when the BIM counter is expired, the DIAG\_OVC\_OVT.OUTn shall be cleared in order to allow IC to perform open load ON diagnosis.

An internal timer set the bit BIM.OUTn back to "0" after 40 ms (parameter  $t_{BIM}$ ) starting from the first overcurrent event latched to prevent an excessive thermal stress to the channel, especially in case of short circuit at the output.

## 7.4

## PWM generators

Device has two independent PWM generators, which are defined as "PWM GEN" and "PWM LED" here below. These can be assigned to one or more channels, and can be programmed with different duty cycles and frequencies. Both refer to the same base frequency  $f_{INT}$  (8 MHz typ) even if two separate pre-scalers can be defined.

### 7.4.1

#### PWM GEN

The first PWM generator is called PWM GEN. Its frequency pre-scaler can be adjusted using CFG\_1.PWM\_DIV\_GEN bits to program target frequency and using CFG\_2.FR\_ADJ bits to modulate fine adjustments around the target. Configuration of fine adjustment is described in Table 11 while target frequency setting is reported in Table 12.

Table 11. Adjustment coefficients

| CFG_2.FR_ADJ    | Absolute delta to $f_{INT}$ divider |

|-----------------|-------------------------------------|

| 00 <sub>B</sub> | 0 %                                 |

| CFG_2.FR_ADJ    | Absolute delta to $f_{INT}$ divider |

|-----------------|-------------------------------------|

| 01 <sub>B</sub> | -15 %                               |

| 10 <sub>B</sub> | +15 %                               |

| 11 <sub>B</sub> | 0 %                                 |

The user can set the following parameters to configure the PWM generator:

- duty cycle (bits PWM\_GEN\_DC.DUTY\_CYCLE)

- 8 configuration bits are available, with 100/255 duty cycle resolution for each LSB

- The maximum duty cycle achievable is 100% (PWM\_GEN\_DC.DUTY\_CYCLE set to “11111111B”)

- In case the duty cycle is changed, the next target is applied once the previous PWM period is over and the new one is started. Once a new target is programmed, the behavior above is valid also if the current duty is 100% while when the current duty is 0% the new target value is applied immediately.

- frequency (bits CFG\_1.PWM\_DIV\_GEN)

- 2 configuration bits are available to select the frequency among 4 target values

**Table 12. PWM GEN generator available frequencies**

| CFG_1.PWM_DIV_GEN | PWM frequency |

|-------------------|---------------|

| 00 <sub>B</sub>   | 122.5 Hz      |

| 01 <sub>B</sub>   | 245.1 Hz      |

| 10 <sub>B</sub>   | 490.2 Hz      |

| 11 <sub>B</sub>   | 980.4 Hz      |

- Channels driven by PWM GEN (PWM\_SEL and PWM\_MAP registers)

The correct sequence to use the PWM generator is:

- define the frequency divider through CFG\_1.PWM\_DIV\_GEN bit.

- define duty cycle control register through PWM\_GEN\_DC register.

- set up channel output control through PWM\_SEL register (PWM GEN corresponds to 0)

- define channels driven by PWM selected in PWM\_SEL through mapping register PWM\_MAP

In order to clarify how to select the source that can drive the channels command, the driving tree with all possible sources (ie PWM generators, SPI and parallel inputs) is reported in [Figure 12](#).

Figure 12. Driving tree

#### 7.4.2 PWM LED

The second PWM generator is named PWM LED. Its frequency prescaler can be adjusted using CFG\_2.PWM\_DIV\_LED bits (see Table 13) while the modulation around the defined target is actually shared with PWM GEN, using CFG\_2.FR\_ADJ bits described in Table 11.

The user can set the following parameters to configure the PWM generator:

- duty cycle (bits PWM\_LED\_DC.DUTY\_CYCLE)

- 8 configuration bits are available, with 100/255 duty cycle resolution for each LSB

- The maximum duty cycle achievable is 100% (PWM\_LED\_DC.DUTY\_CYCLE set to "1111111B")

- In case the duty cycle is changed, the next target is applied once the previous PWM period is over and the new one is started. Once a new target is programmed, the behavior above is valid also if the current duty is 100% while when the current duty is 0% the new target value is applied immediately.

- frequency (bits CFG\_1.PWM\_DIV\_LED)

- 2 configuration bits are available to select the frequency among 4 target values

**Table 13. PWM LED generator available frequencies**

| CFG_2.PWM_DIV_LED | PWM frequency |

|-------------------|---------------|

| 00 <sub>B</sub>   | 122.5 Hz      |

| 01 <sub>B</sub>   | 245.1 Hz      |

| 10 <sub>B</sub>   | 490.2 Hz      |

| 11 <sub>B</sub>   | 980.4 Hz      |

- Channels driven by PWM LED (PWM\_SEL and PWM\_MAP registers)

The correct sequence to use the PWM LED generator is:

- define the frequency divider through CFG\_1.PWM\_LED\_GEN bit.

- define duty cycle control register through PWM\_LED\_DC register.

- set up channel output control through PWM\_SEL register (PWM LED corresponds to 0)

- define channels driven by PWM selected in PWM\_SEL through mapping register PWM\_MAP

## 7.5

## Power stages electrical specifications

3 V ≤ VDDIO ≤ 5.5 V; 6 ≤ VBATT ≤ 18 V; -40 °C ≤ T<sub>j</sub> ≤ 150 °C unless otherwise noted. All voltages are referred to GND pin.

**Table 14. Power stages electrical parameters**

| Parameter           | Description                                                                                     | Test condition                                                                                  | Min  | Typ  | Max                | Unit |

|---------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|--------------------|------|

| R <sub>DS(ON)</sub> | On-State Resistance                                                                             | T <sub>j</sub> = 25 °C                                                                          | -    | 0.75 | -                  | Ω    |

| R <sub>DS(ON)</sub> | On-State Resistance                                                                             | T <sub>j</sub> = 150 °C; I <sub>L</sub> = 100 mA                                                | -    | -    | 1.5                | Ω    |

| I <sub>L(NOM)</sub> | Nominal load current (all channels active)                                                      | T <sub>j</sub> ≤ 150 °C; Design info                                                            | -    | 260  | 500                | mA   |

| E <sub>AS</sub>     | Maximum energy dissipation single pulse                                                         | T = 25 °C, IL = 2XIL(EAR)                                                                       | -    | -    | 50                 | mJ   |

| E <sub>AS</sub>     | Maximum energy dissipation single pulse                                                         | T = 150 °C, IL = 400 mA                                                                         | -    | -    | 25                 | mJ   |

| I <sub>L(EAR)</sub> | Load current for maximum energy dissipation – repetitive (all channels active)                  | T <sub>j</sub> ≤ 150 °C; Design info                                                            | -    | 220  | -                  | mA   |

| E <sub>AR</sub>     | Maximum energy dissipation repetitive pulses - 2*I <sub>L(EAR)</sub> (two channels in parallel) | T <sub>j(0)</sub> = 85 °C; I <sub>L(0)</sub> = 2*I <sub>L(EAR)</sub> ; 2*10 <sup>6</sup> cycles | -    | -    | 15                 | mJ   |

| E <sub>AR</sub>     | Maximum energy dissipation repetitive pulses - I <sub>L(EAR)</sub>                              | T = 85 °C, 2*10 <sup>6</sup> cycles                                                             | -    | -    | 10                 | mJ   |

| V <sub>DS</sub>     | Voltage at power transistor                                                                     | -                                                                                               | -0.3 | -    | V <sub>D(CL)</sub> | V    |

| V <sub>D(CL)</sub>  | Drain to GND Output clamping voltage LS                                                         | I <sub>L</sub> = 10 mA; Low-Side Configuration                                                  | 45   | 47   | 49                 | V    |

| Parameter        | Description                                                                                           | Test condition                                                                                                                                                          | Min  | Typ | Max | Unit                   |

|------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------------------------|

| $V_{S(CL)}$      | Source to GND Output clamping voltage HS                                                              | $I_L = 10 \text{ mA}$ ; $V_{BATT} = V_{OUT\_Dn} = 7 \text{ V}$ ; High-Side Configuration                                                                                | -18  | -17 | -16 | V                      |

| $I_{L(OFF)}$     | Output leakage current (each channel)<br>$T_J = 150 \text{ }^\circ\text{C}$                           | $V_{BATT} = 0 \text{ V}$ ; $V_{DDIO} = 0 \text{ V}$ ; $V_{SOURCE} = 0 \text{ V}$ ; $V_{DS} = 28 \text{ V}$ ; $T_J$ up to $150 \text{ }^\circ\text{C}$                   | -3   | 0   | 3   | $\mu\text{A}$          |

| $I_{L(OFF)\_HS}$ | Output leakage current (each channel)<br>$T_J = 150 \text{ }^\circ\text{C}$                           | $V_{BATT} = 28 \text{ V}$ ; $V_{DDIO} = 0 \text{ V}$ ; $V_{SOURCE} = 0 \text{ V}$ ; $V_{DS} = 28 \text{ V}$ ; $T_J$ up to $150 \text{ }^\circ\text{C}$ – High side case | -3   | -   | 3   | $\mu\text{A}$          |

| $I_{(OFF)\_HS}$  | Output current (each channel) in High side case                                                       | High side configuration, Power OFF, $V_{SOURCE} = 0 \text{ V}$                                                                                                          | -70  | -   | -30 | $\mu\text{A}$          |

| $I_{(OFF)\_HS}$  | Output current (each channel) in High side case                                                       | High side configuration, Power OFF, $V_{SOURCE} = 2.5 \text{ V}$                                                                                                        | -10  | -   | 10  | $\mu\text{A}$          |

| <b>Timing</b>    |                                                                                                       |                                                                                                                                                                         |      |     |     |                        |

| $t_{DELAY(ON)}$  | Turn-ON delay (from INn pin or bit to $V_{OUT} = 90\%$ VBATT) (Channels used as Low-Side)             | $RL = 50 \Omega$<br>$VBATT = 14 \text{ V}$<br>Active or Limp Home mode                                                                                                  | 3    | 5   | 7   | $\mu\text{s}$          |

| $t_{DELAY(OFF)}$ | Turn-OFF delay (from INn pin or bit to $V_{OUT} = 10\%$ VBATT) (Channels used as Low-Side)            | $RL = 50 \Omega$ ; $VBATT = 14 \text{ V}$ ; Active or Limp Home mode                                                                                                    | 2.5  | 10  | 21  | $\mu\text{s}$          |

| $t_{ON}$         | Turn-ON time (from INn pin or bit to $V_{OUT} = 10\%$ VBATT) (Channels used as Low-Side)              | $RL = 50 \Omega$ ; $VBATT = 14 \text{ V}$ ; Active or Limp Home mode                                                                                                    | 7    | 15  | 35  | $\mu\text{s}$          |

| $t_{OFF}$        | Turn-OFF time (from INn pin or bit to $V_{OUT} = 90\%$ VBATT) (Channels used as Low-Side)             | $RL = 50 \Omega$ ; $VBATT = 14 \text{ V}$ ; Active or Limp Home mode                                                                                                    | 4    | -   | 40  | $\mu\text{s}$          |

| $dV/dt_{ON}$     | Turn-ON slew rate $V_{DS} = 70\%$ to $30\%$ VBATT (Channels used as Low-Side)                         | $RL = 50 \Omega$ ; $VBATT = 14 \text{ V}$ ; Active or Limp Home mode                                                                                                    | 0.35 | 1   | 2.2 | $\text{V}/\mu\text{s}$ |

| $-dV/dt_{OFF}$   | Turn-OFF slew rate $V_{DS} = 30\%$ to $70\%$ VBATT (Channels used as Low-Side)                        | $RL = 50 \Omega$ ; $VBATT = 14 \text{ V}$ ; Active or Limp Home mode                                                                                                    | 0.15 | 1.3 | 3.4 | $\text{V}/\mu\text{s}$ |