## PRODUCT / PROCESS CHANGE NOTIFICATION

### 1. PCN basic data

|                      |                                                                                   |                                                                                 |

|----------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 1.1 Company          |  | STMicroelectronics International N.V                                            |

| 1.2 PCN No.          |                                                                                   | ADG/21/12576                                                                    |

| 1.3 Title of PCN     |                                                                                   | SPC584BxxE1xx (FC70): Activation of Muar as Assembly and Final Testing Location |

| 1.4 Product Category |                                                                                   | see list                                                                        |

| 1.5 Issue date       |                                                                                   | 2021-02-02                                                                      |

### 2. PCN Team

|                           |                          |

|---------------------------|--------------------------|

| 2.1 Contact supplier      |                          |

| 2.1.1 Name                | ROBERTSON HEATHER        |

| 2.1.2 Phone               | +1 8475853058            |

| 2.1.3 Email               | heather.robertson@st.com |

| 2.2 Change responsibility |                          |

| 2.2.1 Product Manager     | Luca RODESCHINI          |

| 2.2.2 Marketing Manager   | Matteo MOIOLI            |

| 2.2.3 Quality Manager     | Alberto MERVIC           |

### 3. Change

| 3.1 Category | 3.2 Type of change                                                                                                                              | 3.3 Manufacturing Location |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Transfer     | Line transfer for a full process or process brick (process step, control plan, recipes) from one site to another site: Assembly site (SOP 2617) | ST Muar - Malaysia         |

### 4. Description of change

|                                                                                       | Old                                                    | New                                                                 |

|---------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------|

| 4.1 Description                                                                       | ST Kirkop-Malta as Assembly and Final Testing Location | ST Kirkop-Malta and ST Muar as Assembly and Final Testing Locations |

| 4.2 Anticipated Impact on form,fit, function, quality, reliability or processability? | No Impact                                              |                                                                     |

### 5. Reason / motivation for change

|                      |                   |

|----------------------|-------------------|

| 5.1 Motivation       | Capacity Increase |

| 5.2 Customer Benefit | CAPACITY INCREASE |

### 6. Marking of parts / traceability of change

|                 |                               |

|-----------------|-------------------------------|

| 6.1 Description | Dedicated Finished Good Codes |

|-----------------|-------------------------------|

### 7. Timing / schedule

|                                     |              |

|-------------------------------------|--------------|

| 7.1 Date of qualification results   | 2021-03-31   |

| 7.2 Intended start of delivery      | 2021-04-30   |

| 7.3 Qualification sample available? | Upon Request |

### 8. Qualification / Validation

|                                                    |             |

|----------------------------------------------------|-------------|

| 8.1 Description                                    |             |

| 8.2 Qualification report and qualification results | In progress |

### 9. Attachments (additional documentations)

|                          |

|--------------------------|

| 12576 Public product.pdf |

| 12576 Details.pdf        |

| 10. Affected parts      |                         |                          |

|-------------------------|-------------------------|--------------------------|

| 10. 1 Current           |                         | 10.2 New (if applicable) |

| 10.1.1 Customer Part No | 10.1.2 Supplier Part No | 10.1.2 Supplier Part No  |

|                         | SPC584B70E1NHC0X        |                          |

**IMPORTANT NOTICE – PLEASE READ CAREFULLY**

Subject to any contractual arrangement in force with you or to any industry standard implemented by us, STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics – All rights reserved

## Public Products List

Public Products are off the shelf products. They are not dedicated to specific customers, they are available through ST Sales team, or Distributors, and visible on ST.com

**PCN Title :** SPC584BxxE1xx (FC70): Activation of Muar as Assembly and Final Testing Location

**PCN Reference :** ADG/21/12576

**Subject :** Public Products List

Dear Customer,

Please find below the Standard Public Products List impacted by the change.

|                  |                  |                  |

|------------------|------------------|------------------|

| SPC584B60E1EG00X | SPC584B70E1NHC0X | SPC584B70E1EDC0X |

| SPC584B64E1NH00X |                  |                  |

### **IMPORTANT NOTICE – PLEASE READ CAREFULLY**

Subject to any contractual arrangement in force with you or to any industry standard implemented by us, STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics – All rights reserved

## PRODUCT/PROCESS CHANGE NOTIFICATION

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>TITLE</b>              | <b>SPC584BxxE1xx (FC70): Activation of Muar as Assembly and Final Testing Location</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>IMPACTED PRODUCTS</b>  | <p>ST silicon line FC70 assembled in TQFP 64 10x10x1.0 Exposed Pad Package:</p> <ul style="list-style-type: none"> <li>• SPC584B60E1EG00X</li> <li>• SPC584B64E1DD00X</li> <li>• SPC584B64E1NH00X</li> <li>• SPC584B70E1ED01X</li> <li>• SPC584B70E1EDC0X</li> <li>• SPC584B70E1EH00X</li> <li>• SPC584B70E1NHC0X</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

| <b>MANUFACTURING STEP</b> | Assembly and Electrical Final Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>INVOLVED PLANT</b>     | ST Muar (Malaysia)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>CHANGE REASON</b>      | Capacity Increase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>CHANGE DESCRIPTION</b> | <p>ST Muar will be activated for Assembly and electrical Final Test</p> <p>Assembly transfer includes specific product's improvements linked to new solutions and processes availability, such as:</p> <ul style="list-style-type: none"> <li>• <b>Package Bill of Material:</b><br/>move to High Density (HD) leadframe (different supplier)<br/>move to 0.7mil wires diameter</li> <li>• <b>Molding Process:</b><br/>move to central top gate resin injection<br/>move to new molding compound (Sumitomo EME-G700SLS)</li> <li>• <b>Marking: re-layout and addition of 2D identifier.</b></li> </ul> <p>Final Test transfer does not concern changes in test flow or equipment</p> |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

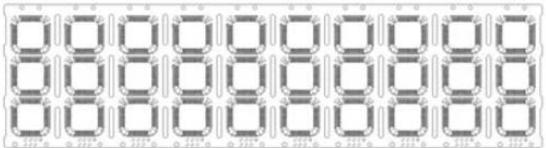

|                     | <p>As far as assembly is concerned, additional details are here below provided.</p> <p>High Density (HD) Leadframe: increased number of units per strip, from 30 to 64 units/strip.</p> <div style="display: flex; justify-content: space-between;"> <div style="width: 45%;"> <p>Standard Frame 3x10<br/>(30 units/strip)</p>  </div> <div style="width: 45%;"> <p>High Density 4x16<br/>(64 units/strip)</p>  </div> </div> <p>Unit level drawing (pad size, etc.) remains unchanged.</p> <p><b>Central Top Gate Mold Injection:</b> reduces stress and possible wire sweeping during molding process</p> <p><b>2D Marking:</b> improves product's internal traceability.</p> <p>Both changes are visible on package as shown:</p> <div style="display: flex; justify-content: space-around;"> <div style="text-align: center;"> <p><b>Malta</b></p>  </div> <div style="text-align: center;"> <p><b>Muar</b></p>  </div> </div> <p>Muar: Central Top Gate is visible at package's center<br/>2D Marking positioned at right top corner</p> |

| <b>TRACEABILITY</b> | New Finished Good (internal part number) code and Date Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       |                                                                                                                                 |    |   |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|----|---|

| <b>VALIDATION</b>     | Validation report included in this communication based on ZVEI (AEC-Q100/Q006) recommendations reported in the following table: |    |   |

| SEM-PA-08             | Change of wire bonding                                                                                                          | P  | P |

| SEM-PA-11             | Change of mold compound / encapsulation material                                                                                | P  | P |

| SEM-PA-13             | Change of product marking                                                                                                       | I  | P |

| SEM-PA-16             | Change of direct material supplier                                                                                              | -- | P |

| SEM-PA-18             | Move all or parts of production to a different assembly site.                                                                   | P  | P |

| SEM-PA-21             | Molding / Encapsulation process                                                                                                 | -- | P |

|                       | <b>PACKING/SHIPPING</b>                                                                                                         |    |   |

|                       | <b>EQUIPMENT</b>                                                                                                                |    |   |

|                       | <b>TEST FLOW</b>                                                                                                                |    |   |

|                       | SEM-TF-01 Move of all or part of electrical wafer test and/or final test to a different test site.                              | P  | P |

| <b>IMPLEMENTATION</b> | Change will be implemented upon customer approval                                                                               |    |   |

| <b>REPORT</b>         | Validation report will be provided within March 2021<br>Here enclosed the qualification Plan                                    |    |   |

# Preliminary Reliability Report

## Chorus2M eTQFP64 Muar Assy

### M40

*FAB transfer*

| General Information        |          | Locations                                                                                                                                         |           |

|----------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Product Line               | FC70     | Wafer fab location                                                                                                                                | Crolles 2 |

| Product Description        | Chorus2M | Final Assessment                                                                                                                                  |           |

| Product Group              | ADG      | Reliability trials on Chorus2M eTQFP64 assembled in Muar completed up to Q100 milestone with positive results. Extension required by Q006 ongoing |           |

| Product division           | ADS      | Reliability assessment                                                                                                                            |           |

| Silicon process technology | CMOS M40 |                                                                                                                                                   |           |

## DOCUMENT HISTORY

| Version | Date       | Author     | Comment                            |

|---------|------------|------------|------------------------------------|

| 1.0     | 19/01/2021 | P.Epigrafi | First release. Preliminary results |

## RELEASED DOCUMENT

## TABLE OF CONTENTS

|                                                               |           |

|---------------------------------------------------------------|-----------|

| <b>1 RELIABILITY EVALUATION OVERVIEW.....</b>                 | <b>3</b>  |

| 1.1 OBJECTIVES .....                                          | 3         |

| 1.2 CONCLUSIONS .....                                         | 3         |

| 1.3 WAFER FAB INFORMATION .....                               | 4         |

| 1.4 PACKAGE OUTLINE/MECHANICAL DATA .....                     | 4         |

| 1.5 FINAL TESTING INFORMATION:.....                           | 4         |

| <b>2 RELIABILITY PLAN AND TESTS RESULTS .....</b>             | <b>5</b>  |

| 2.1 CONDITIONS .....                                          | 5         |

| 2.2 TABLES ENTRY LEGEND .....                                 | 5         |

| 2.3 ACCELERATED ENVIRONMENTAL STRESS TEST (Q100 GROUP A)..... | 5         |

| 2.4 ACCELERATED LIFETIME SIMULATION TEST (Q100 GROUP B).....  | 8         |

| 2.5 PACKAGE ASSEMBLY INTEGRITY TEST (Q100 GROUP C).....       | 11        |

| 2.6 DIE FABRICATION RELIABILITY TEST (Q100 GROUP D) .....     | 11        |

| 2.7 ELECTRICAL VERIFICATION TEST (Q100 GROUP E) .....         | 12        |

| 2.8 DEFECT SCREENING TEST (Q100 GROUP F).....                 | 13        |

| <b>3 REVISION TRACKING.....</b>                               | <b>14</b> |

## 1 RELIABILITY EVALUATION OVERVIEW

### 1.1 Objectives

Aim of this document is to report the preliminary reliability trials results for Chorus2M Cut1.2 eTQFP64 assy transfer from Malta to Muar.

Chorus2M eTQFP64 product diffused in Crolles and assembled in Malta is in mass production since 2018.

Purpose of the change is to transfer Back End site from ST Malta to ST Muar plant. Assembly transfer includes specific product improvements linked to new solutions and processes availability, such as:

- Package Bill of Material:

- o change from standard matrix to High Density (HD) matrix leadframe (different supplier) with increased number of units per strip. Unit level drawing (pad size, etc.) remains unchanged

- o change wire diameter from 0.8mils to 0.7mils

- o change of molding compound

- Molding Process: change to central top gate resin injection with the purpose to reduce stress and wire sweeping during molding process.

Qualification of Chorus2M eTQFP64 assembled in Muar takes similarities with Chorus4M eTQFP64 assembled in Muar.

BOM comparison between Malta and Muar assy is reported in table at paragraph 1.4.

Assy reports are available for all qualification lots.

The qualification exercise for this change is in line with ZVEI Delta Qualification Matrix (ESD CDM performed in addition to ZVEI Requirements according to internal common practice) and it is in respect of AEC-Q100 rev.H and AEC-Q006 rev.A for copper wire qualification.

### 1.2 Conclusions

Preliminary results of reliability trials are presented.

AEC-Q100 rev. H milestone has been positively achieved on Chorus2M eTQFP64 assembled in Muar.

Reliability trials are still ongoing to reach AEC-Q006 rev.A milestone.

### 1.3 Wafer fab information

| DIE FEATURES            |                |

|-------------------------|----------------|

| Product Code            | FC70           |

| Diffusion Site          | Crolles 2      |

| Wafer Diameter (inches) | 12             |

| Process Technology      | CMOS M40       |

| Passivation             | PSG + Nitride  |

| Die finishing back side | Lapped Silicon |

### 1.4 Package outline/Mechanical data

|                                      | Chorus2M<br>eTQFP64 Malta Assy    | Chorus2M<br>eTQFP64 Muar Assy      | Chorus4M<br>eTQFP64 Muar Assy      |

|--------------------------------------|-----------------------------------|------------------------------------|------------------------------------|

| Package Description                  | TQFP-EP 64 10X10X1.0<br>ExpadDown | TQFP-EP 64L 10X10X1.0<br>ExpadDown | TQFP-EP 64L 10X10X1.0<br>ExpadDown |

| Assembly Site                        | ST KIRKOP – MALTA                 | ST MUAR                            | ST MUAR                            |

| Die Attach material                  | QMI9507                           | QMI9507                            | QMI9507                            |

| Molding compound                     | G700LS                            | G700SLS                            | G700SLS                            |

| Substrate/Leadframe                  | Standard Pre-plated               | HD Pre-plated                      | HD Pre-plated                      |

| Wires bonding<br>materials/diameters | Cu 0.8mil                         | Cu 0.7mil                          | Cu 0.7mil                          |

### 1.5 Final testing information:

| PACKAGE FEATURES                             |                      |

|----------------------------------------------|----------------------|

| Electrical Testing<br>manufacturing location | : ST MUAR / ST MALTA |

| Tester                                       | : Teradyne J750      |

## 2 RELIABILITY PLAN AND TESTS RESULTS

### 2.1 Conditions

Room test temperature is 25°C

Hot test temperature is 150°C

Cold test temperature is -40°C

### 2.2 Tables entry legend

| Symbol                              | How to read                                                                           |

|-------------------------------------|---------------------------------------------------------------------------------------|

| <input type="checkbox"/>            | Action or condition has not to be considered                                          |

| <input checked="" type="checkbox"/> | The action/condition has been done/applied during the trial                           |

| N.P.                                | The trial or readout is not in the Qualification Plan and thus has not been performed |

| N.A.                                | Not applicable                                                                        |

| N.C.                                | Trial not completed yet                                                               |

### 2.3 Accelerated Environmental Stress Test (Q100 Group A)

| N  | TEST NAME              | CONDITIONS [SPEC]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Step     | Results eTQFP64                               | Notes                                                |

|----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------|------------------------------------------------------|

|    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                               |                                                      |

| A1 | Pre Conditioning MSL 3 | [J-STD-020]<br><input checked="" type="checkbox"/> Testing at Room<br><input checked="" type="checkbox"/> Testing at Hot<br><input checked="" type="checkbox"/> Testing at Cold<br><input checked="" type="checkbox"/> Sonoscan pre / post<br><input checked="" type="checkbox"/> WPT pre / post<br><input checked="" type="checkbox"/> WBS pre / post<br><input checked="" type="checkbox"/> Die visual inspection post trial<br><input checked="" type="checkbox"/> 100 Temperature Cycles<br><br>24h bake@125°C,<br>192h@30°C/60%RH<br>3x Reflow simulation<br>260°C Peak Temp | Pre/Post | 0/77 x 1<br><br>0/231 x 3<br>Chorus4M eTQFP64 | Similarities with Chorus4M eTQFP64 assembled in Muar |

# RELIABILITY REPORT

ADG – Q&R Digital

Products

RR000021\_01

Chorus2M eTQFP64 Muar-M40

|      |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                                              |                                                                  |  |

|------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------|------------------------------------------------------------------|--|

|      |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                                              |                                                                  |  |

| A2   | <b>THB</b><br>Temperature<br>Humidity Bias       | <p>[JESD22-A101/A110]</p> <p><input checked="" type="checkbox"/> After Jedec PC MSL3</p> <p><input checked="" type="checkbox"/> Testing at Room</p> <p><input checked="" type="checkbox"/> Testing at Hot</p> <p><input type="checkbox"/> Testing at Cold</p> <p><input checked="" type="checkbox"/> Sonoscan pre / post</p> <p><input checked="" type="checkbox"/> WPT pre / post</p> <p><input checked="" type="checkbox"/> WBS pre / post</p> <p><input checked="" type="checkbox"/> Visual Inspection</p> <p><input checked="" type="checkbox"/> Cross section</p> <p>Ta=85°C, 85%RH, 1000hrs<br/>2000hrs AEC-Q006</p> | <b>1000 hrs</b> | N.P.<br>0/77 x 3<br>Chorus4M<br>eTQFP64      | Similarities with<br>Chorus4M<br>eTQFP64<br>assembled in<br>Muar |  |

|      |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>2000hrs</b>  | N.P<br>N.C.<br>77 x 3<br>Chorus4M<br>eTQFP64 |                                                                  |  |

| A3.a | <b>THS</b><br>Temperature<br>Humidity<br>Storage | <p>[JESD22-A101/A110]</p> <p><input checked="" type="checkbox"/> After Jedec PC MSL3</p> <p><input checked="" type="checkbox"/> Testing at Room</p> <p><input type="checkbox"/> Testing at Hot</p> <p><input type="checkbox"/> Testing at Cold</p> <p><input checked="" type="checkbox"/> Sonoscan pre / post</p> <p><input checked="" type="checkbox"/> WPT pre / post)</p> <p><input checked="" type="checkbox"/> WBS pre / post</p> <p><input checked="" type="checkbox"/> Visual Inspection</p> <p><input checked="" type="checkbox"/> Cross section</p> <p>Ta=85°C, 85%RH, 1000hrs</p>                                | <b>2000 hrs</b> | N.P.                                         |                                                                  |  |

| A3.b | <b>AC</b><br>Autoclave                           | <p>[JESD22-A102/A118]</p> <p><input checked="" type="checkbox"/> After Jedec PC MSL3</p> <p><input checked="" type="checkbox"/> Testing at Room</p> <p><input type="checkbox"/> Testing at Hot</p> <p><input type="checkbox"/> Testing at Cold</p> <p><input checked="" type="checkbox"/> Sonoscan pre / post</p> <p><input checked="" type="checkbox"/> WPT pre / post</p> <p><input checked="" type="checkbox"/> WBS pre / post</p> <p><input checked="" type="checkbox"/> Visual Inspection</p> <p><input checked="" type="checkbox"/> Cross section</p> <p>P=2.08atm Ta=121°C,<br/>96hrs</p>                           | <b>96 hrs</b>   | N.P.<br>0/77 x 3<br>Chorus4M<br>eTQFP64      | Similarities with<br>Chorus4M<br>eTQFP64<br>assembled in<br>Muar |  |

**Auth:** P.Epigrafi

**Approved:** M.De Tomasi

**Date:** 19/01/2021

**Page:** 6 of 14

# RELIABILITY REPORT

ADG – Q&R Digital

Products

RR000021\_01

Chorus2M eTQFP64 Muar-M40

| A4 | <b>TC</b><br>Temperature<br>Cycling         | <p>[JESD22-A104]</p> <ul style="list-style-type: none"><li><input checked="" type="checkbox"/> After Jedec PC MSL3</li><li><input checked="" type="checkbox"/> Testing at Room</li><li><input checked="" type="checkbox"/> Testing at Hot</li><li><input checked="" type="checkbox"/> Testing at Cold</li><li><input checked="" type="checkbox"/> Sonoscan pre / post</li><li><input checked="" type="checkbox"/> WPT pre / post</li><li><input checked="" type="checkbox"/> WBS pre / post</li><li><input checked="" type="checkbox"/> Visual Inspection</li><li><input checked="" type="checkbox"/> Cross section</li></ul> <p>Ta=-55°C /+150 °C,<br/>1000cyc<br/>2000cyc AEC-Q006</p> | <b>1000cyc</b>  | 0/77 x 1<br>Chorus2M<br>eTQFP64<br><br>0/77 x 3<br>Chorus4M<br>eTQFP64   | Similarities with<br>Chorus4M<br>eTQFP64<br>assembled in<br>Muar |  |

|----|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------|------------------------------------------------------------------|--|

|    |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>2000cyc</b>  | N.C.<br>Chorus2M<br>eTQFP64<br><br>N.C.<br>77 x 3<br>Chorus4M<br>eTQFP64 |                                                                  |  |

| A5 | <b>PTC</b><br>Power<br>Temperature<br>Cycle | <p>[JESD22-A105]</p> <ul style="list-style-type: none"><li><input checked="" type="checkbox"/> After Jedec PC MSL3</li><li><input checked="" type="checkbox"/> Testing at Room</li><li><input checked="" type="checkbox"/> Testing at Hot</li><li><input checked="" type="checkbox"/> Testing at Cold</li></ul> <p>Ta=-40°C /+125 °C<br/>1000 cyc<br/>2000cyc AEC-Q006</p>                                                                                                                                                                                                                                                                                                               | <b>1000 cyc</b> | N.P.<br><br>0/45 x 1<br>Chorus4M<br>eTQFP64                              | Similarities with<br>Chorus4M<br>eTQFP64<br>assembled in<br>Muar |  |

|    |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>2000cyc</b>  | N.P.<br><br>N.C.<br>Chorus4M<br>eTQFP64                                  |                                                                  |  |

**Auth:** P.Epigrafi

**Approved:** M.De Tomasi

**Date:** 19/01/2021

**Page:** 7 of 14

**RELIABILITY REPORT**ADG – Q&R Digital

Products**RR000021\_01****Chorus2M eTQFP64 Muar-M40**

|  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |

**2.4 Accelerated Lifetime Simulation Test (Q100 Group B)**

| N    | TEST NAME                                   | CONDITIONS [SPEC]                                                                                                                                                                                                                                                                                                                                       | Step    | Results                                                          |  | Notes                                                            |

|------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------|--|------------------------------------------------------------------|

|      |                                             |                                                                                                                                                                                                                                                                                                                                                         |         | Lot 1                                                            |  |                                                                  |

| B1.a | <b>HTOL</b><br>High Temp.<br>Operating Life | [JESD22-A108]<br><br><input type="checkbox"/> After Jedec PC MSL3<br><input checked="" type="checkbox"/> After 1k W/E cyc @125°C<br><input checked="" type="checkbox"/> Testing at Room, Hot, Cold<br><input checked="" type="checkbox"/> Drift Analysis on Key parameters<br><br>Ta=125°C, VDD_HV=5.5V,<br>VDD_LV=1.44V<br>168hrs<br>(1000hrs monitor) | 168 hrs | N.P.<br><br>0/77 x 1<br>Chorus4M<br>eTQFP64<br>assembled in Muar |  | Similarities with<br>Chorus4M<br>eTQFP64<br>assembled in<br>Muar |

**Auth:** P.Epigrafi**Approved:** M.De Tomasi**Date:** 19/01/2021**Page:** 8 of 14

# RELIABILITY REPORT

ADG – Q&R Digital

Products

RR000021\_01

Chorus2M eTQFP64 Muar-M40

|       |                                             |                                                                                                                                                                                                                                                                                                                                                                                                             |                  |      |                                                                                                       |

|-------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-------------------------------------------------------------------------------------------------------|

| B1.b  | <b>LTOL</b><br>High Temp.<br>Operating Life | [JESD22-A108]<br><br><input type="checkbox"/> After Jedec PC MSL3<br><input checked="" type="checkbox"/> After 1k W/E cyc @125°C<br><input checked="" type="checkbox"/> Testing at Room, Hot, Cold<br><input checked="" type="checkbox"/> Drift Analysis on Key parameters<br><br>Ta=-40°C, VDD_LV=1.44V<br>1000hrs                                                                                         | <b>1000hrs</b>   | N.P. |                                                                                                       |

| B2    | <b>ELFR</b><br>Early Life<br>Failure Rate   | [AEC Q100-008]<br><br><input checked="" type="checkbox"/> Testing at Room, Hot<br>Ta= 125°C, Tj=150°C<br>BI+24 hrs                                                                                                                                                                                                                                                                                          | <b>BI +24hrs</b> | N.P. | Silicon stress trial, not<br>significant for<br>assembly changes.<br>Line Stress performed<br>instead |

| B3.1  | <b>HTDR</b><br>High Temp.<br>Data Retention | [AEC Q100-005]<br><br><input checked="" type="checkbox"/> After Jedec PC MSL3<br><input checked="" type="checkbox"/> Testing at Room<br><input type="checkbox"/> Testing at Hot<br><input type="checkbox"/> Testing at Cold<br><input checked="" type="checkbox"/> After 1k W/E cyc @125°C<br><input checked="" type="checkbox"/> Vth Drift Analysis<br><br>All0, Ta=150°C,<br>1000hrs (2000hrs monitoring) | <b>2000 hrs</b>  | N.P. |                                                                                                       |

| B3.2a | <b>FET @25°C</b>                            | [AEC Q100-005]<br><br><input checked="" type="checkbox"/> Testing at Room<br><input checked="" type="checkbox"/> Drift Analysis on Flash key<br>parameters at Room, Hot, Cold<br><br>Ta= 25°C<br>100k Write/Erase cyc                                                                                                                                                                                       | <b>100k cyc</b>  | N.P. |                                                                                                       |

| B3.2b | <b>HTDR<br/>After FET</b>                   | <input checked="" type="checkbox"/> Vth Drift Analysis<br>Ta= 150°C, All0 Pattern<br>168hrs                                                                                                                                                                                                                                                                                                                 | <b>168 hrs</b>   | N.P. |                                                                                                       |

| B3.3a | <b>FET @125°C</b>                           | [AEC Q100-005]<br><br><input checked="" type="checkbox"/> Testing at Room<br><input checked="" type="checkbox"/> Drift Analysis on Flash key<br>parameters at Room, Hot, Cold<br><br>Ta= 125°C<br>100k Write/Erase cyc                                                                                                                                                                                      | <b>100k cyc</b>  | N.P. |                                                                                                       |

| B3.3b | <b>HTDR<br/>After FET</b>                   | <input checked="" type="checkbox"/> Vth Drift Analysis<br>Ta= 150°C, All0 Pattern<br>168hrs                                                                                                                                                                                                                                                                                                                 | <b>168 hrs</b>   | N.P. |                                                                                                       |

Auth: P.Epigrafi

Approved: M.De Tomasi

Date: 19/01/2021

Page: 9 of 14

# RELIABILITY REPORT

ADG – Q&R Digital

Products

RR000021\_01

Chorus2M eTQFP64 Muar-M40

|       |                           |                                                                                                                                                                                                                     |                 |      |  |

|-------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|--|

| B3.4a | <b>FET @-40°C</b>         | [AEC Q100-005]<br><br><input checked="" type="checkbox"/> Testing at Room<br><input checked="" type="checkbox"/> Drift Analysis on Flash key parameters at Room, Hot, Cold<br><br>Ta= -40°C<br>100k Write/Erase cyc | <b>100k cyc</b> | N.P. |  |

| B3.4b | <b>HTDR<br/>After FET</b> | <input checked="" type="checkbox"/> Vth Drift Analysis<br>Ta= 150°C, All0 Pattern<br>168hrs                                                                                                                         | <b>168 hrs</b>  | N.P. |  |

| B3.5  | <b>Read Disturb</b>       | After 10 W/E cyc @125°C<br><br>Ta= 125°C; 4,5V Stress<br><1ppm after 6000hrs with ECC                                                                                                                               | <b>Final</b>    | N.P. |  |

| B3.6  | <b>Read Disturb</b>       | After 10k W/E cyc @125°C<br><br>Ta= 125°C; 4,5V Stress<br><1ppm after 1 sec with ECC                                                                                                                                | <b>Final</b>    | N.P. |  |

**Auth:** P.Epigrafi

**Approved:** M.De Tomasi

**Date:** 19/01/2021

**Page:** 10 of 14

## 2.5 Package Assembly Integrity Test (Q100 Group C)

| N  | Test                            |                                                                                                   | Step         | Results |             |

|----|---------------------------------|---------------------------------------------------------------------------------------------------|--------------|---------|-------------|

|    | TEST NAME                       | CONDITIONS [SPEC]                                                                                 |              | eTQFP64 |             |

| C1 | <b>WBS</b><br>Wire Bond Shear   | [AEC Q100-001]<br>At appropriate time interval for each bonder to be used<br>30 bonds x 5 devices | Final result | Passed  | Assy Report |

| C2 | <b>WBP</b><br>Wire Bond Pull    | [MIL-STD883 method 2011]<br>30 bonds x 5 devices                                                  | Final result | Passed  | Assy Report |

| C3 | <b>SD</b><br>Solderability      | [JEDEC JEDES22-B102]<br>> 95% lead coverage                                                       | Final result | Passed  | Assy Report |

| C4 | <b>PD</b><br>Physical Dimension | [JEDEC JEDES22-B100 and B108]                                                                     | Final result | Passed  | Assy Report |

| C5 | <b>SBS</b><br>Solder Ball Shear | [AEC Q100-010]                                                                                    | Final result | N.A.    |             |

| C6 | <b>LI</b><br>Lead Integrity     | [JEDEC JEDES22-B105]                                                                              | Final result | N.A.    |             |

## 2.6 Die Fabrication Reliability Test (Q100 Group D)

| N  | Test                                                 |                                                                                                                                | Step         | RESULTS | Notes                 |

|----|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------|---------|-----------------------|

|    | TEST NAME                                            | CONDITIONS                                                                                                                     |              |         |                       |

| D1 | <b>EM</b><br>Electromigration                        | The data, test method, calculation and internal criteria should be available to the customer upon request for new technologies | Final result | DONE    | Process qualification |

| D2 | <b>TDDB</b><br>Time Dependent Dielectric Breakdown   | The data, test method, calculation and internal criteria should be available to the customer upon request for new technologies | Final result | DONE    | Process qualification |

| D3 | <b>HCI</b><br>Hot Carrier Injection                  | The data, test method, calculation and internal criteria should be available to the customer upon request for new technologies | Final result | DONE    | Process qualification |

| D4 | <b>NBTI</b><br>Negative Bias Temperature Instability | The data, test method, calculation and internal criteria should be available to the customer upon request for new technologies | Final result | DONE    | Process qualification |

| D5 | <b>SM</b><br>Stress Migration                        | The data, test method, calculation and internal criteria should be available to the customer upon request for new technologies | Final result | DONE    | Process qualification |

**RELIABILITY REPORT**ADG – Q&R Digital

Products**RR000021\_01**

Chorus2M eTQFP64 Muar-M40

**2.7 Electrical Verification Test (Q100 Group E)**

| <b>Test</b> |                                                | <b>CONDITIONS<br/>[AEC Q100]</b>                                                                                                                                                                                                                                                                                                                      | <b>Step</b>             | <b>RESULTS</b>            | <b>Notes</b>          |

|-------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------|-----------------------|

| <b>N</b>    | <b>TEST NAME</b>                               |                                                                                                                                                                                                                                                                                                                                                       |                         |                           |                       |

| E2          | <b>ESD<br/>HBM</b>                             | HBM = 2kV                                                                                                                                                                                                                                                                                                                                             | <b>Final<br/>result</b> | N.P.                      |                       |

| E3          | <b>ESD<br/>CDM</b>                             | CDM = 500V / 750V<br>corner only                                                                                                                                                                                                                                                                                                                      | <b>Final<br/>result</b> | PASSED<br>0/3 per V level |                       |

| E4          | <b>LU</b>                                      | Current Injection<br>Power supply sequence<br>Oversupply on power<br>supply<br>@Room & Hot                                                                                                                                                                                                                                                            | <b>Final<br/>result</b> | N.P.                      |                       |

| E5          | <b>ED</b><br>Electrical<br>Distribution        | [AEC Q100-009]<br><input checked="" type="checkbox"/> Testing at Room<br><input checked="" type="checkbox"/> Testing at Hot<br><input checked="" type="checkbox"/> Testing at Cold                                                                                                                                                                    | <b>Final<br/>result</b> | DONE                      |                       |

| E6          | <b>FG</b><br>Fault Grading                     | [AEC Q100-007]<br>FG shall be = or > 90% for qual<br>units                                                                                                                                                                                                                                                                                            | <b>Final<br/>result</b> | DONE                      |                       |

| E7          | <b>CHAR</b><br>Characterization                | [AEC Q103]<br>Performed on new<br>technologies and part families.<br><input checked="" type="checkbox"/> Testing at Room<br><input checked="" type="checkbox"/> Testing at Hot<br><input checked="" type="checkbox"/> Testing at Cold                                                                                                                 | <b>Final<br/>result</b> | N.P.                      |                       |

| E9          | <b>EMC</b><br>Electromagnetic<br>Compatibility | [SAE J1752/3 – radiated<br>Emission]                                                                                                                                                                                                                                                                                                                  | <b>Final<br/>result</b> | N.P.                      |                       |

| E10         | <b>SC</b><br>Short Circuit<br>Characterization | [AEC Q100-012]<br>Applicable to all smart power<br>devices. This test and<br>statistical evaluation shall be<br>performed per agreement<br>between user and supplier on a<br>case-by-case basis.                                                                                                                                                      | <b>Final<br/>result</b> | N.A.                      |                       |

| E11         | <b>SER</b><br>Soft Error<br>Rate               | [JEDEC Un-accelerated:<br>JESD89-1 or Accelerated:<br>JESD89-2 & JESD89-3]<br><br>Applicable to devices with<br>memory sizes 1Mbit SRAM or<br>DRAM based cells. Either test<br>option (un-accelerated or<br>accelerated) can be performed,<br>in accordance to the<br>referenced specifications. This<br>test and its accept criteria is<br>performed | <b>Final<br/>result</b> | DONE                      | Process qualification |

| E12         | <b>LF</b><br>Lead (Pb) Free<br>[AEC Q005]      | /                                                                                                                                                                                                                                                                                                                                                     | /                       | YES                       |                       |

**Auth:** P.Epigrafi**Approved:** M.De Tomasi**Date:** 19/01/2021**Page:** 12 of 14

## 2.8 Defect Screening Test (Q100 Group F)

| Test |                                              |            | Step                | RESULTS     | Notes |

|------|----------------------------------------------|------------|---------------------|-------------|-------|

| N    | TEST NAME                                    | CONDITIONS |                     |             |       |

| F1   | <b>PAT</b><br>Process Average testing        | [AEC Q101] | <b>Final result</b> | IMPLEMENTED |       |

| F2   | <b>SBA</b><br>Statistical Bin/Yield Analysis | [AEC Q102] | <b>Final result</b> | IMPLEMENTED |       |

### **3 REVISION TRACKING**

Rev 1.0

1. First Release