## PRODUCT INFORMATION LETTER

---

PIL IPD-PWR/13/8048

Dated 07 Aug 2013

---

**Top metallization change from AlSiCu to AlCu on

products using 4925 DMOS technology**

|                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sales Type/product family label                                                              | See attached list                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Type of change                                                                               | Waferfab process change                                                                                                                                                                                                                                                                                                                                                                                                            |

| Reason for change                                                                            | Process rationalization                                                                                                                                                                                                                                                                                                                                                                                                            |

| Description                                                                                  | The change from AISiCu to AlCu top metallization has already been successfully implemented on several ST technologies. Usage of the same metal target on sputtering equipment will avoid changes of targets and consequently a longer equipment uptime and availability. The new metallization is in agreement with ST's standards and guarantees the same quality, reliability and electrical characteristics as the current one. |

| Forecasted date of implementation                                                            | 01-Nov-2013                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Forecasted date of samples for customer                                                      | 31-Jul-2013                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Forecasted date for <b>STMicroelectronics</b> change Qualification Plan results availability | 31-Jul-2013                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Involved ST facilities                                                                       | Catania                                                                                                                                                                                                                                                                                                                                                                                                                            |

## DOCUMENT APPROVAL

| Name                | Function          |

|---------------------|-------------------|

| Comola, Marco       | Marketing Manager |

| Juhel, Serge        | Product Manager   |

| Petralia, Francesco | Q.A. Manager      |

# Reliability Evaluation Report

SD3931-10

*Top metallization change from AlSiCu to AlCu on

4925 DMOS technology*

| General Information               |                                 | Locations                     |                      |

|-----------------------------------|---------------------------------|-------------------------------|----------------------|

| <b>Product Line</b>               | 4925                            | <b>Wafer fab</b>              | CATANIA              |

| <b>Product Description</b>        | HF/VHF/UHF N-channel<br>MOSFETs | <b>Assembly plant</b>         | BOUSKOURA B/E        |

| <b>P/N</b>                        | SD3931-10                       | <b>Reliability Lab</b>        | CTN Reliability Lab. |

| <b>Product Group</b>              | IPD                             | <b>Reliability assessment</b> | PASS.                |

| <b>Product division</b>           | POWER TRANSISTORS               |                               |                      |

| <b>Package</b>                    | M174                            |                               |                      |

| <b>Silicon Process technology</b> | DISCRETE                        |                               |                      |

## DOCUMENT INFORMATION

| Version | Date        | Pages | Prepared by | Approved by | Comment |

|---------|-------------|-------|-------------|-------------|---------|

| 1.0     | 30-Jul-2013 | 8     | A.Riciputo  | G.Presti    |         |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

## TABLE OF CONTENTS

|                                                   |          |

|---------------------------------------------------|----------|

| <b>1 APPLICABLE AND REFERENCE DOCUMENTS .....</b> | <b>3</b> |

| <b>2 GLOSSARY .....</b>                           | <b>3</b> |

| <b>3 RELIABILITY EVALUATION OVERVIEW .....</b>    | <b>3</b> |

| 3.1 OBJECTIVES .....                              | 3        |

| 3.2 CONCLUSION .....                              | 3        |

| <b>4 DEVICE CHARACTERISTICS .....</b>             | <b>4</b> |

| 4.1 DEVICE DESCRIPTION .....                      | 4        |

| 4.2 CONSTRUCTION NOTE .....                       | 4        |

| <b>5 TESTS RESULTS SUMMARY .....</b>              | <b>5</b> |

| 5.1 TEST VEHICLE .....                            | 5        |

| 5.2 TEST PLAN AND RESULTS SUMMARY .....           | 5        |

| <b>6 ANNEXES .....</b>                            | <b>6</b> |

| 6.1 DEVICE DETAILS .....                          | 6        |

| 6.2 TESTS DESCRIPTION .....                       | 8        |

## 1 APPLICABLE AND REFERENCE DOCUMENTS

| Document reference | Short description                                 |

|--------------------|---------------------------------------------------|

| <b>0061692</b>     | Reliability tests and criteria for qualifications |

|                    |                                                   |

## 2 GLOSSARY

|            |                   |

|------------|-------------------|

| <b>DUT</b> | Device Under Test |

| <b>SS</b>  | Sample Size       |

|            |                   |

## 3 RELIABILITY EVALUATION OVERVIEW

### 3.1 Objectives

AlCu top metal extension to all high voltage technologies.

### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. It is stressed that reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the ruggedness of the products and safe operation, which is consequently expected during their lifetime.

## 4 DEVICE CHARACTERISTICS

### 4.1 Device description

175W – 100V HF/VHF DMOS transistor.

### 4.2 Construction note

|                                           |                  | SD3931-10 |

|-------------------------------------------|------------------|-----------|

| <b>Wafer/Die fab. information</b>         |                  |           |

| Wafer fab manufacturing location          | CATANIA          |           |

| Process family                            | DMOS             |           |

| Die finishing back side                   | AuAs             |           |

| Die size                                  | 6220x3420 micron |           |

| Bond pad metallization layers             | AlCu             |           |

| <b>Wafer Testing (EWS) information</b>    |                  |           |

| Electrical testing manufacturing location | CATANIA          |           |

| <b>Assembly information</b>               |                  |           |

| Assembly site                             | BOUSKOURA B/E    |           |

| Package description                       | M174             |           |

| Die attach material                       | Au Eutectique    |           |

| Wires bonding materials                   | Al-Si            |           |

| <b>Final testing information</b>          |                  |           |

| Testing location                          | BOUSKOURA B/E    |           |

## 5 TESTS RESULTS SUMMARY

### 5.1 Test vehicle

| Lot # | Lot | Data Code | Trace Code   | Package | Product Line | Comments |

|-------|-----|-----------|--------------|---------|--------------|----------|

| 1     | 553 | 1251      |              |         |              |          |

| 2     | 556 |           | MAMI*20080YS | M174    | 4925         |          |

| 3     | 573 | 1321      |              |         |              |          |

### 5.2 Test plan and results summary

STAC150V2-350E

| Test                          | PC | Std ref.        | Conditions                | SS | Steps | Failure/SS |       |       | Note |

|-------------------------------|----|-----------------|---------------------------|----|-------|------------|-------|-------|------|

|                               |    |                 |                           |    |       | Lot 1      | Lot 2 | Lot 3 |      |

| <b>Die Oriented Tests</b>     |    |                 |                           |    |       |            |       |       |      |

| HTFB                          | N  | JESD22<br>A-108 | Ta = 175°C, Vbias = +20V  |    |       | 168 H      | 0/77  | 0/77  | 0/77 |

|                               |    |                 |                           |    |       | 500 H      | 0/77  | 0/77  | 0/77 |

|                               |    |                 |                           |    |       | 1000 H     | 0/77  | 0/77  | 0/77 |

| HTRB                          | N  | JESD22<br>A-108 | Ta = 175°C, Vbias = +200V |    |       | 168 H      | 0/77  | 0/77  | 0/77 |

|                               |    |                 |                           |    |       | 500 H      | 0/77  | 0/77  | 0/77 |

|                               |    |                 |                           |    |       | 1000 H     | 0/77  | 0/77  | 0/77 |

| HTSL                          | N  | JESD22<br>A-103 | Ta = 200°C                |    |       | 168 H      | 0/45  | 0/45  | 0/45 |

|                               |    |                 |                           |    |       | 500 H      | 0/45  | 0/45  | 0/45 |

|                               |    |                 |                           |    |       | 1000 H     | 0/45  | 0/45  | 0/45 |

| <b>Package Oriented Tests</b> |    |                 |                           |    |       |            |       |       |      |

| TC                            | N  | JESD22<br>A-104 | Ta = -65°C to 150°C       |    |       | 100 cy     | 0/77  | 0/77  | 0/77 |

|                               |    |                 |                           |    |       | 200 cy     | 0/77  | 0/77  | 0/77 |

|                               |    |                 |                           |    |       | 500 cy     | 0/77  | 0/77  | 0/77 |

## **6 ANNEXES**

### **6.1 Device details**

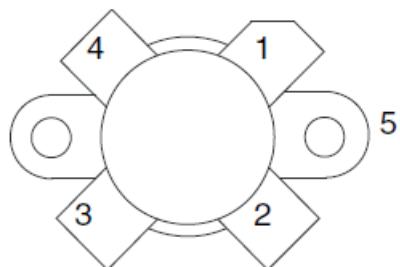

#### **6.1.1 Pin connection**

|           |           |

|-----------|-----------|

| 1. Drain  | 3. Gate   |

| 2. Source | 4. Source |

|           | 5. Source |

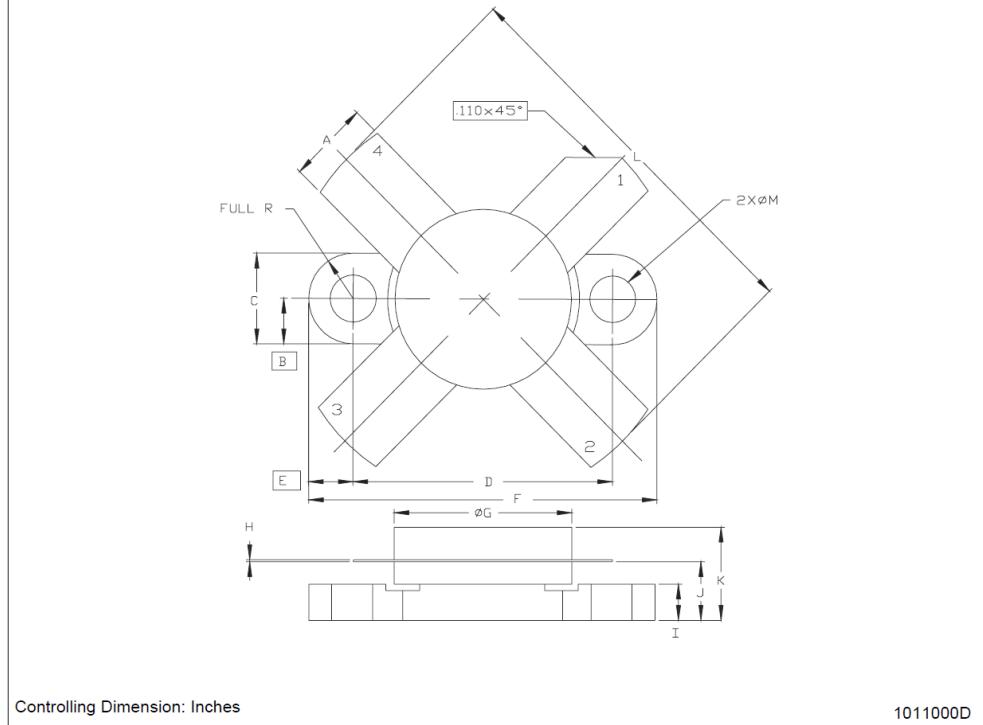

## 6.1.2 Package outline/Mechanical data

| Dim. | mm.   |      |       | Inch  |       |       |

|------|-------|------|-------|-------|-------|-------|

|      | Min   | Typ  | Max   | Min   | Typ   | Max   |

| A    | 5.56  |      | 5.584 | 0.219 |       | 0.230 |

| B    |       | 3.18 |       |       | 0.125 |       |

| C    | 6.22  |      | 6.48  | 0.245 |       | 0.255 |

| D    | 18.28 |      | 18.54 | 0.720 |       | 0.730 |

| E    |       | 3.18 |       |       | 0.125 |       |

| F    | 24.64 |      | 24.89 | 0.970 |       | 0.980 |

| G    | 12.57 |      | 12.83 | 0.495 |       | 0.505 |

| H    | 0.08  |      | 0.18  | 0.003 |       | 0.007 |

| I    | 2.11  |      | 3.00  | 0.083 |       | 0.118 |

| J    | 3.81  |      | 4.45  | 0.150 |       | 0.175 |

| K    |       |      | 7.11  |       |       | 0.280 |

| L    | 25.53 |      | 26.67 | 1.005 |       | 1.050 |

| M    | 3.05  |      | 3.30  | 0.120 |       | 0.130 |

Figure 9. Package dimensions

## 6.2 Tests Description

| Test name                                           | Description                                                                                                                                                                                                                                                                                     | Purpose                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Die Oriented</b>                                 |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                       |

| <b>HTRB</b><br>High Temperature Reverse Bias        | The device is stressed in static configuration, trying to satisfy as much as possible the following conditions:<br><ul style="list-style-type: none"><li>• low power dissipation;</li><li>• max. supply voltage compatible with diffusion process and internal circuitry limitations;</li></ul> | To determine the effects of bias conditions and temperature on solid state devices over time. It simulates the devices' operating condition in an accelerated way.                                                                                                                                                                    |

| <b>HTFB</b><br>High Temperature Forward (Gate) Bias |                                                                                                                                                                                                                                                                                                 | To maximize the electrical field across either reverse-biased junctions or dielectric layers, in order to investigate the failure modes linked to mobile contamination, oxide ageing, layout sensitivity to surface effects.                                                                                                          |

| <b>HTSL</b><br>High Temperature Storage Life        | The device is stored in unbiased condition at the max. temperature allowed by the package materials, sometimes higher than the max. operative temperature.                                                                                                                                      | To investigate the failure mechanisms activated by high temperature, typically wire-bonds solder joint ageing, data retention faults, metal stress-voiding.                                                                                                                                                                           |

| <b>Package Oriented</b>                             |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                       |

| <b>TC</b><br>Temperature Cycling                    | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                                                                                                                                                   | To investigate failure modes related to the thermo-mechanical stress induced by the different thermal expansion of the materials interacting in the die-package system. Typical failure modes are linked to metal displacement, dielectric cracking, molding compound delamination, wire-bonds failure, die-attach layer degradation. |

## Public Products List

PIL Title : Top metallization change from AlSiCu to AlCu on products using 4925 DMOS technology

PIL Reference : IPD-PWR/13/8048

PIL Created on : 31-JUL-2013

Subject : Public Products List

Dear Customer,

Please find below the Standard Public Products List impacted by the change:

### ST COMMERCIAL PRODUCT

SD3931-10

STAC3932B

SD3932

STAC3932F

SD3933

STAC3933

**Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

**UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND / OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE ( AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION ), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.**

**UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.**

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2013 STMicroelectronics - All rights reserved.

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

[www.st.com](http://www.st.com)