## Application Guide

## **Considerations:**

- Each port has 3 differential lanes of data (i.e. D0±, D1±, D2±) plus a clock (CLK±)

- → For HDMI 1.1-1.2 the throughput is a total of 4.95Gbps (1.65Gbps per lane)

- → For HDMI 1.3 the throughput is a total of 10.2Gbps (3.4Gbps per lane)

- To maintain the differential impedance per the HDMI Compliance Test Specification (and consequently signal integrity) a very low capacitance device must be used

- To maintain the differential impedance the designer should avoid using 90° angles and vias.

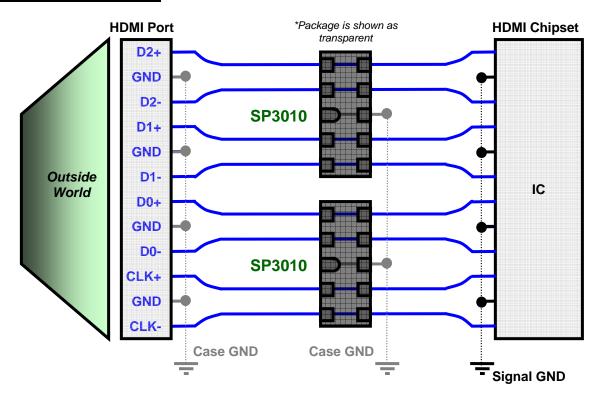

- → This can be accomplished by the use of an ESD device that offers a "straight-through" routing scheme

- Requires 8 channels of protection per port (D0±, D1±, D2±, CLK±)

- $\bullet$  The V<sub>CC</sub> pin on the SP3003-04ATG should be "NC" if backdrive is a concern. There is no V<sub>CC</sub> pin on the SP3010-04UTG.

## **Application Schematic:**

## **Recommended SPA Devices:**

| Ordering Number | ESD Level<br>(Contact) | I/O<br>Capacitance | # of Channels | V <sub>RWM</sub> | Packaging           |

|-----------------|------------------------|--------------------|---------------|------------------|---------------------|

| SP3010-04UTG    | ±8kV                   | 0.45pF             | 4             | 6V               | μDFN-10 (2.5x1.0mm) |

| SP3003-04ATG    | ±8kV                   | 0.65pF             | 4             | 6V               | MSOP-10             |

©2009 Littelfuse, Inc 8