# Intel® Atom™ Processor N400 & N500 Series

Datasheet- Volume 2

This is volume 2 of 2. Refer to Document Ref# 322847 for Volume 1

June 2011

Document Number: 322848-003

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Intel, [include any Intel trademarks which are used in this document] and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Go to: http://www.intel.com/products/processor%5Fnumber/

Enhanced Intel® SpeedStep Technology: See the Processor Spec Finder at http://processorfinder.intel.com or contact your Intel representative for more information.

Enabling Execute Disable Bit functionality requires a PC with a processor with Execute Disable Bit capability and a supporting operating system. Check with your PC manufacturer on whether your system delivers Execute Disable Bit functionality.

\*Other names and brands may be claimed as the property of others.

Copyright © 2009. Intel Corporation. All rights reserved.

# **Contents**

| 8 | Proc | essor Co | onfiguration Registers                                          | 10 |

|---|------|----------|-----------------------------------------------------------------|----|

|   | 8.1  | Registe  | er Terminology                                                  | 10 |

|   | 8.2  | _        | n Address Map                                                   |    |

|   |      | 8.2.1    | Legacy Address Range                                            |    |

|   |      | 8.2.2    | Main Memory Address Range (1 MB to TOLUD)                       |    |

|   |      | 8.2.3    | PCI Memory Address Range (TOLUD – 4 GB)                         |    |

|   |      | 8.2.4    | Graphics Memory Address Ranges                                  |    |

|   |      | 8.2.5    | System Management Mode (SMM)                                    |    |

|   |      | 8.2.6    | Memory Shadowing                                                |    |

|   |      | 8.2.7    | I/O Address Space                                               |    |

|   |      | 8.2.8    | Memory Controller Decode Rules and Cross-Bridge Address Mapping |    |

|   | 8.3  |          | sor Register Introduction                                       |    |

|   | 8.4  |          | pped Registers                                                  |    |

|   | 8.5  |          | vice 0                                                          |    |

|   | 0.0  | 8.5.1    | VID - Vendor Identification                                     |    |

|   |      | 8.5.2    | DID - Device Identification                                     |    |

|   |      | 8.5.3    | PCICMD - PCI Command                                            |    |

|   |      | 8.5.4    | PCISTS - PCI Status                                             |    |

|   |      | 8.5.5    | RID - Revision Identification                                   |    |

|   |      | 8.5.6    | CC - Class Code                                                 |    |

|   |      | 8.5.7    | MLT - Master Latency Timer                                      |    |

|   |      | 8.5.8    | HDR - Header Type                                               |    |

|   |      | 8.5.9    | SVID - Subsystem Vendor Identification                          |    |

|   |      |          | SID - Subsystem Identification                                  |    |

|   |      |          | CAPPTR - Capabilities Pointer                                   |    |

|   |      |          | PXPEPBAR - PCI Express Egress Port Base Address                 |    |

|   |      |          | MCHBAR - Processor Memory Mapped Register Range Base            |    |

|   |      |          | GGC - Processor Graphics Control Register                       |    |

|   |      |          | DEVEN - Device Enable                                           |    |

|   |      |          | PCIEXBAR - PCI Express Register Range Base Address              |    |

|   |      |          | DMIBAR - Root Complex Register Range Base Address               |    |

|   |      |          | PAMO - Programmable Attribute Map 0                             |    |

|   |      |          | PAM1 - Programmable Attribute Map 1                             |    |

|   |      |          | PAM2 - Programmable Attribute Map 2                             |    |

|   |      |          | PAM3 - Programmable Attribute Map 3                             |    |

|   |      |          | PAM4 - Programmable Attribute Map 4                             |    |

|   |      |          | PAM5 - Programmable Attribute Map 5                             |    |

|   |      |          | PAM6 - Programmable Attribute Map 6                             |    |

|   |      |          | LAC - Legacy Access Control                                     |    |

|   |      |          | REMAPBASE - Remap Base Address Register                         |    |

|   |      |          | REMAPLIMIT - Remap Limit Address Register                       |    |

|   |      |          | SMRAM - System Management RAM Control                           |    |

|   |      |          | ESMRAMC - Extended System Management RAM Control                |    |

|   |      |          | TOM - Top of Memory                                             |    |

|   |      |          | TOUUD - Top of Upper Usable DRAM                                |    |

|   |      |          | GBSM - Graphics Base of Stolen Memory                           |    |

|   |      |          | BGSM - Base of GTT Stolen Memory                                |    |

|   |      |          | TSEGMB - TSEG Memory Base                                       |    |

|   |      |          |                                                                 |    |

|     |        | TOLUD - Top of Low Usable DRAM                                |       |

|-----|--------|---------------------------------------------------------------|-------|

|     |        | ERRSTS - Error Status                                         |       |

|     | 8.5.37 | ERRCMD - Error Command                                        | 68    |

|     | 8.5.38 | SMICMD - SMI Command                                          | 69    |

|     | 8.5.39 | SKPD - Scratchpad Data                                        | 70    |

|     | 8.5.40 | CAPIDO - Capability Identifier                                | 70    |

| 8.6 | MCHBA  | .R                                                            | 74    |

|     | 8.6.1  | CHDECMISC - Channel Decode Misc                               | 75    |

|     | 8.6.2  | CODRBO – Channel O DRAM Rank Boundary Address O               | 76    |

|     | 8.6.3  | CODRB1 - Channel O DRAM Rank Boundary Address 1               |       |

|     | 8.6.4  | CODRB2 - Channel O DRAM Rank Boundary Address 2               |       |

|     | 8.6.5  | CODRB3 - Channel O DRAM Rank Boundary Address 3               |       |

|     | 8.6.6  | CODRAO1 - Channel O DRAM Rank 0,1 Attribute                   | 78    |

|     | 8.6.7  | CODRA23 - Channel O DRAM Rank 2,3 Attribute                   | 79    |

|     | 8.6.8  | COCYCTRKPCHG - Channel O CYCTRK PCHG                          | 80    |

|     | 8.6.9  | COCYCTRKACT - Channel O CYCTRK ACT                            | 81    |

|     | 8.6.10 | COCYCTRKWR - Channel O CYCTRK WR                              | 82    |

|     | 8.6.11 | COCYCTRKRD - Channel O CYCTRK READ                            | 83    |

|     | 8.6.12 | COCYCTRKREFR - Channel O CYCTRK REFR                          | 84    |

|     | 8.6.13 | COCKECTRL - Channel O CKE Control                             | 84    |

|     | 8.6.14 | COREFRCTRL - Channel O DRAM Refresh Control                   | 86    |

|     | 8.6.15 | COODTCTRL - Channel 0 ODT Control                             | 88    |

|     | 8.6.16 | COGTEW - Channel O Memory Controller Throttling Event Weights | 89    |

|     | 8.6.17 | COGTC - Channel O Memory Controller Throttling Control        | 90    |

|     | 8.6.18 | CODTPEW - Channel O DRAM Rank Throttling Passive Event        | 91    |

|     | 8.6.19 | CODTAEW - Channel O DRAM Rank Throttling Active Event         | 92    |

|     |        | CODTC - Channel O DRAM Throttling Control                     |       |

|     | 8.6.21 | TSC1 - Thermal Sensor Control 1                               | 95    |

|     | 8.6.22 | TSS - Thermal Sensor Status                                   | 97    |

|     |        | TR - Thermometer Read                                         |       |

|     |        | TSTTP - Thermal Sensor Temperature Trip Point                 |       |

|     | 8.6.25 | DACGIOCTRL1 - DAC/GPIO Control Register 1                     | . 100 |

|     | 8.6.26 | PMCFG - Power Management Configuration                        | . 100 |

|     | 8.6.27 | PMSTS - Power Management Status                               | . 102 |

| 8.7 | DMIBA  | R                                                             | . 103 |

|     | 8.7.1  | DMIVCECH - DMI Virtual Channel Enhanced Capability            |       |

|     | 8.7.2  | DMIPVCCAP1 - DMI Port VC Capability Register 1                | . 105 |

|     | 8.7.3  | DMIPVCCAP2 - DMI Port VC Capability Register 2                | . 105 |

|     | 8.7.4  | DMIPVCCTL - DMI Port VC Control                               | . 106 |

|     | 8.7.5  | DMIVCORCAP - DMI VCO Resource Capability                      |       |

|     | 8.7.6  | DMIVCORCTLO - DMI VCO Resource Control                        |       |

|     | 8.7.7  | DMIVCORSTS - DMI VCO Resource Status                          | . 108 |

|     | 8.7.8  | DMIVC1RCAP - DMI VC1 Resource Capability                      | . 109 |

|     | 8.7.9  | DMIVC1RCTL1 - DMI VC1 Resource Control                        |       |

|     |        | DMIVC1RSTS - DMI VC1 Resource Status                          |       |

|     | 8.7.11 | DMIRCLDECH - DMI Root Complex Link Declaration                | . 112 |

|     |        | DMI Element Self Description                                  |       |

|     |        | DMILE1D - DMI Link Entry 1 Description                        |       |

|     |        | DMILE1A - DMI Link Entry 1 Address                            |       |

|     |        | DMILE2D - DMI Link Entry 2 Description                        |       |

|     |        | DMILE2A - DMI Link Entry 2 Address                            |       |

|     |        | DMIRCILCECH - DMI Root Complex Internal Link Control          |       |

|     | 8.7.18 | DMILCAP - DMI Link Capabilities                               | . 117 |

|      | 8.7.19 | DMILCTL - DMI Link Control                        | 1 | 18 |

|------|--------|---------------------------------------------------|---|----|

|      |        | DMILSTS - DMI Link Status                         |   |    |

| 8.8  |        |                                                   |   |    |

|      | 8.8.1  | EPESD - EP Element Self Description               |   |    |

|      | 8.8.2  | EPLE1D - EP Link Entry 1 Description              |   |    |

|      | 8.8.3  | EPLE1A - EP Link Entry 1 Address                  |   |    |

|      | 8.8.4  | EPLE2D - EP Link Entry 2 Description              |   |    |

|      | 8.8.5  | EPLE2A - EP Link Entry 2 Address                  |   |    |

| 8.9  |        | vice 2 Function 0                                 |   |    |

| 0.7  | 8.9.1  | VID2 - Vendor Identification                      |   |    |

|      | 8.9.2  | DID - Device Identification                       |   |    |

|      | 8.9.3  | PCICMD2 - PCI Command                             |   |    |

|      | 8.9.4  | PCISTS2 - PCI Status                              |   |    |

|      |        |                                                   |   |    |

|      | 8.9.5  | RID2 - Revision Identification                    |   |    |

|      | 8.9.6  | CC - Class Code                                   |   |    |

|      | 8.9.7  | CLS - Cache Line Size                             |   |    |

|      | 8.9.8  | MLT2 - Master Latency Timer                       |   |    |

|      | 8.9.9  | HDR2 - Header Type                                |   |    |

|      |        | MMADR - Memory Mapped Range Address               |   |    |

|      |        | IOBAR - I/O Base Address                          |   |    |

|      |        | GMADR – Graphics Memory Range Address             |   |    |

|      |        | GTTADR - Graphics Translation Table Range Address |   |    |

|      |        | SVID2 - Subsystem Vendor Identification           |   |    |

|      |        | SID2 - Subsystem Identification                   |   |    |

|      |        | ROMADR - Video BIOS ROM Base Address              |   |    |

|      |        | CAPPOINT - Capabilities Pointer                   |   |    |

|      |        | INTRLINE - Interrupt Line                         |   |    |

|      |        | INTRPIN - Interrupt Pin                           |   |    |

|      |        | MINGNT - Minimum Grant                            |   |    |

|      |        | MAXLAT - Maximum Latency                          |   |    |

|      |        | MGGC - Processor Graphics Control Register        |   |    |

|      | 8.9.23 | DEVEN - Device Enable                             | 1 | 39 |

|      | 8.9.24 | SSRW - Software Scratch Read Write                | 1 | 40 |

|      | 8.9.25 | BSM - Base of Stolen Memory                       | 1 | 40 |

|      | 8.9.26 | HSRW - Hardware Scratch Read Write                | 1 | 41 |

|      | 8.9.27 | MC - Message Control                              | 1 | 41 |

|      | 8.9.28 | MA - Message Address                              | 1 | 42 |

|      |        | MD - Message Data                                 |   |    |

|      |        | GDRST – Graphics Debug Reset                      |   |    |

|      |        | PMCAPID - Power Management Capabilities ID        |   |    |

|      |        | PMCAP - Power Management Capabilities             |   |    |

|      |        | PMCS - Power Management Control/Status            |   |    |

|      |        | SWSMI - Software SMI                              |   |    |

|      |        | LBB - Legacy Backlight Brightness                 |   |    |

|      |        | ASLE – System Display Event Register              |   |    |

|      |        | ASLS – ASL Storage                                |   |    |

| 8.10 |        | vice 2 Function 1                                 |   |    |

| 5.10 |        | VID2 - Vendor Identification                      |   |    |

|      |        | DID2 - Device Identification                      |   |    |

|      |        | PCICMD2 - PCI Command                             |   |    |

|      |        | PCISTS2 - PCI Status                              |   |    |

|      |        | RID2 - Revision Identification                    |   |    |

|      |        |                                                   |   | 55 |

|      |        |                                                   |   |    |

Figure 8-3

Figure 8-4

Figure 8-5

|     |        | 8 10 7  | CLS - Cache Line Size                                       | 155 |

|-----|--------|---------|-------------------------------------------------------------|-----|

|     |        |         | MLT2 - Master Latency Timer                                 |     |

|     |        |         | HDR2 - Header Type                                          |     |

|     |        |         | DMMADR - Memory Mapped Range Address                        |     |

|     |        |         | 1SVID2 - Subsystem Vendor Identification                    |     |

|     |        |         | 2SID2 - Subsystem Identification                            |     |

|     |        |         | BROMADR - Video BIOS ROM Base Address                       |     |

|     |        |         | 4CAPPOINT - Capabilities Pointer                            |     |

|     |        |         | 5MINGNT - Minimum Grant                                     |     |

|     |        | 8.10.16 | 6MAXLAT - Maximum Latency                                   | 159 |

|     |        |         | 7 CAPIDO - Mirror of Device O Capability Identifier         |     |

|     |        |         | BMGGC - Mirror of Dev 0 processor Graphics Control Register |     |

|     |        |         | PDEVEN - Device Enable                                      |     |

|     |        | 8.10.20 | OSSRW - Mirror of Fun O Software Scratch Read Write         | 164 |

|     |        | 8.10.21 | 1 BSM - Mirror of FuncO Base of Stolen Memory               | 164 |

|     |        | 8.10.22 | 2HSRW - Mirror of Dev2 Func0 Hardware Scratch Read Write    | 165 |

|     |        | 8.10.23 | BPMCAPID - Mirror of Fun O Power Management Capabilities ID | 165 |

|     |        |         | 4PMCAP - Mirror of Fun O Power Management Capabilities      |     |

|     |        |         | 5PMCS - Power Management Control/Status                     |     |

|     |        | 8.10.26 | SSWSMI - Mirror of Func0 Software SMI                       | 168 |

|     |        | 8.10.27 | 7 ASLE - Mirror of Dev2 Func0 System Display Event Register | 168 |

|     |        | 8.10.28 | BASLS - ASL Storage                                         | 169 |

|     | 8.11   |         | 2 10                                                        |     |

|     |        | 8.11.1  | Index - MMIO Address Register                               | 170 |

|     |        | 8.11.2  | Data - MMIO Data Register                                   | 171 |

|     |        |         |                                                             |     |

|     |        |         |                                                             |     |

|     |        |         |                                                             |     |

| Ei~ | uroa   |         |                                                             |     |

| rig | ures   |         |                                                             |     |

|     | Figure | · 8-1   | System Address Ranges                                       | 14  |

|     | Figure |         | DOS Legacy Address Range                                    |     |

Main Memory Address Range......18

PCI Memory Address Range ......21

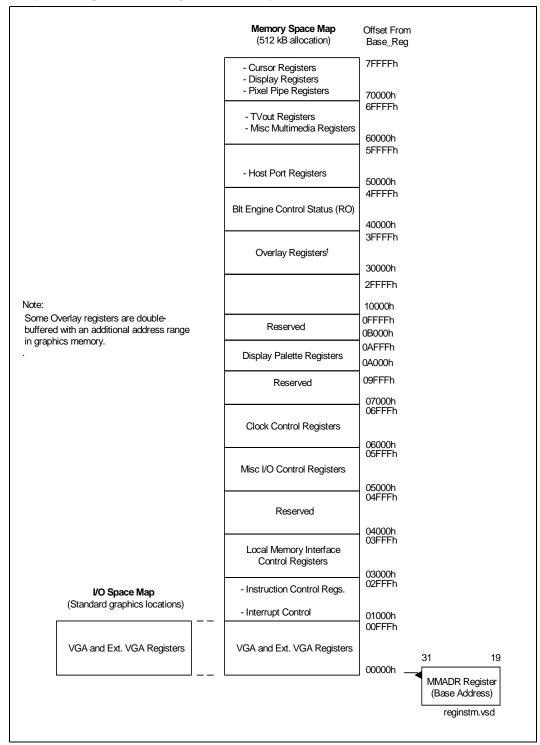

Graphics Register Memory and I/O Map ......24

# **Tables**

| Table 8-1  | Expansion Area Memory Segments                                      | 16    |

|------------|---------------------------------------------------------------------|-------|

| Table 8-2  | Extended System BIOS Area Memory Segments                           | 17    |

| Table 8-3  | System BIOS Area Memory Segments                                    | 17    |

| Table 8-4  | Pre-allocated Memory Example for 64-MB DRAM, 1-MB VGA, and 1-MB TSE | G.19  |

| Table 8-5  | SMM Space Definition Summary                                        | 26    |

| Table 8-6  | SMM Space Table                                                     | 26    |

| Table 8-7  | SMM Control Table                                                   | 27    |

| Table 8-8  | Device 0 Function 0 Register Summary                                | 30    |

| Table 8-9  | MCHBAR Register Summary                                             | 74    |

| Table 8-10 | EPBAR Register Summary                                              | . 119 |

| Table 8-11 | PCI Device 2 Function 0 Registers Summary                           | . 124 |

| Table 8-12 | PCI Device 2 Function 1 Register Summary                            | . 149 |

# **Revision History**

| Revision<br>Number | Description                                                   | Revision<br>Date |

|--------------------|---------------------------------------------------------------|------------------|

| 001                | Initial release                                               | December 2009    |

| 002                | Updated Section 1.6.6: Corrected the desription of CODRA[7:0] | April 2010       |

| 003                | Included the N500 series information                          | June 2011        |

§

# 8 Processor Configuration Registers

This is the volume-2 of Intel<sup>®</sup> Atom<sup>™</sup> Processor N400 & N500 Series Datasheet, and is intended to be distributed as part of the complete document. This document provides register information for Intel<sup>®</sup> Atom<sup>™</sup> Processor N400 & N500 Series.

Note:

Throughout this document,  $Intel^{\circledR}$  Atom<sup>TM</sup> Processor N400 & N500 Series is referred as the processor and  $Intel^{\circledR}$  NM10 Family Express Chipset is referred as the chipset.

# 8.1 Register Terminology

The following table shows the register-related terminology that is used in this document.

| Item     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RO       | <b>Read Only bit(s).</b> Writes to these bits have no effect. These are static values only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| RO-V     | Read Only/Volatile bit(s). Writes to these bits have no effect. These are status bits only. The value to be read may change based on internal events.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| RO-V-S   | Read Only/Volatile/Sticky bit(s). Writes to these bits have no effect. These are status bits only. The value to be read may change based on internal events. Bits are not returned to their default values by "warm" reset, but will be reset with a cold/complete reset.                                                                                                                                                                                                                                                                                                        |  |

| AF       | Atomic Flag bit(s). The first time the bit is read with an enabled byte, it returns the value 0, but a side-effect of the read is that the value changes 1. Any subsequent reads with enabled bytes return a 1 until a 1 is written the bit. When the bit is read, but the byte is not enabled, the state of the bit does not change, and the value returned is irrelevant, but will match the state of the bit.  When a 0 is written to the bit, there is no effect. When a 1 is written to the bits value becomes 0, until the next byte-enabled read. When the bit is written |  |

|          | but the byte is not enabled, there is no effect.  Conceptually, this is "Read to Set, Write 1 to Clear"                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| RW       | Read/Write bit(s). These bits can be read and written by software.  Hardware may only change the state of this bit by reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| RW1C     | Read/Write 1 to Clear bit(s). These bits can be read. Internal events may set this bit. A software write of 1 clears (sets to '0') the corresponding bit(s) and a write of 0 has no effect.                                                                                                                                                                                                                                                                                                                                                                                      |  |

| RW1C-L-S | Read/Write 1 to Clear/Lockable/Sticky bit(s). These bits can be read. Internal events may set this bit. A software write of 1 clears (sets to '0') the corresponding bit(s) and a write of 0 has no effect. Bits are not cleared by "warm" reset, but will be reset with a cold/complete reset. Additionally there is a Key bit (which is marked RW-K or RW-L-K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only/Volatile).                                                                                                           |  |

| Item     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RW1C-S   | Read/Write 1 to Clear/Sticky bit(s). These bits can be read. Internal events may set this bit. A software write of 1 clears (sets to 0) the corresponding bit(s) and a write of 0 has no effect. Bits are not cleared by "warm" reset, but will be reset with a cold/complete reset.                                                                                                                                                                            |  |

| RW-K     | Read/Write/Key bit(s). These bits can be read and written by software. Additionally this bit, when set, prohibits some other target bit field from being writeable (bit fields become Read Only).                                                                                                                                                                                                                                                               |  |

| RW-L     | Read/Write/Lockable bit(s). These bits can be read and written by software. Additionally there is a Key bit (which is marked RW-K or RW-L-K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only).                                                                                                                                                                                                                       |  |

| RW-L-K   | Read/Write/Lockable/Key bit(s). These bits can be read and written by software. This bit, when set, prohibits some other bit field(s) from being writeable (bit fields become Read Only). Additionally there is a Key bit (which is marked RW-K or RW-L-K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only).  Conceptually, this may be a cascaded lock, or it may be self-locking when in                           |  |

|          | its non-default state. When self-locking, it differs from RW-O in that writing back the default value will not set the lock.                                                                                                                                                                                                                                                                                                                                    |  |

| RW-V     | Write/Volatile bit(s). These bits can be read and written by software. Hardware may set or clear the bit based on internal events, possibly sooner than any subsequent software read could retrieve the value written.                                                                                                                                                                                                                                          |  |

| RW-V-L   | Read/Write/Volatile/Lockable bit(s). These bits can be read and written by software. Hardware may set or clear the bit based upon internal events, possibly sooner than any subsequent software read could retrieve the value written Additionally there is a bit (which is marked RW-K or RW-L-K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only).                                                                 |  |

| RW-V-L-S | Read/Write/Volatile/Lockable/Sticky bit(s). These bits can be read and written by software. Hardware may set or clear the bit based upon internal events, possibly sooner than any subsequent software read could retrieve the value written Additionally there is a bit (which is marked RW-K or RW-L-K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only). These bits return to their default values on cold reset. |  |

| RW-S     | <b>Read/Write/Sticky bit(s).</b> These bits can be read and written by software. Bits are not returned to their default values by "warm" reset, but will return to default values with a cold/complete reset.                                                                                                                                                                                                                                                   |  |

| RW-O     | Read/Write Once bit(s). Reads prior to the first write return the default value. The first write after warm reset stores any value written. Any subsequent write to this bit field is ignored. All subsequent reads return the first value written. The value returns to default on warm reset. If there are multiple RW-O or RW-O-S fields within a DWORD, they should be written all at once (atomically) to avoid capturing an incorrect value.              |  |

| Item   | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RW-O-S | Read/Write Once/Sticky bit(s). Reads prior to the first write return the default value. The first write after cold reset stores any value written. Any subsequent write to this bit field is ignored. All subsequent reads return the first value written. The value returns to default on cold reset. If there are multiple RW-O or RW-O-S fields within a DWORD, they should be written all at once (atomically) to avoid capturing an incorrect value. |  |

| W      | <b>Write-only.</b> These bits may be written by software, but will always return zeros when read. They are used for write side-effects. Any data written to these registers cannot be retrieved.                                                                                                                                                                                                                                                          |  |

| W1C    | Write 1 to Clear-only. These bits may be cleared by software by writing a 1. Writing a 0 has no effect. The state of the bits cannot be read directly. The states of such bits are tracked outside the CPU and all read transactions to the address of such bits are routed to the other agent. Write transactions to these bits go to both agents.                                                                                                       |  |

# 8.2 System Address Map

The processor supports 4 GB of addressable memory space and 64 KB+3 of addressable I/O space. There is a programmable memory address space under

the 1 MB region which is divided into regions which can be individually controlled with programmable attributes such as Disable, Read/Write, Write Only, or Read Only. Attribute programming is described in the Register Description section. This section focuses on how the memory space is partitioned and what the separate memory regions are used for. I/O address space has simpler mapping and is explained near the end of this section.

The processor supports a maximum of 2GB of DRAM. No DRAM memory will be accessible above 2 GB. DRAM capacity is limited by the silicon fuse. There is no hardware lock to stop someone from inserting more memory than that is addressable.

When running in internal graphics mode, writes to GMADR range linear range are supported. Write accesses to linear regions are supported from DMI. Write accesses to tileX and tileY regions (defined via fence registers) are not supported from DMI. GMADR read accesses are not supported from DMI. In the following sections, it is assumed that all of the compatibility memory ranges reside on the DMI Interface. The exception to this rule is VGA ranges, which may be mapped to DMI or to the internal graphics device (IGD). In the absence of more specific references, cycle descriptions referencing PCI should be interpreted as the DMI Interface/PCI, while cycle descriptions referencing IGD are related to the internal graphics device. processor does not remap APIC or any other memory spaces above TOLUD (Top of Low Usable DRAM). The TOLUD register is set to the appropriate value by BIOS. The reclaimbase/reclaimlimit registers remap logical accesses bound for addresses above 4G onto physical addresses that fall within DRAM.

The Address Map includes a number of programmable ranges:

#### 1. Device 0:

- PXPEPBAR Egress port registers. Necessary for setting up VC1 as an isochronous channel with fixed arbitration. (4KB window)

- MCHBAR Memory mapped range for IMC registers. For example, memory buffer register controls. (16KB window)

- PCIEXBAR Flat memory-mapped address spaced to access device configuration registers. This mechanism can be used to access PCI configuration space (0-FFh) and Extended configuration space (100h-FFFh) for PCI Express devices. This enhanced configuration access mechanism is defined in the PCI Express specification. (64MB, 128MB, or 256MB window).

- DMIBAR This window is used to access registers associated with the processor Serial Interconnect (DMI) register memory range. (4KB window)

- GGCGMS graphics control register, Graphics Mode Select. Used to select the amount of main memory that is pre-allocated to support the internal graphics device in VGA (non-linear) and Native (linear) modes. (0-64MB options).

- GGCGGMS graphics control register, GTT Graphics Memory Size. Used to select the amount of main memory that is pre-allocated to support the Internal Graphics Translation Table. (0-2MB options).

#### 2. Device 2, Function 0:

- MMADR IGD registers and internal graphics instruction port. (512KB window)

- IOBAR IO access window for internal graphics. Though this window address/data register pair, using I/O semantics, the IGD and internal graphics instruction port registers can be accessed. Note, this allows accessing the same registers as MMADR.

- GMADR Internal graphics translation window (128MB, 256MB or 512MB window).

- GTTADR Internal graphics translation table location. (1MB window).

**Note:** The Base of GTT stolen Memory register (Device 0 A8) indicates the physical address base which is 1MB aligned.

#### 3. Device 2, Function 1:

MMADR – Function 1 IGD registers and internal graphics instruction port (512KB window).

The rules for the above programmable ranges are:

- ALL of these ranges MUST be unique and NON-OVERLAPPING. It is the BIOS or system designers' responsibility to limit memory population so that adequate PCI, High BIOS, and APIC memory space can be allocated.

- In the case of overlapping ranges with memory, the memory decode will be given priority.

- There are NO Hardware Interlocks to prevent problems in the case of overlapping ranges.

- Accesses to overlapped ranges may produce indeterminate results.

- Peer-to-peer cycles from DMI Interface to the Internal Graphics VGA is not allowed.

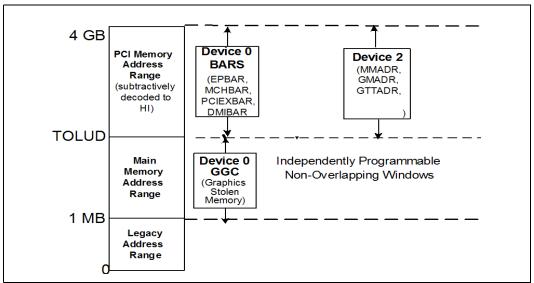

The following figure represents system memory address map in a simplified form:

Figure 8-1. System Address Ranges

# 8.2.1 Legacy Address Range

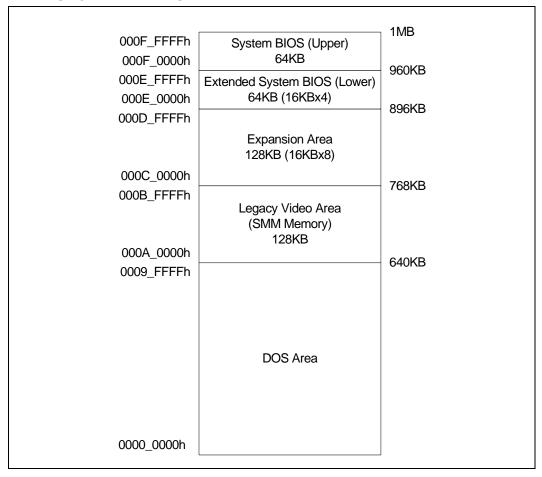

This area is divided into the following address regions:

- 0 640 KB DOS Area

- 640 768 KB Legacy Video Buffer Area

- 768 896 KB in 16KB sections (total of 8 sections) Expansion Area

- 896 -960 KB in 16KB sections (total of 4 sections) Extended System BIOS Area

- 960 KB 1 MB Memory System BIOS Area

Figure 8-2. DOS Legacy Address Range

#### 8.2.1.1 DOS Range (0h – 9\_FFFFh)

The DOS area is 640 KB (0000\_0000h - 0009\_FFFFh) in size and is always mapped to the main memory controlled by the Integrated Memory Controller (IMC).

#### 8.2.1.2 Legacy Video Area (A\_0000h-B\_FFFFh)

The legacy 128-KB VGA memory range, frame buffer, (000A\_0000h – 000B\_FFFFh) can be mapped to IGD (Device 2), and/or to the DMI. The appropriate mapping depends on which devices are enabled and the programming of the VGA steering bits. Based on the VGA steering bits, priority for VGA mapping is constant. The IMC always decodes internally mapped devices first. Internal to the IMC, decode precedence is always given to IGD. The IMC always positively decodes internally mapped devices, namely the IGD and PCI Express. Subsequent decoding of regions mapped to PCI Express or the DMI depends on the Legacy VGA configuration bits (VGA Enable and MDAP). This region is also the default for SMM space.

#### 8.2.1.2.1 Compatible SMRAM Address Range (A\_0000h-B\_FFFFh)

When compatible SMM space is enabled, SMM-mode CPU accesses to this range are routed to physical system DRAM at 000A 0000h - 000B FFFFh. Non-SMM-mode CPU accesses to this range are considered to be to the Video Buffer Area as described above. PCI Express and DMI originated cycles to enabled SMM space are not allowed and are considered to be to the Video Buffer Area if IGD is not enabled as the VGA device. PCI Express and DMI initiated cycles are attempted as Peer cycles, and will master abort on PCI if no external VGA device claims them.

#### 8.2.1.2.2 Monochrome Adapter (MDA) Range (B\_0000h-B\_7FFFh)

Legacy support requires the ability to have a second graphics controller (monochrome) in the system. Accesses in the standard VGA range are forwarded to IGD, PCI Express, or the DMI (depending on configuration bits). Since the monochrome adapter may be mapped to any one of these devices, the IMC must decode cycles in the MDA range (000B\_0000h - 000B\_7FFFh) and forward either to IGD, PCI Express, or the DMI. This capability is controlled by a VGA steering bits and the legacy configuration bit (MDAP bit). In addition to the memory range B0000h to B7FFFh, the IMC decodes IO cycles at 3B4h, 3B5h, 3B8h, 3B9h, 3BAh and 3BFh and forwards them to the either IGD, PCI Express, and/or the DMI.

#### 8.2.1.3 Expansion Area (C\_0000h-D\_FFFFh)

This 128-KB ISA Expansion region (000C\_0000h - 000D\_FFFFh) is divided into eight, 16-KB segments. Each segment can be assigned one of four Read/Write states: read-only, write-only, read/write, or disabled. Typically, these blocks are mapped through IMC and are subtractively decoded to ISA space. Memory that is disabled is not remapped.

Non-snooped accesses from PCI Express or DMI to this region are always sent to DRAM.

**Table 8-1. Expansion Area Memory Segments**

| Memory Segments   | Attributes | Comments    |

|-------------------|------------|-------------|

| OCOOOOH - OC3FFFH | W/R        | Add-on BIOS |

| 0C4000H - 0C7FFFH | W/R        | Add-on BIOS |

| OC8000H - OCBFFFH | W/R        | Add-on BIOS |

| OCCOOOH - OCFFFFH | W/R        | Add-on BIOS |

| ODOOOOH - OD3FFFH | W/R        | Add-on BIOS |

| OD4000H - OD7FFFH | W/R        | Add-on BIOS |

| OD8000H - ODBFFFH | W/R        | Add-on BIOS |

| ODCOOOH - ODFFFFH | W/R        | Add-on BIOS |

#### 8.2.1.4 Extended System BIOS Area (E\_0000h-E\_FFFFh)

This 64-KB area (000E\_0000h – 000E\_FFFFh) is divided into four, 16-KB segments. Each segment can be assigned independent read and write attributes so it can be mapped either to main DRAM or to DMI. Typically, this area is used for RAM or ROM. Memory segments that are disabled are not remapped elsewhere.

Non-snooped accesses from PCI Express or DMI to this region are always sent to DRAM.

Table 8-2. Extended System BIOS Area Memory Segments

| Memory Segments   | Attributes | Comments       |

|-------------------|------------|----------------|

| OEOOOOH - OE3FFFH | W/R        | BIOS Extension |

| 0E4000H - 0E7FFFH | W/R        | BIOS Extension |

| OE8000H - OEBFFFH | W/R        | BIOS Extension |

| OECOOOH - OEFFFFH | W/R        | BIOS Extension |

# 8.2.1.5 System BIOS Area (F\_0000h-F\_FFFFh)

This area is a single, 64-KB segment (000F\_0000h – 000F\_FFFFh). This segment can be assigned read and write attributes. It is by default (after reset) Read/Write disabled and cycles are forwarded to DMI. By manipulating the Read/Write attributes, the IMC can "shadow" BIOS into the main DRAM. When disabled, this segment is not remapped.

Non-snooped accesses from PCI Express or DMI to this region are always sent to DRAM.

Table 8-3. System BIOS Area Memory Segments

| Memory Segments   | Attributes | Comments  |

|-------------------|------------|-----------|

| OFOOOOH - OFFFFFH | WE RE      | BIOS Area |

#### 8.2.1.6 Programmable Attribute Map (PAM) Memory Area Details

The 13 sections from 768 KB to 1 MB comprise what is also known as the PAM Memory Area.

The IMC does not handle IWB (Implicit Write-Back) cycles targeting DMI. Since all memory residing on DMI should be set as non-cacheable, there normally will not be IWB cycles targeting DMI.

However, DMI becomes the default target for CPU and DMI originated accesses to disabled segments of the PAM region. If the MTRRs covering the PAM regions are set to WB or RC it is possible to get IWB cycles targeting DMI. This may occur for DMI originated cycles to disabled PAM regions.

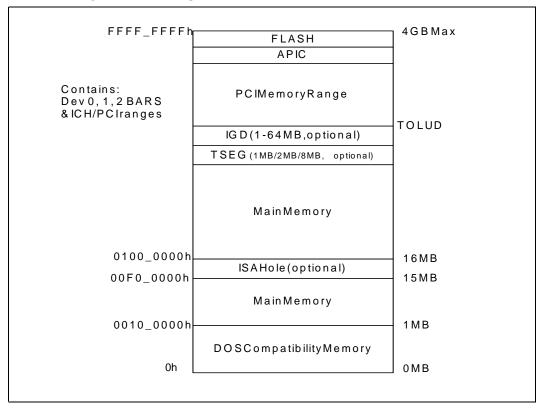

# 8.2.2 Main Memory Address Range (1 MB to TOLUD)

This address range extends from 1 MB to the top of physical memory that is permitted to be accessible by the IMC (as programmed in the TOLUD register). All accesses to addresses within this range will be forwarded by the IMC to the DRAM unless they fall into the optional TSEG, optional ISA Hole, or optional IGD stolen VGA memory.

The processor provides a maximum DRAM address decode space of 4 GB. The processor does not remap APIC memory space. This means that as the amount of physical memory populated in the system reaches 4 GB, there will be physical memory that exists yet is non-addressable and therefore unusable by the system.

The processor does not limit DRAM address space in hardware.

Figure 8-3. Main Memory Address Range

#### 8.2.2.1 ISA Hole (15 MB-16 MB)

A hole can be created at 15 MB–16 MB as controlled by the fixed hole enable in Device 0 space. Accesses within this hole are forwarded to the DMI. The range of physical DRAM memory disabled by opening the hole is not remapped to the top of the memory – that physical DRAM space is not accessible. This 15-MB to 16-MB hole is an optionally enabled ISA hole.

Video accelerators originally used this hole. It is also used for validation by customer teams for some of their test cards. That is why it is being supported. There is no inherent BIOS request for the 15-MB to 16-MB window.

#### 8.2.2.2 TSEG

TSEG is optionally 1 MB, 2 MB, or 8 MB in size. TSEG is below IGD stolen memory, which is at the top of physical memory. SMM-mode CPU accesses to enabled TSEG access the physical DRAM at the same address. Non-CPU originated accesses are not allowed to SMM space. PCI Express, DMI, and Internal Graphics originated cycles to enabled SMM space are handled as invalid cycle type with reads and writes to location 0 and byte enables turned off for writes. When the extended SMRAM space is enabled, CPU accesses to the TSEG range without SMM attribute or without WB attribute are also forwarded to memory as invalid accesses (see Table 8-5). Non-SMM-mode Write Back cycles that target TSEG space are completed to DRAM for cache coherency. When SMM is enabled the maximum amount of memory available to the system is equal to the amount of physical DRAM minus the value in the TSEG register which is fixed at 1 MB, 2 MB or 8 MB.

#### 8.2.2.3 Pre-allocated Memory

Voids of physical addresses that are not accessible as general system memory and reside within system memory address range (< TOLUD) are created for SMM-mode and legacy VGA graphics compatibility. It is the responsibility of BIOS to properly initialize these regions. Table 8-4 details the location and attributes of the regions. How to enable and disable these ranges are described in the processor Control Register Device 0 (GGC).

Table 8-4. Pre-allocated Memory Example for 64-MB DRAM, 1-MB VGA, and 1-MB TSEG

| Memory<br>Segments         | Attributes                   | Comments                                                                          |

|----------------------------|------------------------------|-----------------------------------------------------------------------------------|

| 0000_0000h –<br>03DF_FFFFh | R/W                          | Available System Memory 62 MB                                                     |

| 03E0_0000h –<br>03EF_FFFFh | SMM Mode Only -<br>CPU Reads | TSEG Address Range & Pre-allocated Memory                                         |

| 03F0_0000h –<br>03FF_FFFFh | R/W                          | Pre-allocated Graphics VGA memory.  1 MB (or 4/8/16/32/64 MB) when IGD is enabled |

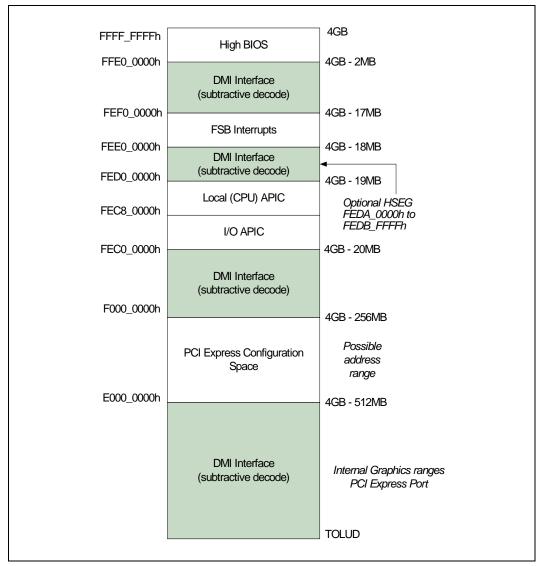

### 8.2.3 PCI Memory Address Range (TOLUD – 4 GB)

This address range, from the top of physical memory to 4 GB (top of addressable memory space supported by the IMC is normally mapped to the DMI Interface.

Exceptions to this mapping include the BAR memory mapped regions, which include:

- 1. Addresses decoded to the egress port registers (PXPEPBAR)

- 2. Addresses decoded to the memory mapped range for internal memory controller registers (MCHBAR)

- 3. Addresses decoded to the flat memory-mapped address spaced to access device configuration registers (PCIEXBAR)

- 4. Addresses decoded to the registers associated with the processor Serial Interconnect (DMI) register memory range. (DMIBAR)

In an internal graphics configuration, there are three exceptions to this rule:

- 1. Addresses decoded to the Graphics Memory Range. (GMADR range)

- 2. Addresses decoded to the Graphics Translation Table range (GTTADR range)

- 3. Addresses decoded to the Memory Mapped Range of the Internal Graphics Device (MMADR range). There is a MMADR range for Device 2 Function 0 and a MMADR range for Device 2 Function 1. Both ranges are forwarded to the internal graphics device

There are sub-ranges within the PCI Memory address range defined as APIC Configuration Space, and High BIOS Address Range. The exceptions listed above for internal graphics *MUST NOT* overlap with these ranges.

Figure 8-4. PCI Memory Address Range

#### 8.2.3.1 APIC Configuration Space (FECO\_0000h-FECF\_FFFFh)

This range is reserved for APIC configuration space which includes the default I/O APIC configuration space from FECO\_0000h to FEC7\_0FFFh. The default Local (CPU) APIC configuration space goes from FEC8\_0000h to FECF\_FFFFh.

CPU accesses to the Local APIC configuration space do not result in external bus activity since the Local APIC configuration space is internal to the CPU. However, an MTRR must be programmed to make the Local APIC range uncacheable (UC). The Local APIC base address in each CPU should be relocated to the FECO\_0000h (4 GB-20 MB)

to FECF\_FFFFh range so that one MTRR can be programmed to 64 KB for the Local and I/O APICs. The I/O APIC(s) usually reside in the ICH portion of the chip set or as a stand-alone component(s).

I/O APIC units will be located beginning at the default address FECO\_0000h. The first I/O APIC will be located at FECO\_0000h. Each I/O APIC unit is located at FECO\_x000h where x is I/O APIC unit number 0 through F(hex). This address range will normally be mapped to DMI.

**Note:** There is no provision to support an I/O APIC device on PCI Express.

#### 8.2.3.2 HSEG (FEDA\_0000h-FEDB\_FFFFh)

This optional segment from FEDA\_0000h to FEDB\_FFFFh provides a remapping window to SMM memory. It is sometimes called the High SMM memory space. SMM-mode CPU accesses to the optionally enabled HSEG are remapped to 000A\_0000h - 000B\_FFFFh. Non-SMM mode CPU accesses to enabled HSEG are considered invalid and are terminated immediately on the FSB. The exceptions to this rule are Non-SMM mode Write Back cycles which are remapped to SMM space to maintain cache coherency. PCI Express and DMI originated cycles to enabled SMM space are not allowed. Physical DRAM behind the HSEG transaction address is not remapped and is not accessible. All Cacheline writes with WB attribute or implicit write backs to the HSEG range are completed to DRAM like an SMM cycle.

#### 8.2.3.3 High BIOS Area

The top 2 MB (FFEO\_0000h -FFFF\_FFFFh) of the PCI Memory Address Range is reserved for System BIOS (High BIOS), extended BIOS for PCI devices, and the A20 alias of the system BIOS. The CPU begins execution from the High BIOS after reset. This region is mapped to DMI so that the upper subset of this region aliases to the 16-MB-256-KB range. The actual address space required for the BIOS is less than 2 MB but the minimum CPU MTRR range for this region is 2 MB so that full 2 MB must be considered.

# 8.2.4 Graphics Memory Address Ranges

The processor can be programmed to direct memory accesses to IGD when addresses are within any of ranges specified via registers in processor's Device 2 configuration space.

- The Memory Map Base register (MMADR) is used to access graphics control registers.

- The Graphics Memory Aperture Base register (GMADR) is used to access graphics memory allocated via the graphics translation table.

- The Graphics Translation Table Base register (GTTADR) is used to access the translation table.

Normally these ranges will reside above the Top-of-Low-DRAM and below High BIOS and APIC address ranges. They normally reside above the top of memory (TOLUD) so they do not steal any physical DRAM memory space.

GMADR is a Prefetchable range in order to apply USWC attribute (from the processor point of view) to that range. The USWC attribute is used by the processor for write combining.

#### 8.2.4.1 Graphics Register Ranges

This section provides a high-level register map (register groupings per function) for the integrated graphics. The memory and I/O maps for the graphics registers are shown in Figure 8-5, except PCI Configuration registers. The VGA and Extended VGA registers can be accessed via standard VGA I/O locations as well as via memory-mapped locations. In addition, the memory map contains allocation ranges for various functions. The memory space address listed for each register is an offset from the base memory address programmed into the MMADR register (PCI configuration offset 14h). The same memory space can be accessed via dword accesses to I/OBAR. Through the IOBAR, I/O registers MMIO\_index and MMIO\_data are written.

#### VGA and Extended VGA Control Registers (00000h-00FFFh)

These registers are located in both I/O space and memory space. The VGA and Extended VGA registers contain the following register sets: General Control/Status, Sequencer (SRxx), Graphics Controller (GRxx), Attribute Controller (ARxx), VGA Color Palette, and CRT Controller (CRxx) registers.

#### Instruction, Memory, and Interrupt Control Registers (01000h-02FFFh)

The Instruction and Interrupt Control registers are located in main memory space and contain the types of registers listed in the following sections.

#### 8.2.4.2 I/O Mapped Access to Device 2 MMIO Space

If Device 2 is enabled, and Function 0 within Device 2 is enabled, then IGD registers can be accessed using the IOBAR.

**MMIO\_Index**: MMIO\_INDEX is a 32-bit register. An I/O write to this port loads the address of the MMIO register that needs to be accessed. I/O Reads returns the current value of this register.

**MMIO\_Data**: MMIO\_DATA is a 32-bit register. An I/O write to this port is re-directed to the MMIO register pointed to by the MMIO-index register. An I/O read to this port is redirected to the MMIO register pointed to by the MMIO-index register.

Figure 8-5. Graphics Register Memory and I/O Map

### 8.2.5 System Management Mode (SMM)

System Management Mode uses main memory for System Management RAM (SMM RAM). The processor supports: Compatible SMRAM (C\_SMRAM), High Segment (HSEG), and Top of Memory Segment (TSEG). System Management RAM space provides a memory area that is available for the SMI handlers and code and data storage. This memory resource is normally hidden from the system OS so that the processor has immediate access to this memory space upon entry to SMM. IMC provides three SMRAM options:

- Below 1-MB option that supports compatible SMI handlers.

- Above 1-MB option that allows new SMI handlers to execute with write-back cacheable SMRAM.

- Optional TSEG area of 1 MB, 2 MB, or 8 MB in size. The TSEG area lies below IGD stolen memory.

The above 1-MB solutions require changes to compatible SMRAM handlers code to properly execute above 1 MB.

**Note:** DMI masters are not allowed to access the SMM space.

#### 8.2.5.1 SMM Space Definition

SMM space is defined by its **addressed** SMM space and its DRAM SMM space. The addressed SMM space is defined as the range of bus addresses used by the CPU to access SMM space. DRAM SMM space is defined as the range of physical DRAM memory locations containing the SMM code. SMM space can be accessed at one of three transaction address ranges: Compatible, High and TSEG. The Compatible and TSEG SMM space is not remapped and therefore the addressed and DRAM SMM space is the same address range. Since the High SMM space is remapped the addressed and DRAM SMM space are different address ranges.

**Note:** The High DRAM space is the same as the Compatible Transaction Address space.

Table 8-5 describes three unique address ranges:

- Compatible Transaction Address (Adr C)

- High Transaction Address (Adr H)

- TSEG Transaction Address (Adr T)

These abbreviations are used later in the table describing SMM Space Transaction Handling.

Table 8-5. SMM Space Definition Summary

| SMM Space Enabled | Transaction Address Space           | DRAM Space (DRAM)                   |

|-------------------|-------------------------------------|-------------------------------------|

| Compatible (C)    | 000A_0000h to 000B_FFFFh            | 000A_0000h to 000B_FFFFh            |

| High (H)          | FEDA_0000h to FEDB_FFFFh            | 000A_0000h to 000B_FFFFh            |

| TSEG (T)          | (TOLUD-STOLEN-TSEG) to TOLUD-STOLEN | (TOLUD-STOLEN-TSEG) to TOLUD-STOLEN |

#### 8.2.5.2 SMM Space restrictions

If any of the following conditions are violated, the results of SMM accesses are unpredictable and may cause the system to hang:

- The Compatible SMM space **must not** be set-up as cacheable.

- High or TSEG SMM transaction address space must not overlap address space assigned to system DRAM, or to any "PCI" devices (including DMI, PCI Express, and graphics devices). This is a BIOS responsibility.

- Both D\_OPEN and D\_CLOSE must not be set to 1 at the same time.

- When TSEG SMM space is enabled, the TSEG space must not be reported to the OS as available DRAM. This is a BIOS responsibility.

- Any address translated through the GMADR must not target DRAM from A\_0000-F\_FFFF.

### 8.2.5.3 SMM Space Combinations

When High SMM is enabled (G\_SMRAME=1 and H\_SMRAM\_EN=1) the Compatible SMM space is effectively disabled. CPU originated accesses to the Compatible SMM space are forwarded to PCI Express if VGAEN=1 (also depends on MDAP), otherwise they are forwarded to the DMI. PCI Express and DMI originated accesses are **never** allowed to access SMM space.

Table 8-6. SMM Space Table

| Global Enable<br>G_SMRAME | High Enable<br>H_SMRAM_EN | TSEG Enable<br>TSEG_EN | Compatible (C) Range | High (H)<br>Range | TSEG (T)<br>Range |

|---------------------------|---------------------------|------------------------|----------------------|-------------------|-------------------|

| 0                         | Х                         | Х                      | Disable              | Disable           | Disable           |

| 1                         | 0                         | 0                      | Enable               | Disable           | Disable           |

| 1                         | 0                         | 1                      | Enable               | Disable           | Enable            |

| 1                         | 1                         | 0                      | Disabled             | Enable            | Disable           |

| 1                         | 1                         | 1                      | Disabled             | Enable            | Enable            |

#### 8.2.5.4 SMM Control Combinations

The G\_SMRAME bit provides a global enable for all SMM memory. The D\_OPEN bit allows software to write to the SMM ranges without being in SMM mode. BIOS software can use this bit to initialize SMM code at power-up. The D\_LCK bit limits the SMM range

access to only SMM mode accesses. The D\_CLS bit causes SMM data accesses to be forwarded to the DMI or PCI Express. The SMM software can use this bit to write to video memory while running SMM code out of DRAM.

Table 8-7. SMM Control Table

| G_SMRAME | D_LCK | D_CLS | D_OPEN | CPU in SMM<br>Mode | SMM Code<br>Access | SMM Data<br>Access |

|----------|-------|-------|--------|--------------------|--------------------|--------------------|

| 0        | х     | Х     | х      | ×                  | Disable            | Disable            |

| 1        | 0     | Х     | 0      | 0                  | Disable            | Disable            |

| 1        | 0     | 0     | 0      | 1                  | Enable             | Enable             |

| 1        | 0     | 0     | 1      | ×                  | Enable             | Enable             |

| 1        | 0     | 1     | 0      | 1                  | Enable             | Disable            |

| 1        | 0     | 1     | 1      | ×                  | Invalid            | Invalid            |

| 1        | 1     | Х     | х      | 0                  | Disable            | Disable            |

| 1        | 1     | 0     | х      | 1                  | Enable             | Enable             |

| 1        | 1     | 1     | х      | 1                  | Enable             | Disable            |

#### 8.2.5.5 SMM Space Decode and Transaction Handling

Only the CPU is allowed to access SMM space. DMI originated transactions are not allowed to SMM space.

#### 8.2.5.6 CPU WB Transaction to an Enabled SMM Address Space

CPU Writeback transactions (REQ[1]#=0) to enabled SMM address space must be written to the associated SMM DRAM even though D\_OPEN=0 and the transaction is not performed in SMM mode. This ensures SMM space cache coherency when cacheable extended SMM space is used.

#### 8.2.5.7 SMM Access through GTT TLB

Accesses through GTT TLB address translation to enabled SMM DRAM space are not allowed. Writes will be routed to Memory address 000C\_0000h with byte enables deasserted and reads will be routed to Memory address 000C\_0000h. If a GTT TLB translated address hits enabled SMM DRAM space, an error is recorded in the PGTBL\_ER register.

DMI Interface originated accesses are **never** allowed to access SMM space directly or through the GTT TLB address translation. If a GTT TLB translated address hits enabled SMM DRAM space, an error is recorded in the PGTBL\_ER register.

DMI Interface write accesses through GMADR range will be snooped. Assesses to GMADR linear range (defined via fence registers) are supported. DMI Interface tileY and tileX writes to GMADR are not supported. If, when translated, the resulting physical address is to enabled SMM DRAM space, the request will be remapped to address 000C\_0000h with deasserted byte enables.

DMI Interface read accesses to the GMADR range are not supported therefore will have no address translation concerns. DMI Interface reads to GMADR will be remapped to address 000C\_0000h. The read will complete with UR (unsupported request) completion status.

GTT fetches are always decoded (at fetch time) to ensure not in SMM (actually, anything above base of TSEG or 640K-1M). Thus, they will be invalid and go to address 000C\_0000h, but that isn't specific to DMI; it applies to CPU or internal graphics engines. Also, since the GMADR snoop would not be directly to the SMM space, there wouldn't be a writeback to SMM. In fact, the writeback would also be invalid (because it uses the same translation) and go to address 000C\_0000h.

# 8.2.6 Memory Shadowing

Any block of memory that can be designated as read-only or write-only can be "shadowed" into DRAM memory. Typically this is done to allow ROM code to execute more rapidly out of main DRAM. ROM is used as read-only during the copy process while DRAM at the same time is designated write-only. After copying, the DRAM is designated read-only so that ROM is shadowed. CPU bus transactions are routed accordingly.

# 8.2.7 I/O Address Space

The processor does not support the existence of any other I/O devices beside itself. The processor generates DMI cycles for all processor I/O accesses that it does not claim. Within the host bridge the processor contains two internal registers in the CPU I/O space, Configuration Address register (CONFIG\_ADDRESS) and the Configuration Data register (CONFIG\_DATA). These locations are used to implement a configuration space access mechanism.

The CPU allows 64 k+3 bytes to be addressed within the I/O space. The processor propagates the CPU I/O address without any translation on to the destination bus and therefore provides addressability for 64 k+3 byte locations.

Note:

The upper three locations can be accessed only during I/O address wrap-around when CPU bus HAB\_16 address signal is asserted. HAB\_16 is asserted on the CPU bus whenever an I/O access is made to 4 bytes from address OFFFDh, OFFFEh, or OFFFFh. HAB\_16 is also asserted when an I/O access is made to 2 bytes from address OFFFFh.

A set of I/O accesses (other than ones used for configuration space access) are consumed by the internal graphics device if it is enabled. The mechanisms for internal graphics I/O decode and the associated control is explained later.

The I/O accesses (other than ones used for configuration space access) are forwarded normally to the DMI bus unless they fall within the PCI Express I/O address range as defined by the mechanisms explained below. I/O writes are **not** posted. Memory writes to ICH or PCI Express are posted. The PCICMD1 register can disable the routing of I/O cycles to PCI Express.

The processor responds to I/O cycles initiated on DMI with a UR status. Upstream I/O cycles and configuration cycles should never occur. If one does occur, the request will route as a read to memory address 0h so a completion is naturally generated (whether the original request was a read or write). The transaction will complete with a UR completion status.

# 8.2.8 Memory Controller Decode Rules and Cross-Bridge Address Mapping

$VGAA = 000A\_0000 - 000A\_FFFF$

$MDA = 000B_0000 - 000B_7FFF$

$VGAB = 000B_8000 - 000B_FFFF$

MAINMEM = 0100\_0000 to TOLUD

#### 8.2.8.1 Legacy VGA and I/O Range Decode Rules

The legacy 128-KB VGA memory range 000A\_0000h-000B\_FFFFh can be mapped to IGD (Device 2), and/or to the DMI depending on the programming of the VGA steering bits. Priority for VGA mapping is constant in that the GMCH always decodes internally mapped devices first. Internal to the GMCH, decode precedence is always given to IGD. The GMCH always positively decodes internally mapped devices, namely the IGD. Subsequent decoding of regions mapped to the DMI depends on the Legacy VGA configurations bits (VGA Enable and MDAP).

# 8.3 Processor Register Introduction

The processor processor internal registers (I/O Mapped Configuration and PCI Express Extended Configuration registers) are accessible by the Host CPU. The registers that reside within the lower 256 bytes of each device can be accessed as Byte, Word (16-bit), or Dword (32-bit) quantities, with the exception of CONFIG\_ADDRESS which can only be accessed as a Dword. All multi-byte numeric fields use "little-Indian" ordering (i.e., lower addresses contain the least significant parts of the field). Registers which reside in bytes 256 through 4095 of each device may only be accessed using memory mapped transactions in Dword (32-bit) quantities.

Some of the processor registers described in this section contain reserved bits. These bits are labeled "Reserved". Software must deal correctly with fields that are reserved.

On reads, software must use appropriate masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new values for other bit positions and then written back. Note the software does not need to perform read, merge, write operation for the configuration address register.

In addition to reserved bits within a register, the processor contains address locations in the configuration space of the Host Bridge entity that are marked either "Reserved" or "Intel Reserved". The CPU responds to accesses to "Reserved" address locations by completing the host cycle. When a "Reserved" register location is read, a zero value is returned. ("Reserved" registers can be 8-, 16-, or 32-bit in size). Writes to "Reserved" registers have no effect on the CPU. Registers that are marked as "Intel Reserved" must not be modified by system software. Writes to "Intel Reserved" registers may cause system failure. Reads to "Intel Reserved" registers may return a non-zero value.

Upon a Full Reset, the processor sets all of its internal configuration registers to predetermined default states. Some register values at reset are determined by external strapping options, or the states of polysilicon fuses. The default state represents the minimum functionality feature set required to successfully bring up the system. Hence, it does not represent the optimal system configuration. It is the responsibility of the system initialization software (usually BIOS) to properly determine the DRAM configurations, operating parameters and optional system features that are applicable, and to program the processor registers accordingly.

# 8.4 I/O Mapped Registers

The processor contains two registers that reside in the processor I/O address space - the Configuration Address (CONFIG\_ADDRESS) Register and the Configuration Data (CONFIG\_DATA) Register. The Configuration Address Register enables/disables the configuration space and determines what portion of configuration space is visible through the Configuration Data window.

#### 8.5 PCI Device 0

The processor/DMI controller registers are in Device 0 (D0), Function 0 (F0).

Address locations that are not listed are considered Intel Reserved registers locations. Reads to Reserved registers may return non-zero values. Writes to reserved locations may cause system failures.

All registers that are defined in the latest *PCI Local Bus Specification*, but are not necessary or implemented in this component are simply not included in this document. The reserved/unimplemented space in the PCI configuration header space is not documented as such in this summary.

Table 8-8. Device 0 Function 0 Register Summary (Sheet 1 of 3)

| Register Name            | Register<br>Symbol | Register<br>Start | Register End | Default Value | Access  |

|--------------------------|--------------------|-------------------|--------------|---------------|---------|

| Vendor<br>Identification | VID                | 0                 | 1            | 8086h         | RO;     |

| Device<br>Identification | DID                | 2                 | 3            | A010h         | RO;     |

| PCI Command              | PCICMD             | 4                 | 5            | 0006h         | RO; RW; |

Table 8-8. Device 0 Function 0 Register Summary (Sheet 2 of 3)

| Register Name                                     | Register<br>Symbol | Register<br>Start | Register End | Default Value        | Access              |

|---------------------------------------------------|--------------------|-------------------|--------------|----------------------|---------------------|

| PCI Status                                        | PCISTS             | 6                 | 7            | 0090h                | RWC; RO;            |

| Revision<br>Identification                        | RID                | 8                 | 8            | 00h                  | RO;                 |

| Class Code                                        | СС                 | 9                 | В            | 060000h              | RO;                 |

| Master Latency<br>Timer                           | MLT                | D                 | D            | 00h                  | RO;                 |

| Header Type                                       | HDR                | Е                 | E            | 00h                  | RO;                 |

| Subsystem Vendor<br>Identification                | SVID               | 2C                | 2D           | 0000h                | RWO;                |

| Subsystem<br>Identification                       | SID                | 2E                | 2F           | 0000h                | RWO;                |

| Capabilities Pointer                              | CAPPTR             | 34                | 34           | E0h                  | RO;                 |

| PCI Express<br>Egress Port Base<br>Address        | PXPEPBAR           | 40                | 47           | 0000000000<br>00000h | RW-L; RO            |

| Processor Memory<br>Mapped Register<br>Range Base | MCHBAR             | 48                | 4F           | 00000000000<br>0000h | RW-L; RO;           |

| processor Graphics<br>Control Register            | GGC                | 52                | 53           | 0030h                | RO; RW-L;           |

| Device Enable                                     | DEVEN              | 54                | 57           | 00000019h            | RO; RW-L;           |

| PCI Express<br>Register Range<br>Base Address     | PCIEXBAR           | 60                | 67           | 0000000E00<br>00000h | RW/L; RO;<br>RW/L/K |

| Root Complex<br>Register Range<br>Base Address    | DMIBAR             | 68                | 6F           | 00000000000<br>0000h | RW-L; RO;           |

| Programmable<br>Attribute Map 0                   | PAMO               | 90                | 90           | 00h                  | RO; RW-L;           |

| Programmable<br>Attribute Map 1                   | PAM1               | 91                | 91           | 00h                  | RO; RW-L;           |

| Programmable<br>Attribute Map 2                   | PAM2               | 92                | 92           | 00h                  | RO; RW-L;           |

| Programmable<br>Attribute Map 3                   | PAM3               | 93                | 93           | 00h                  | RO; RW-L;           |

| Programmable<br>Attribute Map 4                   | PAM4               | 94                | 94           | 00h                  | RO; RW-L;           |

| Programmable<br>Attribute Map 5                   | PAM5               | 95                | 95           | 00h                  | RO; RW-L;           |

| Programmable<br>Attribute Map 6                   | PAM6               | 96                | 96           | 00h                  | RO; RW-L;           |

Table 8-8. Device 0 Function 0 Register Summary (Sheet 3 of 3)

| Register Name                                | Register<br>Symbol | Register<br>Start | Register End | Default Value | Access                   |

|----------------------------------------------|--------------------|-------------------|--------------|---------------|--------------------------|

| Legacy Access<br>Control                     | LAC                | 97                | 97           | 00h           | RW-L; RO;                |