# **Intel<sup>®</sup> Atom™ Processor E6xx Series**

## **Specification Update**

May 2013

**Revision 016**

**Notice:** The Intel<sup>®</sup> Atom<sup>™</sup> Processor E6xx Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

Document Number: 324209-016

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS! FESS ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/#/en\_US\_01.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Go to: http://www.intel.com/products/processor%5Fnumber/ for details.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Inside, Core Inside, i960, Intel, the Intel logo, Intel AppUp, Intel Atom, Intel Atom Inside, Intel Cilk, Intel Core, Intel Inside, the Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel Sponsors of Tomorrow., the Intel Sponsors of Tomorrow. logo, Intel StrataFlash, Intel VPro, Intel XScale, InTru, the Intru logo, the InTru Inside logo, Intru soundmark, Itanium, Itanium Inside, MCS, MMX, Moblin, Pentium, Pentium Inside, skoool, the skoool logo, Sound Mark, The Creators Project, The Journey Inside, VPro Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Microsoft, Windows, and the Windows logo are trademarks, or registered trademarks of Microsoft Corporation in the United States and/or other countries.

Copyright  $\ensuremath{@}$  2010-2013, Intel Corporation. All rights reserved.

## **Contents**

| Revision History                                 | ∠  |

|--------------------------------------------------|----|

| Introduction                                     |    |

| Summary Tables of Current Product Issue Activity |    |

| General Product Information                      |    |

| Microcode Updates                                | 17 |

| Errata                                           | 18 |

| NDA Errata                                       | 34 |

| Specification Changes                            | 35 |

| Specification Clarifications                     | 46 |

| Document-Only Changes                            | 50 |

May 2013 Document Number: 324209-016

## **Revision History**

| Date           | Revision | Description                                                                                                                                                                                                     |  |  |

|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| May 2013       | 016      | Updated Erratum BI57.                                                                                                                                                                                           |  |  |

| March 2013     | 015      | Out of cycle release to add Documentation Change 9.                                                                                                                                                             |  |  |

| March 2013     | 014      | Added Errata BI59. Added Documentation Change 8.                                                                                                                                                                |  |  |

| January 2013   | 013      | Added Errata BI57. and BI58.                                                                                                                                                                                    |  |  |

| May 2012       | 012      | Added Errata BI56.                                                                                                                                                                                              |  |  |

| April 2012     | 011      | Added Errata BI54. and BI55.                                                                                                                                                                                    |  |  |

| February 2012  | 010      | Added Errata BI52. and BI53. Specification Changes 2 through 4 and Documentation Changes 7 and 8. Added B1 PRQ stepping to the Component Markings table.                                                        |  |  |

| November 2011  | 009      | Added erratum BI51.<br>Updated Table 10.                                                                                                                                                                        |  |  |

| August 2011    | 008      | Removed Specification Changes, and Document Changes through Revision 007.  Added errata BI48., BI49., BI50 Added Specification Change 1, Specification Clarification 13, Document-Only Changes § §, 2, 3, 4, 5. |  |  |

| June 2011      | 007      | Added column "Stepping" to Table 5, 6 and 7. Added erratum BI45., BI46., Specification Changes 11, 12, 13. Document-Only Changes 30, 32.                                                                        |  |  |

| May 2011       | 006      | Removed Specification Changes referring to Datasheet Rev. 002, and TMDG Rev. 001 Added Specification Changes 9, 10, Document Changes 17, 18, 19, 20, 21, 27, 29                                                 |  |  |

| April 2011     | 005      | Added Specification Changes 5, 7, 8, corrected Table Number in Specification Change 2, and Document Changes 3, 4, 5, 6, 11, 14, 15.                                                                             |  |  |

| March 2011     | 004      | Added Specification Change 3, added Section , "Microcode Updates" on page 16                                                                                                                                    |  |  |

| February 2011  | 003      | Added specification change 2, and Document Changes 1 and 2                                                                                                                                                      |  |  |

| December 2010  | 002      | Added errata BI41. and BI44. and Specification Changes 1 through 4                                                                                                                                              |  |  |

| September 2010 | 001      | Initial release                                                                                                                                                                                                 |  |  |

## Introduction

## **Purpose/Scope/Audience**

This document is an update to the specifications listed in the Parent Documents/Related Documents table that follows. This document is a compilation of Errata, Specification Changes, Specification Clarifications, and Document-Only Changes. It is intended for hardware and software system designers and manufacturers as well as developers of applications, operating systems, or tools.

Information types defined in Conventions and Terminology are consolidated into the Specification Update and are no longer published in other documents.

This document may also contain information that was not previously published.

### **Table 1.** Parent Documents/Related Documents

| Title                                                                                                  | Number                                                                        |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manuals                             | http://www.intel.com/products/<br>processor/manuals/                          |

| Intel <sup>®</sup> Atom™ Processor E6xx Series Datasheet                                               | http://download.intel.com/embe<br>dded/processor/datasheet/3242<br>08.pdf     |

| Intel <sup>®</sup> Atom <sup>™</sup> Processor E6xx Series Thermal and Mechanical Design<br>Guidelines | http://download.intel.com/embe<br>dded/processors/thermalguide/<br>324210.pdf |

## **Conventions and Terminology**

Note:

Errata remain in the Specification Update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the Specification Update are archived and available upon request. Specification Changes, Specification Clarifications and Document-Only Changes are removed from the Specification Update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

### Table 2. Conventions and Terminology

| Term                                        | Definition                                                                                                                                                                                                                                                                                              |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Document-<br>Only<br>Changes                | Document-Only Changes are changes to an Intel Parent Specification that result in changes only to an Intel customer document but no changes to a specification or to a parameter for an Intel product. An example of a document-only change is the correction of a typographical error.                 |

| Errata<br>(plural)<br>Erratum<br>(singular) | Errata are design defects or errors. These may cause the Intel® Atom™ Processor E6xx Series's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices. |

## **Table 2.** Conventions and Terminology

| Term                            | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parent<br>Specification         | A parent specification is a top-level specification from which other documents can be derived, depending on the product or platform. Typically, a parent specification includes a product's pinout, architectural overview, device operation, hardware interface, or electrical specifications.  Examples of parent specifications include the following: Datasheet, External Design Specification (EDS), Developer's Manual, Technical Product Specification.  The derived documents may be used for purposes other than that for which the parent specification is used. |

| Specification                   | Specification Changes are the result of adding, removing, or changing a feature, after which an Intel product subsequently operates differently than specified in an Intel Parent Specification,                                                                                                                                                                                                                                                                                                                                                                           |

| Changes                         | but typically the customer does not have to do anything to achieve proper device functionality as a result of Intel adding, removing, or changing a feature.                                                                                                                                                                                                                                                                                                                                                                                                               |

| Specification<br>Clarifications | Specification Clarifications are changes to a document that arise when an Intel Parent Specification must be reworded so that the specification is either more clear or not in conflict with another specification.                                                                                                                                                                                                                                                                                                                                                        |

## **Summary Tables of Current Product Issue Activity**

Table 5 through Table 11 indicate the Errata, Specification Changes, Specification Clarifications, and Document-Only Changes that apply to the Intel<sup>®</sup> Atom™ Processor E6xx Series product. Intel may fix some of the Errata in a future stepping of the component as noted in Table 4 or account for the other outstanding issues through Specification Changes, Specification Clarifications, or Document-Only Changes. Table 5 through Table 11 use the codes listed in Table 4.

### Table 3. Codes Used in Summary Tables

| Code             | Column   | Definition                                                                                                                                                          |  |  |

|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Х                | Stepping | Indicates either that, for the stepping/revision listed,  • an erratum eXists and is not yet fixed  • a specification change or specification clarification applies |  |  |

| No mark or blank | Stepping | Indicates either that, for the stepping/revision listed,                                                                                                            |  |  |

| Plan Fix         | Status   | This erratum may be fixed in a future stepping/revision.                                                                                                            |  |  |

| Fixed            | Status   | This erratum has been previously fixed.                                                                                                                             |  |  |

| No Fix           | Status   | There are no plans to fix this erratum.                                                                                                                             |  |  |

A change bar to the left of a table row indicates an item that is either new or modified from the previous version of the Specification Update document.

### Table 4. Errata (Sheet 1 of 3)

| No.  | Stepping/Revision |    | Status                                                                                          | Errata Title                                                                                                                                           |  |  |

|------|-------------------|----|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO.  | В0                | B1 | Status                                                                                          | Lifeta fitte                                                                                                                                           |  |  |

| BI1. | Х                 | Х  | No Fix                                                                                          | IO_SMI Indication in SMRAM State Save Area May Be Set Incorrectly                                                                                      |  |  |

| BI2. | Х                 | Х  | No Fix                                                                                          | Writes to IA32_DEBUGCTL MSR May Fail When FREEZE_LBRS_ON_PMI Set                                                                                       |  |  |

| BI3. | Х                 | Х  | No Fix Address Reported by Machine-Check Architecture (MCA) on L2 Cache Errors May Be Incorrect |                                                                                                                                                        |  |  |

| BI4. | Х                 | Х  | No Fix                                                                                          | Pending x87 FPU Exceptions (#MF) Following STI May Be Serviced Before Higher Priority Interrupts                                                       |  |  |

| BI5. | Х                 | Х  | No Fix                                                                                          | Benign Exception After Double Fault May Not Cause Triple Fault Shutdown                                                                                |  |  |

| BI6. | Х                 | Х  | No Fix                                                                                          | IA32_MC1_STATUS MSR Bit [60] Does Not Reflect Machine Check Error Reporting Enable Correctly                                                           |  |  |

| BI7. | х                 | х  | No Fix                                                                                          | If Two Logical Processors Use Same CR3 Value but Configure APIC Virtualization Differently, Either May Operate as if APIC Virtualization Were Disabled |  |  |

| BI8. | Х                 | х  | No Fix                                                                                          | VM Exit Due to Fault While Delivering Software Interrupt May Save Incorrect Data Into VMCS                                                             |  |  |

### Table 4. Errata (Sheet 2 of 3)

| BI9.  BI10.  BI11.  BI12.  BI13. | x x x x x   | <b>B1</b> X  X | No Fix | VM Exit Occurring in IA-32e Mode May Not Produce VMX Abort When Expected                                                                                |  |

|----------------------------------|-------------|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BI10. BI11. BI12. BI13.          | x<br>x<br>x | Х              |        |                                                                                                                                                         |  |

| BI11. BI12. BI13.                | x<br>x      |                | No Fix |                                                                                                                                                         |  |

| BI12.                            | Х           | Х              |        | Performance Monitoring Event for Outstanding Bus Requests Ignores AnyThread Bit                                                                         |  |

| BI13.                            |             |                | No Fix | Thermal Interrupts Dropped During and While Exiting Deep Power-<br>Down State                                                                           |  |

|                                  |             | Х              | No Fix | Corruption of CS Segment Register During RSM While Transitioning From Real Mode to Protected Mode                                                       |  |

| DI14                             | Х           | Х              | No Fix | Performance Monitoring Counter With AnyThread Bit Set May Not<br>Count on Non-Active Thread                                                             |  |

| D114.                            | Х           | Х              | No Fix | GP and Fixed Performance Monitoring Counters With AnyThread Bit<br>Set May Not Accurately Count Only OS or Only USR Events                              |  |

| BI15.                            | Х           | Х              | No Fix | PMI Request Not Generated on Counter Overflow if Its OVF Bit Already Set in IA32_PERF_GLOBAL_STATUS                                                     |  |

| BI16.                            | Х           | Х              | No Fix | Processor May Use Incorrect Translation if TLBs Contain Two<br>Different Translations for Linear Address                                                |  |

| BI17.                            | Х           | Х              | No Fix | Write to APIC Register Sometimes May Appear to Have Not Occurred                                                                                        |  |

| BI18.                            | Х           | Х              | No Fix | xTPR Update Transaction Cycle, if Enabled, May Be Issued to FSB After Processor Issued Stop-Grant Special Cycle                                         |  |

| BI19.                            | Х           | X              | No Fix | Processor May Report #TS Instead of #GP Fault                                                                                                           |  |

| BI20.                            | Х           | Х              | No Fix | Writing Local Vector Table (LVT) When Interrupt Pending May Cause Unexpected Interrupt                                                                  |  |

| BI21.                            | Х           | X              | No Fix | MOV To/From Debug Registers Causes Debug Exception                                                                                                      |  |

| BI22.                            | Х           | Х              | No Fix | Using 2M/4M Pages When A20M# Asserted May Result in Incorrect Address Translations                                                                      |  |

| BI23.                            | Χ           | X              | No Fix | Values for LBR/BTS/BTM Will Be Incorrect After Exit From SMM                                                                                            |  |

| BI24.                            | Х           | Х              | No Fix | Incorrect Address Computed for Last Byte of FXSAVE/FXRSTOR Image Leads to Partial Memory Update                                                         |  |

| BI25.                            | Х           | Х              | No Fix | Thermal Interrupt Not Generated When Current Temperature Invalid                                                                                        |  |

| BI26.                            | Х           | Х              | No Fix | Programming Digital Thermal Sensor (DTS) Threshold May Cause Unexpected Thermal Interrupts                                                              |  |

| BI27.                            | Х           | Х              | No Fix | Returning to Real Mode From SMM With EFLAGS.VM Set May Result in Unpredictable System Behavior                                                          |  |

| BI28.                            | Х           | Х              | No Fix | Fault on ENTER Instruction May Result in Unexpected Values on Stack Frame                                                                               |  |

| BI29.                            | х           | Х              | No Fix | With TF (Trap Flag) Asserted, FP Instruction That Triggers Unmasked FP Exception May Take Single Step Trap Before Retirement of Instruction             |  |

| BI30.                            | х           | Х              | No Fix | Enabled Debug Breakpoint or Single Step Trap May Be Taken After MOV SS/POP SS Instruction if Followed by Floating Point Exception Signaling Instruction |  |

| BI31.                            | х           | Х              | No Fix | Code Segment Limit/Canonical Faults on RSM May Be Serviced<br>Before Higher Priority Interrupts/Exceptions and May Push Wrong<br>Address Onto Stack     |  |

| BI32.                            | Х           | Х              | No Fix | BTS (Branch Trace Store) and PEBS (Precise Event Based Sampling) May Update Memory Outside BTS/PEBS Buffer                                              |  |

| BI33.                            | Х           | Х              | No Fix | Single Step Interrupts With Floating Point Exception Pending May Be Mishandled                                                                          |  |

May 2013 Document Number: 324209-016

## Table 4. Errata (Sheet 3 of 3)

|       | Stepping/Revision |    |        |                                                                                                                                                                                    |  |  |

|-------|-------------------|----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| No.   | В0                | B1 | Status | Errata Title                                                                                                                                                                       |  |  |

| BI34. | Х                 | х  | No Fix | Unsynchronized Cross-Modifying Code Operations Can Cause Unexpected Instruction Execution Results                                                                                  |  |  |

| BI35. | Х                 | Х  | No Fix | LBR Stack May Not Be Frozen on PMI Request When FREEZE_LBRS_ON_PMI Set                                                                                                             |  |  |

| BI36. | Х                 | Х  | No Fix | PMI Request Not Generated on Counter Overflow if Its OVF Bit Already Set in IA32_PERF_GLOBAL_STATUS                                                                                |  |  |

| BI37. | Х                 | Х  | No Fix | Synchronous Reset of IA32_MPERF on IA32_APERF Overflow May Not Work                                                                                                                |  |  |

| BI38. | Х                 |    | Fixed  | Processor May Not Recognize Signal PWROK on Its Initial Assertion                                                                                                                  |  |  |

| BI39. | Х                 |    | Fixed  | Image on SDVO Display Clipped When Multiple Display Planes and SDVO Port Enabled                                                                                                   |  |  |

| BI40. | Х                 | Х  | No Fix | Large Amounts of LPC Bus Memory Reads and Writes May<br>Temporarily Starve Other I/O Devices                                                                                       |  |  |

| BI41. | Х                 | Х  | No Fix | Delayed I/O Device Memory Transactions Can Cause System Hang                                                                                                                       |  |  |

| BI42. | Х                 |    | Fixed  | Software Can Inadvertently Change SDVO Base Class Code Register                                                                                                                    |  |  |

| BI43. | Х                 |    | Fixed  | Voltage Supplied to Internal RTC Logic Violates Design Specification                                                                                                               |  |  |

| BI44. | Х                 |    | Fixed  | Flickering May be Observed on Display while Running Intensive<br>Graphics and Video Decoding Activities                                                                            |  |  |

| BI45. | Х                 | Х  | No Fix | C6 Request May Cause a Machine Check if the Other Logical Processor is in C4 or C6                                                                                                 |  |  |

| BI46. | Х                 | Х  | No Fix | EOI Transaction May Not be Sent if Software Enters Core C6 During an Interrupt Service Routine                                                                                     |  |  |

| BI47. | X                 | Х  | No Fix | PCNT Throttling May Cause System Hang During TM1 Thermal Event                                                                                                                     |  |  |

| BI48. | Х                 | Х  | No Fix | VMX Transitions May Set Bits 63:32 of the IA32_FMASK MSR                                                                                                                           |  |  |

| BI49. | X                 | Х  | No Fix | Writing the Local Vector Table (LVT) when an Interrupt is Pending<br>May Cause an Unexpected Interrupt                                                                             |  |  |

| BI50. | Х                 | Х  | No Fix | Clearing PCIe* Root Port's BME Bit With Pending Upstream Traffic Will Cause Internal Bus to Hang                                                                                   |  |  |

| BI51. | Х                 | Х  | No Fix | CPUID Instruction Returns Incorrect Brand String                                                                                                                                   |  |  |

| BI52. | Х                 |    | No Fix | The APIC Timer May Drift When Bus Ratios Less Than 6 Are Used                                                                                                                      |  |  |

| BI53. | X                 | Х  | No Fix | Extended Tags Are Always Used But Not Reported on PCIe* Root Ports                                                                                                                 |  |  |

| BI54. | х                 | Х  | No Fix | Outbound MSI From The PMU Can Result in Live Lock And/or System Hang When Simultaneously Occurring With an Inbound I/O Read                                                        |  |  |

| BI55. | Х                 | Х  | No Fix | SMBus Timing Violation                                                                                                                                                             |  |  |

| BI56. | Х                 | Х  | No Fix | RTC Does Not Detect a Coin Cell Battery Low Voltage Condition                                                                                                                      |  |  |

| BI57. | Х                 | Х  | No Fix | Complex Conditions Associated With Instruction Page Remapping or<br>Self/Cross-Modifying Code Execution May Lead to Unpredictable<br>System Behavior                               |  |  |

| BI58. |                   |    | No Fix | REP MOVS/STOS Executing With Fast Strings Enabled and Crossing Page Boundaries with Inconsistent Memory Types May Use an Incorrect Data Size or Lead to Memory-Ordering Violations |  |  |

| BI59. | ×                 | Х  | No Fix | Paging Structure Entry May be Used Before Accessed And Dirty Flags Are Updated                                                                                                     |  |  |

## **Table 5.** Specification Changes

| No. | Stepping |    | epping Document Title                                                                         |     | Specification Changes                                                                                                                              |

|-----|----------|----|-----------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | В0       | B1 | Document Title                                                                                |     | Specification changes                                                                                                                              |

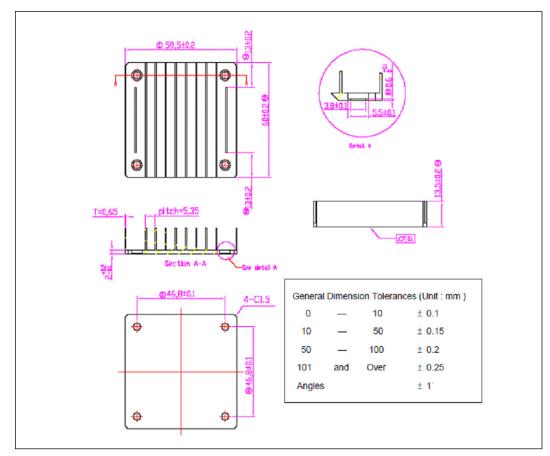

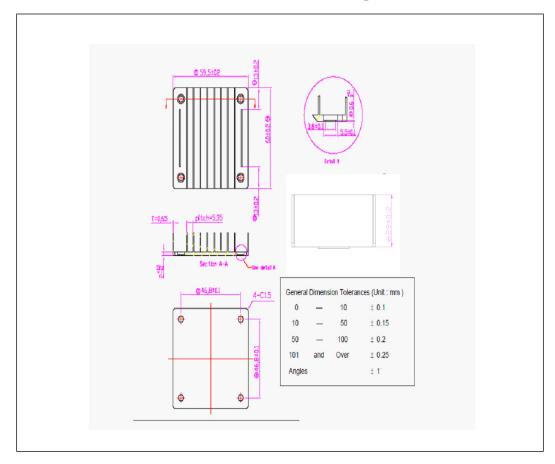

| 1.  | Х        | Х  | Intel <sup>®</sup> Atom™ Processor E6xx<br>Series Thermal and Mechanical<br>Design Guidelines |     | Heatsink Height Change                                                                                                                             |

| 2.  | X        | Х  | Intel <sup>®</sup> Atom™ Processor E6xx<br>Series Datasheet                                   | 004 | Changed VCC33RTC<br>Specification in "Operating<br>Condition Power Supply and<br>Reference DC Characteristics"<br>Table                            |

| 3.  | х        |    | Intel <sup>®</sup> Atom™ Processor E6xx<br>Series Datasheet                                   | 004 | Changed VCCRTCEXT<br>Specification from "Operating<br>Condition Power Supply and<br>Reference DC Characteristics"<br>Table                         |

| 4.  | х        | Х  | Intel <sup>®</sup> Atom™ Processor E6xx<br>Series Datasheet                                   | 004 | Changed V <sub>IH</sub> and V <sub>IL</sub><br>Specifications for RTCRST#,<br>PWROK, and RSMRST# in<br>"Active Signal DC<br>Characteristics" Table |

## **Table 6.** Specification Clarifications

| No.  | Stepping |    | Document Title                                              | Rev. | Specification Clarifications                         |

|------|----------|----|-------------------------------------------------------------|------|------------------------------------------------------|

| 140. | В0       | B1 | Document Title                                              |      | Specification clarifications                         |

| 1.   | х        | х  | Intel <sup>®</sup> Atom™ Processor E6xx<br>Series Datasheet | 003  | Add Information Related to<br>Memory-Mapped Accesses |

## **Table 7.** Document-only Changes (Sheet 1 of 2)

| No. | Step | ping | Document Title Rev.                                                     |      | Document-Only Changes                                                                                       |

|-----|------|------|-------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------|

| NO. | во   | B1   | Document Title                                                          | Rev. | Document-Only changes                                                                                       |

| § § | х    | х    | Intel <sup>®</sup> Atom™ Processor<br>E6xx Series Datasheet             | 003  |                                                                                                             |

| 2.  | х    | x    | Intel <sup>®</sup> Atom™ Processor<br>E6xx Series Datasheet             | 003  | Missing 06h (Host Data 0) Register<br>Description for SMBus Controller                                      |

| 3.  | х    | х    | Intel <sup>®</sup> Atom <sup>™</sup> Processor<br>E6xx Series Datasheet | 003  | Missing 07h (Host Data1) Register<br>Description for SMBus Controller                                       |

| 4.  | Х    | Х    | Intel <sup>®</sup> Atom™ Processor<br>E6xx Series Datasheet             | 003  | Changing BAR1 to WDTBA for WatchDog Timer Base Address Variable.                                            |

| 5.  | Х    | Х    | Intel <sup>®</sup> Atom™ Processor<br>E6xx Series Datasheet             | 003  | Added VIH, VIL and ILEAK<br>Specification and Remove VOH and<br>IOH Specification to CMOS1.05 Open<br>Drain |

| 6.  |      | х    | Intel <sup>®</sup> Atom™ Processor<br>E6xx Series Datasheet             | 003  | Updated GVD.FD Register Bit 0<br>Description                                                                |

May 2013 Document Number: 324209-016

#### **Document-only Changes (Sheet 2 of 2)** Table 7.

| No. | Stepping |   | Document Title                                              | Rev.                  | Document-Only Changes                                                                                                                  |

|-----|----------|---|-------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| NO. | BO B1    |   | Rev.                                                        | Document-Only Changes |                                                                                                                                        |

| 7.  | Х        | Х | Intel <sup>®</sup> Atom™ Processor<br>E6xx Series Datasheet | 003                   | Updated Note Text in the Operating<br>Condition Power Supply and<br>Reference DC Characteristics Table                                 |

| 8.  |          | х | Intel <sup>®</sup> Atom™ Processor<br>E6xx Series Datasheet | 003                   | Corrected Bus 0, Device 3 PCI<br>Configuration Register Default                                                                        |

| 9.  |          | Х | Intel <sup>®</sup> Atom™ Processor<br>E6xx Series Datasheet | 003                   | Update to Specification Change 4.<br>Updated Notes for "Operating<br>Condition Power Supply and<br>Reference DC Characteristics" Table |

## **General Product Information**

The Intel<sup>®</sup> Atom<sup>™</sup> Processor E6xx Series can be identified by the following register

#### **Identification Information (Sheet 1 of 2)** Table 8.

| Stepping | CPUID                                        | Vendor ID <sup>1</sup>                                                                                                                                                                          | Device ID <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Revision<br>Number <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В0       | 0020661h                                     | 8086                                                                                                                                                                                            | 4115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| В0       | 0020661h                                     | 8086                                                                                                                                                                                            | 4115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| В0       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| В0       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| В0       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| В0       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| В0       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| В0       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B1       | 0020661h                                     | 8086                                                                                                                                                                                            | 4115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B1       | 0020661h                                     | 8086                                                                                                                                                                                            | 4115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B1       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B1       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B1       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B1       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B1       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B1       | 0020661h                                     | 8086                                                                                                                                                                                            | 4114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | B0 B0 B0 B0 B0 B0 B0 B0 B1 B1 B1 B1 B1 B1 B1 | B0 0020661h B1 0020661h | B0       0020661h       8086         B1       0020661h       8086 | B0       0020661h       8086       4115         B0       0020661h       8086       4115         B0       0020661h       8086       4114         B1       0020661h       8086       4115         B1       0020661h       8086       4114         B1       0020661h       8086       4114 |

### Notes:

- The Vendor ID corresponds to bits [15:0] of the VID Vendor Identification Register located at Offset 00–01h in the PCI Bus 0 Device 0 Function 0 configuration space. 1.

- The Device ID corresponds to bits [15:0] of the DID Device Identification Register located at Offset 2.

- 72–03h in the PCI Bus 0 Device 0 Function 0 configuration space.

The Revision Number corresponds to bits [7:0] of the RID Revision Identification Register located at Offset 08h in the PCI Bus 0 Device 31 Function 0 configuration space. 3.

May 2013

Document Number: 324209-016

The Intel  $^{\circledR}$  Atom  $^{\intercal M}$  Processor E6xx Series stepping can be identified by the following component markings:

#### Table 9. **Component Markings**

| Stepping | MM#    | SPEC Code | Notes                            |

|----------|--------|-----------|----------------------------------|

| B0 PRQ   | 909841 | SLH94     | 1.6 GHz (Commercial Temperature) |

| B0 PRQ   | 905523 | SLH54     | 1.3 GHz (Commercial Temperature) |

| B0 PRQ   | 905528 | SLH55     | 1.0 GHz (Commercial Temperature) |

| B0 PRQ   | 905531 | SLH56     | 0.6 GHz (Commercial Temperature) |

| B0 PRQ   | 909839 | SLH95     | 1.6 GHz (Extended Temperature)   |

| B0 PRQ   | 905804 | SLH5L     | 1.3 GHz (Extended Temperature)   |

| B0 PRQ   | 905805 | SLH5M     | 1.0 GHz (Extended Temperature)   |

| B0 PRQ   | 905806 | SLH5N     | 0.6 GHz (Extended Temperature)   |

| B1 ES    | 913796 | QP4S      | 0.6 GHz (Commercial Temperature) |

| B1 ES    | 913784 | QP4T      | 1.0 GHz (Commercial Temperature) |

| B1 ES    | 913750 | QP4U      | 1.3 GHz (Commercial Temperature) |

| B1 ES    | 914597 | QP4V      | 1.6 GHz (Commercial Temperature) |

| B1 QS    | 915059 | QP7P      | 0.6 GHz (Extended Temperature)   |

| B1 QS    | 915058 | QP7Q      | 1.0 GHz (Extended Temperature)   |

| B1 QS    | 915057 | QP7R      | 1.3 GHz (Extended Temperature)   |

| B1 QS    | 915056 | QP7S      | 1.6 GHz (Extended Temperature)   |

| B1 PRQ   | 913706 | SLJ35     | 1.6 GHz (Commercial Temperature) |

| B1 PRQ   | 913720 | SLJ34     | 1.3 GHz (Commercial Temperature) |

| B1 PRQ   | 913761 | SLJ33     | 1.0 GHz (Commercial Temperature) |

| B1 PRQ   | 913773 | SLJ32     | 0.6 GHz (Commercial Temperature) |

| B1 PRQ   | 913549 | SLJ39     | 1.6 GHz (Extended Temperature)   |

| B1 PRQ   | 913571 | SLJ38     | 1.3 GHz (Extended Temperature)   |

| B1 PRQ   | 913650 | SLJ37     | 1.0 GHz (Extended Temperature)   |

| B1 PRQ   | 913695 | SLJ36     | 0.6 GHz (Extended Temperature)   |

| Legend for Figure 1           | Mark Text                    | Notes      |

|-------------------------------|------------------------------|------------|

| GRP1INE1                      | INTEL {M} {C}'09 {e1}        | 1, 2, 3    |

| GRP2LINE1                     | {FPO} {SPEC Code}            | 4          |

|                               |                              |            |

| Legend for Figure 2           | Mark Text                    | Notes      |

| Legend for Figure 2  GRP1INE1 | Mark Text  {FPO} {SPEC Code} | Notes<br>4 |

- M = Manufacturing copyright

- 2.

- C = Copyright line e1 = ROHS marking FPO = Wafer lot #

May 2013 Document Number: 324209-016

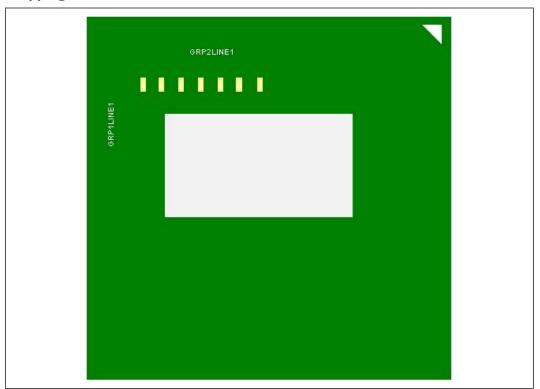

Figure 1. Top-Side Marking Example For Intel<sup>®</sup> Atom™ Processor E6xx Series B0 Stepping

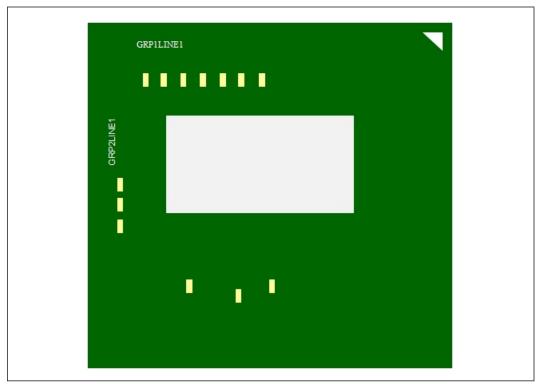

Top-Side Marking Example For Intel<sup>®</sup> Atom<sup>™</sup> Processor E6xx Series B1 Stepping Figure 2.

May 2013

Document Number: 324209-016

## **Microcode Updates**

Each unique processor stepping/package combination has an associated microcode update that, when applied, constitutes a supported processor (that is, Specified processor = Processor Stepping + Microcode Update). The proper microcode update must be loaded on each processor in a system. the proper microcode update is defined as the latest production microcode update available from Intel for a given family, model, and stepping of the processor. Any processor that does not have the correct microcode update loaded is considered to be operating out of specification. Contact your Intel Field Representative to receive the latest production microcode updates.

## Table 10. Intel<sup>®</sup> Atom™ Processor E6xx Series on 45-nm Process Microcode Update Guide

| Microcode<br>Update | Microcode<br>Update<br>Release<br>Date | Processor<br>Signature | Microcode<br>Update<br>Revision | Revision ID | Core<br>Stepping | Workaround<br>for Erratum |