# Intel® System Controller Hub (Intel® SCH)

Datasheet

May 2010

Document Number: 319537-003US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The Intel® System Controller Hub (Intel® SCH) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

Intel® High Definition Audio (Intel® HD Audio) requires a system with an appropriate Intel chipset and a motherboard with an appropriate codec and the necessary drivers installed. System sound quality will vary depending on actual implementation, controller, codec, drivers and speakers. For more information about Intel® High Definition Audio (Intel® HD Audio), refer to http://www.intel.com/.

$I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Intel® Graphics Media Accelerator 500 (Intel® GMA 500), Intel® High Definition Audio (Intel® HD Audio), Enhanced Intel SpeedStep® Technology, Intel® Atom<sup>TM</sup>, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008–2010, Intel Corporation. All Rights Reserved.

# Contents

| 1 | Intro | oduction                                                          | 19 |

|---|-------|-------------------------------------------------------------------|----|

|   | 1.1   | Terminology                                                       | 20 |

|   | 1.2   | Reference Documents                                               | 22 |

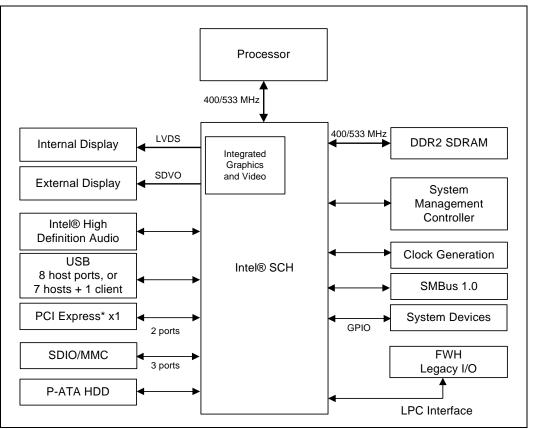

|   | 1.3   | Overview                                                          | 23 |

|   |       | 1.3.1 Processor Interface                                         | 23 |

|   |       | 1.3.2 System Memory Controller                                    |    |

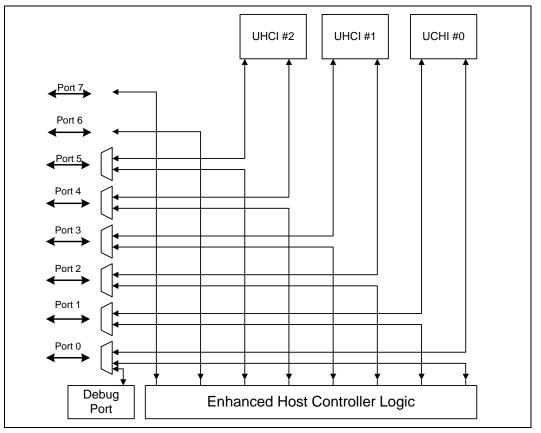

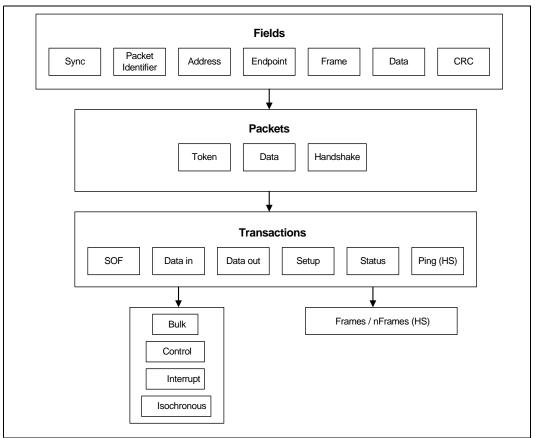

|   |       | 1.3.3 USB Host                                                    |    |

|   |       | 1.3.4 USB Client                                                  |    |

|   |       | 1.3.5 PCI Express*                                                |    |

|   |       | 1.3.6 LPC Interface                                               |    |

|   |       | 1.3.7 Parallel ATA (PATA)                                         |    |

|   |       | 1.3.8 Intel® Graphics Media Accelerator 500 (Intel® GMA 500)      |    |

|   |       | 1.3.9 Display Interfaces                                          |    |

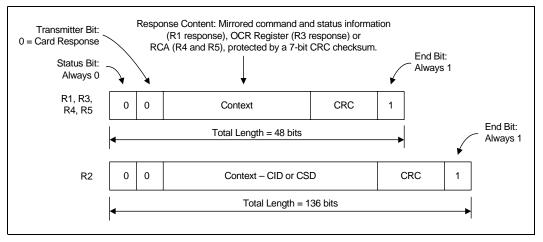

|   |       | 1.3.10 Secure Digital I/O (SDIO)/Multimedia Card (MMC) Controller |    |

|   |       | 1.3.11 SMBus Host Controller                                      |    |

|   |       |                                                                   |    |

|   |       | 1.3.12 Intel® High Definition Audio (Intel® HD Audio) Controller  |    |

|   |       | 1.3.13 General Purpose I/O (GPIO)                                 |    |

|   |       | 1.3.14 Power Management                                           |    |

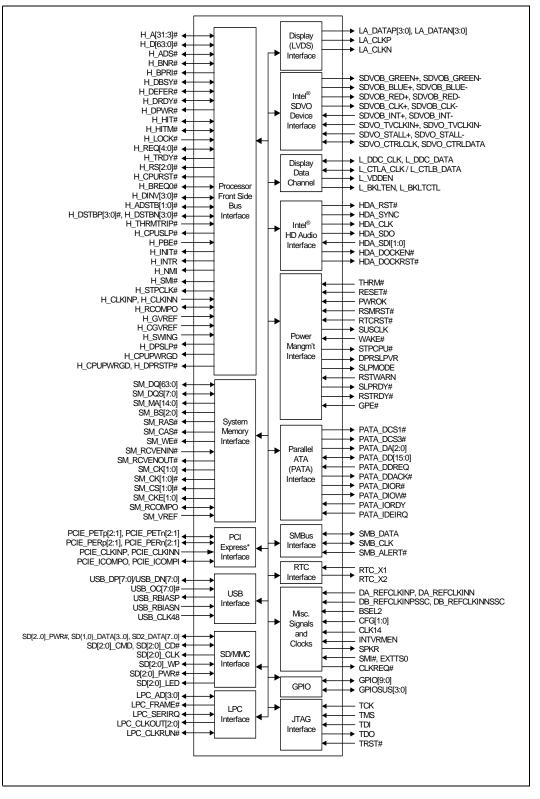

| 2 | Signa | al Description                                                    | 27 |

|   | 2.1   | Host Interface Signals                                            |    |

|   | 2.2   | System Memory Signals                                             |    |

|   | 2.3   | Integrated Display Interfaces                                     |    |

|   |       | 2.3.1 LVDS Signals                                                |    |

|   |       | 2.3.2 Serial Digital Video Output (SDVO) Signals                  |    |

|   |       | 2.3.3 Display Data Channel (DDC) and GMBus Support                |    |

|   | 2.4   | Universal Serial Bus (USB) Signals                                |    |

|   | 2.5   | PCI Express* Signals                                              |    |

|   | 2.6   | Secure Digital I/O (SDIO)/MultiMedia Card (MMC) Signals           |    |

|   | 2.7   | Parallel ATA (PATA) Signals                                       |    |

|   | 2.8   | Intel HD Audio Interface                                          |    |

|   | 2.9   | LPC Interface                                                     |    |

|   | 2.10  | SMBus Interface                                                   |    |

|   | 2.10  | Power Management Interface                                        |    |

|   | 2.11  | Real Time Clock Interface                                         |    |

|   | 2.12  |                                                                   |    |

|   |       | JTAG Interface                                                    |    |

|   | 2.14  | Miscellaneous Signals and Clocks                                  |    |

|   | 2.15  | General Purpose I/O                                               |    |

|   | 2.16  | Power and Ground Signals                                          |    |

|   | 2.17  | Functional Straps                                                 | 46 |

| 3 | Pin S | states                                                            | 47 |

|   | 3.1   | Pin Reset States                                                  | 47 |

|   | 3.2   | Integrated Termination Resistors                                  |    |

| 4 |       | em Clock Domains                                                  |    |

| 5 | •     | ster and Memory Mapping                                           |    |

| 5 | -     |                                                                   |    |

|   | 5.1   | Intel® SCH Register Introduction                                  |    |

|   | 5.2   | PCI Configuration Map                                             | 59 |

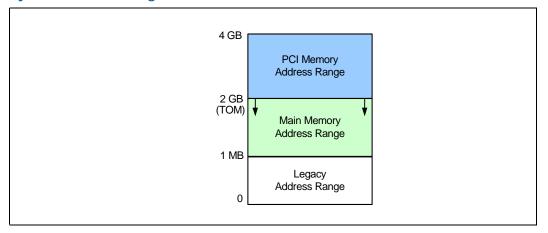

|   | 5.3 | Systen   | n Memory Map                                    |     |

|---|-----|----------|-------------------------------------------------|-----|

|   |     | 5.3.1    | Legacy Video Area (A0000h – BFFFFh)             | .62 |

|   |     | 5.3.2    | Expansion Area (C0000h – DFFFFh)                | .62 |

|   |     | 5.3.3    | Extended System BIOS Area (E0000h – EFFFFh)     | .62 |

|   |     | 5.3.4    | System BIOS Area (F0000h – FFFFFh)              |     |

|   |     | 5.3.5    | EHCI Controller Area                            |     |

|   |     | 5.3.6    | Programmable Attribute Map (PAM)                |     |

|   |     | 5.3.7    | Top of Memory Segment (TSEG)                    |     |

|   |     | 5.3.8    | APIC Configuration Space (FEC00000h – FECFFFFh) |     |

|   |     | 5.3.9    | High BIOS Area                                  |     |

|   |     |          | Boot Block Update                               |     |

|   |     |          | Memory Shadowing                                |     |

|   |     |          | Locked Transactions                             |     |

|   | Γ 4 |          |                                                 |     |

|   | 5.4 |          | dress Space                                     |     |

|   |     | 5.4.1    | Fixed I/O Decode Ranges                         |     |

|   |     | 5.4.2    | Variable I/O Decode Ranges                      |     |

|   | 5.5 |          | pped Registers                                  | .67 |

|   |     | 5.5.1    | NSC-NMI Status and Control Register             |     |

|   |     | 5.5.2    | NMIE—NMI Enable Register                        |     |

|   |     | 5.5.3    | CONFIG_ADDRESS—Configuration Address Register   | .68 |

|   |     | 5.5.4    | RSTC—Reset Control Register                     | .69 |

|   |     | 5.5.5    | CONFIG_DATA—Configuration Data Register         | .69 |

| 6 | Con | oral Chi | pset Configuration                              | 71  |

| 0 |     |          | · · ·                                           |     |

|   | 6.1 |          | omplex Capability                               |     |

|   |     | 6.1.1    | RCTCL—Root Complex Topology Capabilities List   |     |

|   |     | 6.1.2    | ESD—Element Self Description                    |     |

|   |     | 6.1.3    | HDD—Intel® HD Audio Description                 |     |

|   |     | 6.1.4    | HDBA—Intel® HD Audio Base Address               |     |

|   | 6.2 | Interru  | Ipt Pin and Routing Configuration               | .74 |

|   |     | 6.2.1    | Interrupt Pin Configuration                     |     |

|   |     | 6.2.2    | Interrupt Route Configuration                   | .77 |

|   | 6.3 | Genera   | al Configuration Register                       | .80 |

|   |     | 6.3.1    | RC-RTC Configuration Register                   |     |

| - |     |          |                                                 |     |

| 7 |     | -        | (D0:F0)                                         |     |

|   | 7.1 |          | onal Description                                |     |

|   |     | 7.1.1    | Dynamic Bus Inversion                           |     |

|   |     | 7.1.2    | FSB Interrupt Overview                          |     |

|   |     | 7.1.3    | CPU BIST Strap                                  | .82 |

|   | 7.2 | Host P   | CI Configuration Registers                      | .82 |

|   |     | 7.2.1    | VID—Identification Register                     | .82 |

|   |     | 7.2.2    | DID—Identification Register                     |     |

|   |     | 7.2.3    | PCICMD—PCI Command Register                     |     |

|   |     | 7.2.4    | PCISTS—PCI Status Register                      |     |

|   |     | 7.2.5    | RID—Revision Identification Register            |     |

|   |     | 7.2.6    | CC—Class Code Register                          |     |

|   |     | 7.2.7    | SS—Subsystem Identifiers Register               |     |

|   |     | 7.2.8    | Miscellaneous (Port 05h)                        |     |

|   |     |          |                                                 |     |

| 8 | Men | nory Cor | ntroller (D0:F0)                                | .89 |

|   | 8.1 | Functio  | onal Overview                                   |     |

|   |     | 8.1.1    | DRAM Frequencies and Data Rates                 | .89 |

|   |     | 8.1.2    | DRAM Command Scheduling                         |     |

|   |     | 8.1.3    | Page Management                                 |     |

|   |     |          | 5 5                                             |     |

|   | 8.2   | DRAM<br>8.2.1 | Technologies and Organization<br>DRAM Address Mapping     |      |

|---|-------|---------------|-----------------------------------------------------------|------|

|   | 8.3   | DRAM          | Clock Generation                                          |      |

|   | 8.4   |               | On-Die Termination                                        |      |

|   | 8.5   |               | Power Management                                          |      |

|   |       | 8.5.1         | CKE Powerdown                                             |      |

|   |       | 8.5.2         | Interface High-Impedance                                  |      |

|   |       | 8.5.3         | Refresh                                                   |      |

|   |       | 8.5.4         | Self-Refresh                                              |      |

|   |       | 8.5.5         | Dynamic Self-Refresh                                      |      |

|   |       | 8.5.6         | DDR2 Voltage                                              |      |

| 9 | Grapl | hics, Vi      | ideo, and Display (D2:F0)                                 |      |

|   | 9.1   | Graphi        | ics Overview                                              | . 95 |

|   |       | 9.1.1         | 3-D Core Key Features                                     | . 95 |

|   |       | 9.1.2         | Shading Engine Key Features                               | . 95 |

|   |       | 9.1.3         | Vertex Processing                                         | . 96 |

|   |       | 9.1.4         | Pixel Processing                                          | . 97 |

|   |       | 9.1.5         | Unified Shader                                            | . 97 |

|   |       | 9.1.6         | Multi Level Cache                                         | . 98 |

|   | 9.2   | Video         | Decode Overview                                           | . 98 |

|   |       | 9.2.1         | Entropy Coding                                            | . 99 |

|   |       | 9.2.2         | Motion Compensation                                       | . 99 |

|   |       | 9.2.3         | Deblocking                                                | 100  |

|   |       | 9.2.4         | Output Reference Frame Storage Format                     | 100  |

|   | 9.3   | Displa        | y Overview                                                | 101  |

|   |       | 9.3.1         | Planes                                                    | 101  |

|   |       | 9.3.2         | Display Pipes                                             | 102  |

|   |       | 9.3.3         | Display Ports                                             | 102  |

|   | 9.4   | Config        | uration Registers                                         |      |

|   |       | 9.4.1         | VID—Vendor Identification Register                        |      |

|   |       | 9.4.2         | DID—Device Identification Register                        |      |

|   |       | 9.4.3         | PCICMD—PCI Command Register                               |      |

|   |       | 9.4.4         | PCISTS—PCI Status Register                                |      |

|   |       | 9.4.5         | RID—Revision Identification                               |      |

|   |       | 9.4.6         | CC—Class Codes Register                                   |      |

|   |       | 9.4.7         | HEADTYP—Header Type Register                              |      |

|   |       | 9.4.8         | MEM_BASE—Memory Mapped Base Address Register              |      |

|   |       | 9.4.9         | IO_BASE—I/O Base Address Register                         |      |

|   |       |               | GMEM_BASE—Graphics Memory Base Address Register           |      |

|   |       |               | GTT_BASE—Graphics Translation Table Base Address Register |      |

|   |       | 9.4.12        | SS—Subsystem Identifiers                                  | 109  |

|   |       |               | CAP_PTR—Capabilities Pointer Register                     |      |

|   |       |               | INT_LN—Interrupt Line Register                            |      |

|   |       |               | INT_PN—Interrupt Pin Register                             |      |

|   |       |               | GC—Graphics Control Register                              |      |

|   |       |               | SSRW—Software Scratch Read/Write Register                 |      |

|   |       |               | BSM—Base of Stolen Memory Register                        |      |

|   |       |               | MSAC—Multi Size Aperture Control                          |      |

|   |       |               | MSI_CAPID—MSI Capability Register                         |      |

|   |       |               | NXT_PTR3—Next Item Pointer #3 Register                    |      |

|   |       |               | MSI_CTL—Message Control Register                          |      |

|   |       |               | MSI_ADR—Message Address Register                          |      |

|   |       |               | MSI_DATA—Message Data Register                            |      |

|   |       | 9.4.25        | VEND_CAPID—Vendor Capability Register                     | 113  |

|    |       | 9.4.26  | NXT_PTR2—Next Item Pointer #2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 113 |

|----|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    |       | 9.4.27  | FD—Function Disable Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 114 |

|    |       | 9.4.28  | PM_CAPID—Power Management Capabilities ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 114 |

|    |       |         | NXT_PTR1—Next Item Pointer #1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|    |       |         | PM_CAP—Power Management Capabilities Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|    |       |         | PM_CTL_STS—Power Management Control/Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|    |       |         | SWSCISMI—Software SCI/SMI Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|    |       |         | ASLE—System Display Event Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|    |       |         | GCR-Graphics Clock Ratio Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|    |       |         | LBB—Legacy Backlight Brightness Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|    |       |         | ASLS—ASL Storage Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 10 | Intol |         | udio (D27:F0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 10 |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|    | 10.1  |         | nal Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|    |       |         | Docking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|    | 10.0  |         | Low Voltage (LV) Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|    | 10.2  |         | nfiguration Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|    |       |         | VID—Vendor Identification Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|    |       |         | DID—Device Identification Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|    |       |         | PCICMD—PCI Command Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|    |       |         | PCISTS—PCI Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|    |       |         | RID—Revision Identification Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|    |       |         | CC—Class Code Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|    |       |         | CLS—Cache Line Size Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|    |       |         | LT—Latency Timer Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|    |       |         | HEADTYP—Header Type Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|    |       |         | DLBAR—Lower Base Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|    |       | 10.2.11 | I UBAR—Upper Base Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 127 |

|    |       |         | 2SS—Sub System Identifiers Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|    |       |         | CAP_PTR—Capabilities Pointer Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|    |       |         | INTLN—Interrupt Line Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|    |       |         | 5INTPN—Interrupt Pin Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|    |       |         | 5HDCTL—HD Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|    |       | 10.2.17 | 7 DCKCTL—Docking Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 129 |

|    |       |         | BDCKSTS—Docking Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|    |       | 10.2.19 | PM_CAPID—PCI Power Management Capability ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 130 |

|    |       |         | OPM_CAP—Power Management Capabilities Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|    |       | 10.2.21 | IPM_CTL_STS—Power Management Control and Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 131 |

|    |       | 10.2.22 | 2MSI_CAPID—MSI Capability ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 131 |

|    |       |         | 3MSI_CTL—MSI Message Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|    |       | 10.2.24 | Image: Model         Image: Model< | 132 |

|    |       | 10.2.25 | 5MSI_DATA—MSI Message Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 132 |