# Boosted Class D Amplifier with Speaker-Protection Monitoring and Flash LED Drivers

### Mono Class D Speaker Amplifier

- · Two-level Class G operation:

- · Boosted: 5 V nominal

- · Bypassed: battery voltage is supplied directly

- · 2.5-mA quiescent current, monitors powered down

- 1.7 W into 8 Ω (@ 10% THD+N)

- 102-dB signal-to-noise ratio (SNR, A-weighted)

- Idle channel noise 25 μVrms (A-weighted)

- · 90% efficiency

#### **Audio Input and Gain**

- · One differential analog input

- · Speaker gain:

- 9, 12, 15, and 18 dB and mute

- Pop suppression, zero-crossing detect transitions

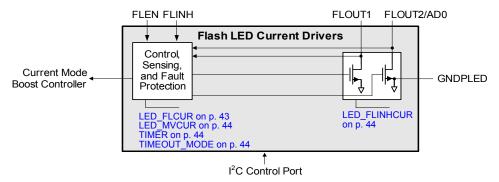

#### Flash LED Drivers

- Integrated dual LED drivers using the following:

- · Boost supply output voltage

- · Dual matched current regulators, 750 mA max each

- Programmable setting for Flash Mode current: 50–750 mA, in 50-mA steps

- Programmable setting for Flash-Inhibit Mode current: 50–350 mA, in 50-mA steps

- Programmable setting for Movie Mode current: 150, 120, 100, 80, 60, 40, 20 mA

- Programmable flash timer setting: 50–500 ms, in 25-ms steps

- Dedicated pin for flash trigger (FLEN)

- · Dedicated pin for flash inhibit (FLINH)

- Thermally managed through boost-voltage regulation

(Features continue on page 2)

#### **Monitors and Protection**

- · Protection:

- · Latched overtemperature shutdown

- Latched amplifier output short circuit shutdown

- · LED short or open detection and LED driver shutdown

- · Flash inhibit LED current reduction

- · Low battery flash LED current reduction

- VP undervoltage lockout (UVLO) shutdown

- · Programmable boost inductor current limiting

- Audio and LED shutdown upon stopped MCLK, with autorecovery

- · Interrupt driven error reporting

- · Speaker current and voltage monitoring:

- 16-bit resolution

- 60-dB dynamic range (unweighted) for voltage

- 56-dB dynamic range (unweighted) for current

- · Bused over I2S bus

- · Battery voltage monitoring:

- · 7-bit resolution

- Bused over I2S and I2C bus

- System reset

#### I2C Control Settings and Registers

- · Low-power standby

- · LED and audio power budgeting programmable settings

- Boost inductor current limit programmable setting

- · Speaker programmable settings:

- · Pop suppression through zero-crossing transitions

- · Gain and mute

- · Battery voltage monitor register, 8 bits

- · LED driver programmable settings:

- · Flash current register

- Flash inhibit current register

- Movie Mode current register

- · Flash timer register

- · Error status bit, including the following:

- · Stopped MCLK error

- Low battery detection with programmable thresholds

- VP UVLO error

- · Overtemperature warning

- Overtemperature error

- · Boost converter overvoltage error

- · Boost inductor current-limiting error

- · Amplifier short-circuit error

- · Shorted or open LED error

#### I2S Reporting

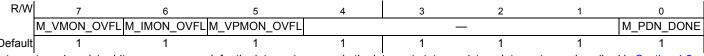

- Monitoring:

- · Speaker voltage monitor

- · Speaker current monitor

- · Battery voltage monitor

- · Error reporting:

- · VP UVLO shutdown error

- · Overtemperature warning

- Overtemperature error

- · Boost converter overvoltage error

- · Boost inductor current limiting error

- · Amplifier short-circuit error

- · Speaker voltage monitor overflow error

- · Speaker current monitor overflow error

- Battery voltage monitor overflow error

- · Status reporting:

- · Power-down done

- · LED flash event

- · LED Movie Mode event

- · Flash timer on

#### **Package**

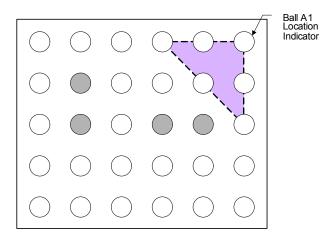

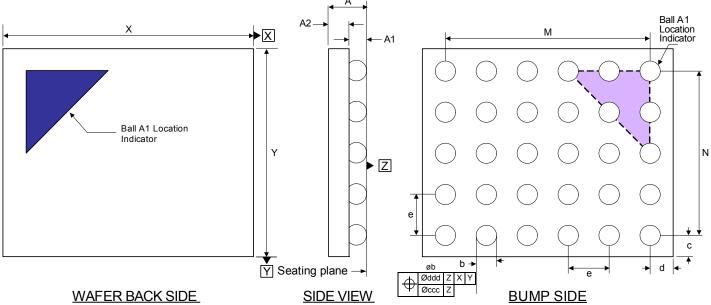

· 30-ball WLCSP

### **Applications**

- · Smart phones

- Tablets

#### **General Description**

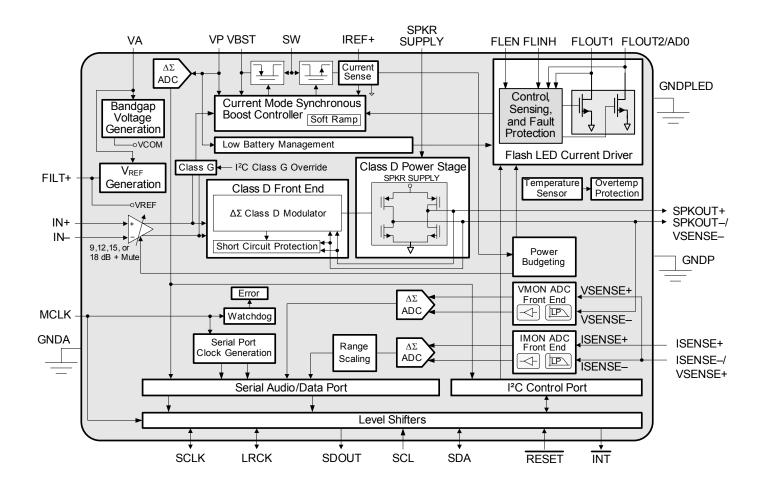

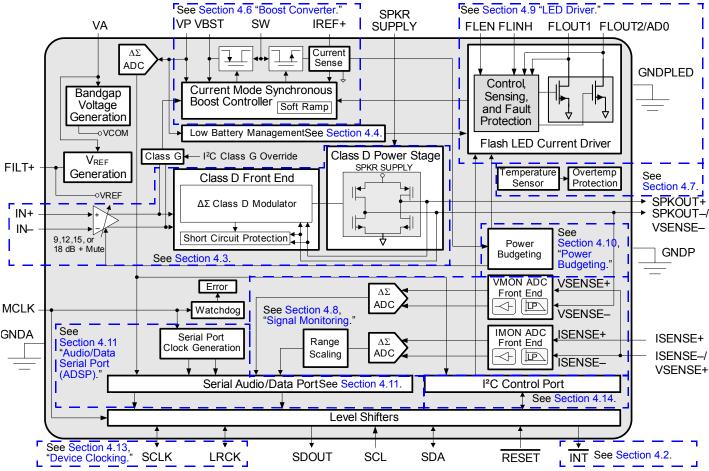

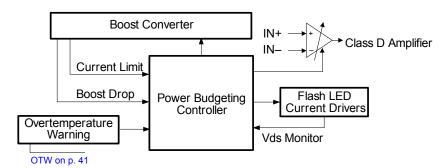

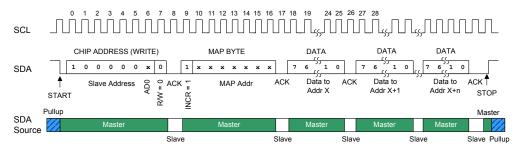

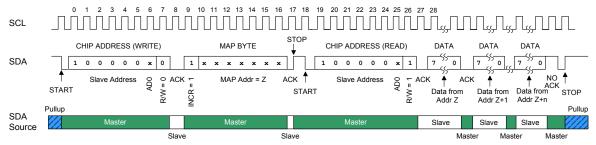

The CS35L32 is a low-quiescent power-integrated audio IC, with a mono full-bridge Class D speaker amplifier operating with a self-boosted Class G supply. Audio input is received differentially. Pop-and-click reduction is achieved with zero-crossing transitions at turn-on, turn-off and upon gain changes. Communication with the host processor is done using an I<sup>2</sup>C interface. In addition, an I<sup>2</sup>S bus is used to send monitor and status data.

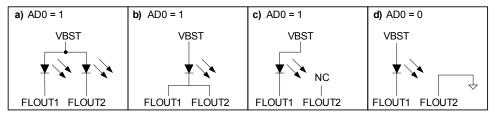

When two CS35L32 <u>devices</u> are available on the same board, each is identified by its I<sup>2</sup>C chip address. Upon power-up or upon deasserting RESET, each CS35L32 reads the AD0 pin logic level and configures its I<sup>2</sup>C device address.

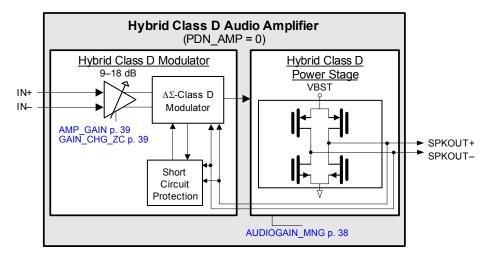

The speaker amplifier, using closed-loop  $\Delta\Sigma$  modulation, achieves low levels of distortion. Class D amplifier efficiency allows operation at higher speaker power levels without generating excessive heat and without wasting power. Automatic Class G operation using a boosted supply to the speaker allows for even higher powers and higher crest factor. With a boosted speaker supply, operation at a fixed 5 V is achieved independently of line supplied battery voltage. The user can disable Class G operation.

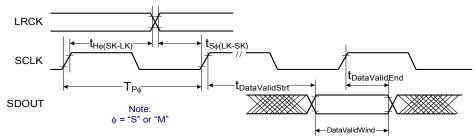

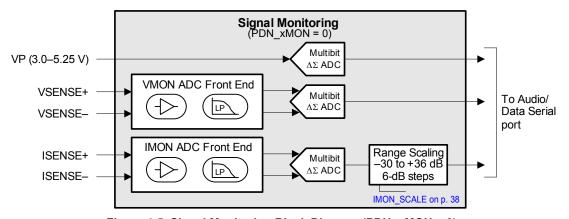

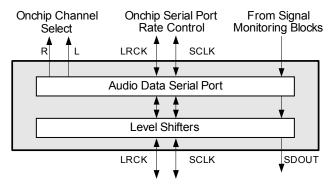

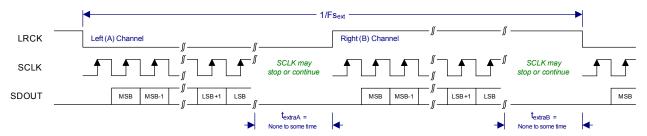

The battery voltage, speaker voltage, and speaker current signals are monitored, digitized using  $\Delta\Sigma$  converters, and serialized over an I<sup>2</sup>S bus. The speaker monitoring signals are part of a speaker-protection algorithm that is managed externally to the CS35L32. Outgoing data is sent over I<sup>2</sup>S with the CS35L32 in Slave or Master Mode. Battery voltage monitor data is accessible through I<sup>2</sup>C.

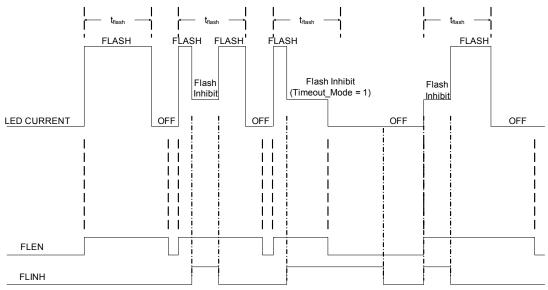

An integrated dual LED driver operates up to two LEDs in Flash Mode or Movie Mode. A flash event is triggered by an external signal. A flash-inhibit event is triggered by an external signal, and causes a reduction in flash current. A timer is provided for flash and flash inhibit events. Movie Mode operation has no timer and starts and ends via an I<sup>2</sup>C command. Flash and Movie Mode current levels, as well as the flash timer are I<sup>2</sup>C programmable.

Total power consumption when powering LEDs in Flash Mode or Movie Mode, and powering audio simultaneously, is managed by the user's choices in programming the current limit and in power budgeting. The primary goal is to manage audio and LED loads so the boost converter is not current limited and so the CS35L32 does not shut down due to overheating.

A latched shutdown of the audio amplifier occurs in the event of an output short pin to ground, pin to supply, or pin to pin. A latched shutdown of the CS35L32 also occurs on overtemperature. An LED driver shutdown occurs in the event of a shorted or open LED. The CS35L32 shuts down in the event of a battery (VP) undervoltage and autorecovers when the battery voltage recovers. The CS35L32 shuts down in the event of a stopped MCLK and autorecovers when MCLK recovers.

The CS35L32 responds to detection of a low battery in the presence of a flash event by reducing flash current and autorecovers when the battery voltage recovers.

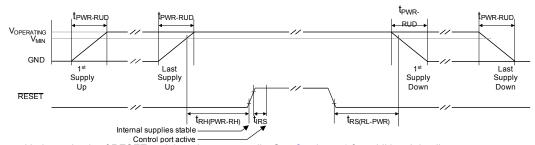

The CS35L32 is reset by asserting RESET. CS35L32 power up and power down are managed through the RESET pin.

The CS35L32 is available in a 30-ball WLCSP package in the temperature range –10 to +70°C.

### **Table of Contents**

| 1 Pin Descriptions                                                   | 6 Register Quick Reference                           | . 35 |

|----------------------------------------------------------------------|------------------------------------------------------|------|

| 2 Typical Connection Diagram                                         | 7 Register Descriptions                              | . 36 |

| 3 Characteristics and Specifications                                 | 7.1 Device ID A and B                                | . 36 |

| Table 3-1. Recommended Operating Conditions                          | 7.2 Device ID C and D                                | . 36 |

| Table 3-2. Absolute Maximum Ratings                                  | 7.3 Device ID E                                      | . 36 |

| Table 3-3. DC Characteristics                                        | 7.4 Revision ID                                      |      |

| Table 3-4. Boost Converter Characteristics                           |                                                      |      |

| Table 3-5. LED Drive Characteristics                                 |                                                      | . 37 |

| Table 3-6. Speaker Amplifier Output Characteristics                  | 7.7 Clocking Control                                 | . 37 |

| Table 3-7. Signal Monitoring Characteristics                         | 7.8 Low Battery Thresholds                           | . 37 |

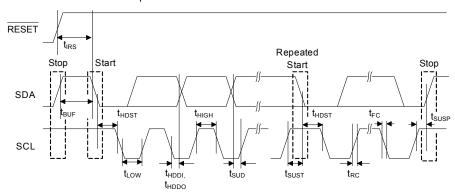

| Table 3-8. Digital Interface Specifications and Characteristics 1    | 7.9 Battery Voltage Monitor                          | . 38 |

| Table 3-9. PŠRR Characteristics                                      | 7.10 Boost Converter Peak Current Protection Control | . 38 |

| Table 3-10. Power Consumption                                        | 7.11 Scaling                                         | . 38 |

| Table 3-11. Switching Specifications: Power, Reset, Master Clocks 12 | 7.12 LED and Audio Power-Budget Management           | . 38 |

| Table 3-12. Switching Specifications: ADSP in I2S Mode               | 7.13 ADSP Control                                    | . 39 |

| Table 3-13. Switching Specifications: I <sup>2</sup> C Control Port  |                                                      | . 39 |

| 4 Functional Description1                                            | 7.15 Protection Release Control                      | . 39 |

| 4.1 Power Supplies                                                   | 7.16 Interrupt Mask 1                                | . 40 |

| 4.2 Interrupts                                                       |                                                      | . 40 |

| 4.3 Speaker Amplifier                                                | 7.18 Interrupt Mask 3                                | . 41 |

| 4.4 Low-Battery Management                                           | 7.19 Interrupt Status 1 (Audio)                      | . 41 |

| 4.5 Undervoltage Lockout (UVLO)                                      | 7.20 Interrupt Status 2 (Monitors)                   | . 42 |

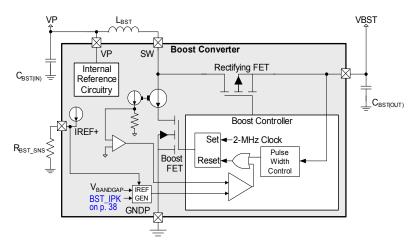

| 4.6 Boost Converter                                                  | 7.21 Interrupt Status 3 (LEDs and Boost Converter)   | . 42 |

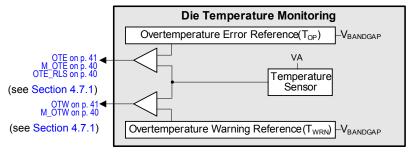

| 4.7 Die Temperature Monitoring                                       | 7.22 LED Lighting Status                             | . 43 |

| 4.8 Signal Monitoring                                                | 7.23 LED Flash Mode Current                          |      |

| 4.9 LED Driver                                                       |                                                      | . 44 |

| 4.10 Power Budgeting                                                 |                                                      |      |

| 4.11 Audio/Data Serial Port (ADSP)                                   | 7.26 LED Flash Inhibit Current                       |      |

| 4.12 Signaling Format                                                |                                                      | . 45 |

| 4.13 Device Clocking                                                 |                                                      | . 45 |

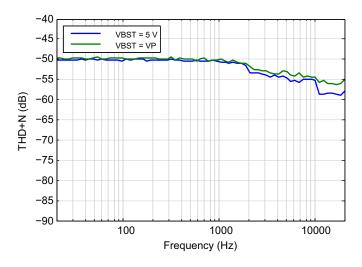

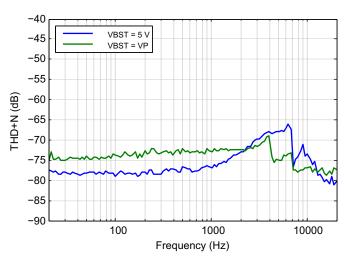

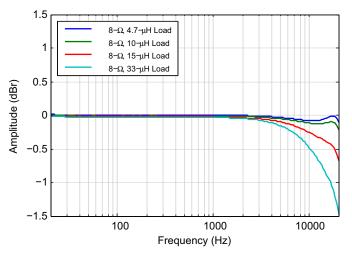

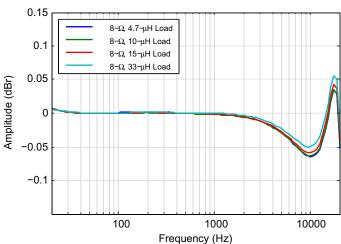

| 4.14 Control Port Operation                                          | 8.2 Audio Output Typical Performance Plots           | . 46 |

| 5 Applications                                                       |                                                      | . 47 |

| 5.1 Required Reserved Register Configuration                         |                                                      |      |

| 5.2 Avoiding Current Transients when Issuing a Flash Event 32        | 10 Package Dimensions                                | . 50 |

| 5.3 External Component and PCB Design Considerations—EMI C           | ut-11 Thermal Characteristics                        | . 50 |

| put Filtering                                                        | 12 Ordering Information                              | . 50 |

| 5.4 PCB Routing Considerations for Thermal Relief33                  | 13 References                                        |      |

| 5.5 Inductor Selection                                               | 14 Revision History                                  | . 51 |

|                                                                      |                                                      |      |

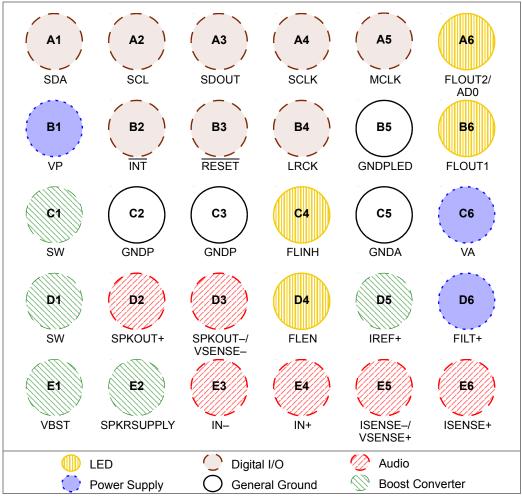

## 1 Pin Descriptions

Figure 1-1. Top-Down (Through-Package) View—30-Ball WLCSP Package

Table 1-1. Pin Descriptions

| Ball Name | Ball<br>Number | Power Supply | I/O | Ball Description                                                                                                                                                                              | Internal<br>Connection        | Driver                       | Receiver                       | State at<br>Reset |

|-----------|----------------|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------|--------------------------------|-------------------|

|           |                |              |     | Digital I/O                                                                                                                                                                                   |                               |                              |                                |                   |

| SDA       | A1             | VA           | I/O | <b>I<sup>2</sup>C Serial Data Input.</b> Serial data for the I <sup>2</sup> C serial port                                                                                                     | _                             | CMOS<br>open-drain<br>output | Hysteresis<br>on CMOS<br>input | Hi-Z              |

| SCL       | A2             | VA           | I   | I <sup>2</sup> C Clock Input. Serial clock for the I <sup>2</sup> C serial port                                                                                                               | _                             | _                            | Hysteresis<br>on CMOS<br>input | Hi-Z              |

| MCLK      | A5             | VA           | I   | Master Clock Source. Clock source for A/D converters and audio/data serial port (ADSP). MCLK <sub>INT</sub> , derived from MCLK, is used for other blocks (see Section 4.13 and Section 7.7). | Weak pull-<br>down<br>(~1 MΩ) | _                            | Hysteresis<br>on CMOS<br>input | Pulled<br>down    |

| SCLK      | A4             | VA           | I/O | <b>Serial Clock.</b> Serial shift clock for the serial audio interface                                                                                                                        | Weak pull-<br>down<br>(~1 MΩ) | CMOS<br>output               | Hysteresis<br>on CMOS<br>input | Pulled<br>down    |

| LRCK      | B4             | VA           | I/O | <b>Left Right Clock.</b> Determines which channel, left or right, is currently active on the serial audio/data lines                                                                          | Weak pull-<br>down<br>(~1 MΩ) | CMOS<br>output               | Hysteresis<br>on CMOS<br>input | Pulled<br>down    |

| SDOUT     | А3             | VA           | 0   | Serial Audio/Data Output. I2S serial data output used to monitor voltage and current of SPKOUT signal and VP levels                                                                           | Weak<br>pull-down<br>(~1 MΩ)  | CMOS<br>output               | <del></del>                    | Pulled<br>down    |

| ĪNT       | B2             | VA           | 0   | Interrupt. Programmable, open-drain, active-<br>low programmable interrupt output                                                                                                             | _                             | CMOS<br>open-drain<br>output | <del></del>                    | Hi-Z              |

|                            |                |                |     | Table 1-1. Pin Descriptions (Cont.)                                                                                                                                                                                                                 |                               |        |                                |                   |

|----------------------------|----------------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------|--------------------------------|-------------------|

| Ball Name                  | Ball<br>Number | Power Supply   | I/O | Ball Description                                                                                                                                                                                                                                    | Internal<br>Connection        | Driver | Receiver                       | State at<br>Reset |

| RESET                      | В3             | VA             | I   | <b>Reset.</b> When asserted, the device enters a low-power mode, outputs are set to Hi-Z, and I <sup>2</sup> C register values are set to defaults. Outputs are Hi-Z except those with weak pull-ups or pull-downs as mentioned.                    | _                             | _      | Hysteresis<br>on CMOS<br>input | Low               |

|                            |                |                |     | LED (                                                                                                                                                                                                                                               |                               |        |                                |                   |

| FLEN                       | D4             | VA             | I   | <b>Flash Enable.</b> Input signal commanding a flash event into both LEDs. It is asserted high.                                                                                                                                                     | Weak pull-<br>down<br>(~1 MΩ) | _      | Hysteresis<br>on CMOS<br>input |                   |

| FLINH                      | C4             | VA             | I   | Flash Inhibit. Input signal determining whether the LEDs are in Flash Mode (logic low) or Flash-Inhibit Mode (logic high, LED current reduced).                                                                                                     | Weak pull-<br>down<br>(~1 MΩ) | _      | Hysteresis<br>on CMOS<br>input | Pulled<br>down    |

| FLOUT1                     | В6             | SPKR<br>SUPPLY |     | <b>LED Driver 1.</b> Output driving LED 1 by sinking current from the LED cathode                                                                                                                                                                   | Weak pull-up (~1 MΩ)          | _      |                                | SPKR<br>SUPPLY    |

| FLOUT2/AD0                 | A6             | SPKR<br>SUPPLY | I/O | LED Driver 2/Address Zero. Output driving LED 2 by sinking current from the LED cathode. AD0 programs the chip address when RESET is deasserted. If no LED is used, tying the pin to ground clears the chip address LSB. Otherwise, the LSB is set. | Weak pull-up<br>(~1 MΩ)       | _      | _                              | SPKR<br>SUPPLY    |

|                            |                |                |     | Boost Converter                                                                                                                                                                                                                                     |                               |        |                                |                   |

| VBST                       | E1             | _              | 0   | <b>Boost Converter Output.</b> Output of boosted supply. This pin cannot be used to drive any external loads other than the on chip Class D Amplifier and Flash LEDs.                                                                               | _                             | _      | _                              | _                 |

| SPKRSUPPLY                 | E2             | _              | I   | <b>Speaker Supply.</b> Full-bridge Class D speaker amplifier power supply.                                                                                                                                                                          | _                             |        |                                | _                 |

| SW                         | C1, D1         | VBST           | I   | <b>Boost Converter Switch Node.</b> Connects the inductor to the rectifying switch.                                                                                                                                                                 | _                             | _      | _                              | _                 |

| IREF+                      | D5             | VA             | I   | Current Reference Resistor. Connection for an external resistor to be used for generating the CS35L32's internal main current reference. See Fig. 2-1 for required resistor value.                                                                  | _                             | _      | _                              | _                 |

|                            |                |                |     | Audio 🏀                                                                                                                                                                                                                                             |                               |        |                                |                   |

| IN+                        | E4             | SPKR<br>SUPPLY | I   | Input 1 Differential Positive Line. Positive analog input                                                                                                                                                                                           | _                             | _      | _                              | _                 |

| IN-                        | E3             | SPKR<br>SUPPLY | I   | <b>Input 1 Differential Negative Line.</b> Negative analog input                                                                                                                                                                                    | _                             | _      | _                              | _                 |

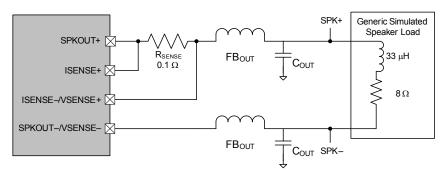

| SPKOUT+<br>SPKOUT-/VSENSE- | D2<br>D3       | SPKR<br>SUPPLY | 0   | Speaker Differential Audio Output. Internal Class D speaker amplifier output. SPKOUT–serves as voltage monitor negative sense pin (VSENSE–).                                                                                                        | _                             | _      | _                              | Hi-Z              |

| ISENSE+<br>ISENSE-/VSENSE+ | E6<br>E5       | SPKR<br>SUPPLY | I   | Current Sense Inputs. Sense voltage across an external resistor in series with SPKOUT+. ISENSE– serves as voltage monitor positive sense pin (VSENSE+).                                                                                             | _                             | _      | _                              | _                 |

|                            |                |                |     | Power Supply 🛑                                                                                                                                                                                                                                      |                               |        |                                |                   |

| FILT+                      | D6             | VA             | 0   | Positive Voltage Reference. Positive reference for internal circuits                                                                                                                                                                                | _                             | _      | _                              | _                 |

| VA                         | C6             | _              | I   | Analog Input Power. Power supply for internal analog section                                                                                                                                                                                        | _                             | _      | _                              | _                 |

| VP                         | B1             | _              | I   | <b>Boost Converter Input Power.</b> Power supply or battery voltage powering boost converter                                                                                                                                                        | _                             | _      | _                              |                   |

|                            |                |                |     | General Ground                                                                                                                                                                                                                                      |                               |        |                                |                   |

| GNDA                       | C5             |                |     | <b>Analog Ground.</b> Ground reference for the internal analog section of the IC                                                                                                                                                                    |                               | _      |                                |                   |

| GNDP                       | C2, C3         |                |     | <b>Power Ground.</b> Ground reference for boost converter and Class D amplifier's output stage                                                                                                                                                      |                               |        |                                |                   |

| GNDPLED                    | B5             | _              |     | <b>LED Power Ground.</b> Ground reference for LED current return. Should be tied to ground plane.                                                                                                                                                   | _                             | _      |                                | _                 |

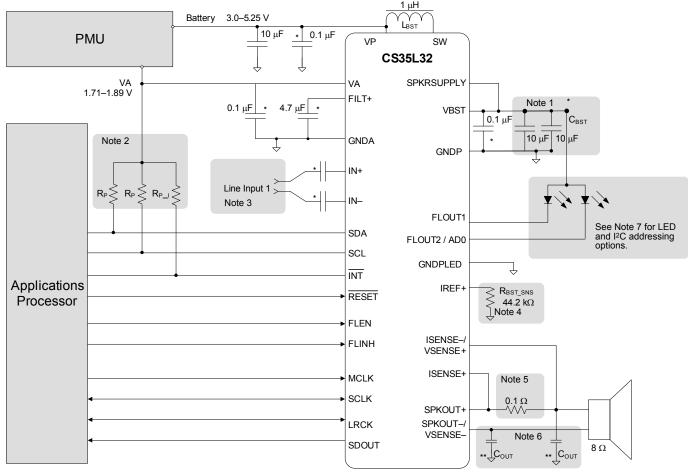

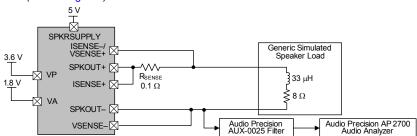

### 2 Typical Connection Diagram

#### Notes:

- All external passive component values are nominal values.

- Key for capacitor types required:

- \* Úse low ESR, X7R/X5R capacitors.

- \*\* Use low ESR. X7R capacitors.

- If no type symbol is shown next to a capacitor, any type may be used.

- As required, add protection circuitry to ensure compliance with the absolute maximum ratings in Table 3-2.

- C<sub>BST</sub> is a ceramic capacitor and derates at DC voltages higher than 0 V. In this application, the capacitor should not derate to a value lower than 4 μF across the specified boost output voltage in Table 3-4. Capacitor tolerance and the temperature coefficient should also be taken into account to guarantee the 4-μF value.

- 2. Minimum pull-up resistor values are selected in accordance with the Table 3-8 V<sub>OL</sub> specification. Maximum pull-up resistances are selected based on load capacitance and relevant switching specs (Table 3-13).

- Select each capacitor to be 0.22 μF for an 18-Hz passband @ 12-dB amplifier gain, for a 3-dB roll-off. The equation for calculating the capacitance for a given passband is C = 1/(π \* f \* R<sub>INDIF</sub>), where C is in F, R<sub>INDIF</sub> is the differential input resistance in Ω, and f is in Hz (see the differential input resistance specification in Table 3-3). Signals IN+ and IN- are subject to the recommended ranges in Table 3-1.

R<sub>BST SNS</sub> is inherently tied to the accuracy of the BST\_IPK current limit. A resistor with a 0.1% tolerance is required for this component to

- R<sub>BST\_SNS</sub> is inherently tied to the accuracy of the BST\_IPK current limit. A resistor with a 0.1% tolerance is required for this component to meet the specified IMAX(B) max and min values in Table 3-4.

- 5. The required tolerance on the 0.1- $\Omega$  ISENSE resistor is 1%. The required temperature coefficient is  $\pm 200$  ppm/°C.

- C<sub>OUT</sub> capacitors are optional EMI suppressors used with CS35L32 edge-rate control, depending on application requirements. Because switching losses increase linearly with increases to these capacitances, it is recommended that C<sub>OUT</sub> values not exceed 2 nF. The recommended value is 470 pF.

- 7. LED and I2C addressing options:

Figure 2-1. Typical Connection Diagram

### 3 Characteristics and Specifications

#### **Table 3-1. Recommended Operating Conditions**

GNDA = GNDP = 0 V, all voltages with respect to ground. Device functional operation is guaranteed within these limits. Functionality is not guaranteed or implied outside of these limits. Operation outside of these limits may adversely affect device reliability.

|                                                          | Parameters                                              | Test Conditions | Symbol            | Min  | Max              | Units |

|----------------------------------------------------------|---------------------------------------------------------|-----------------|-------------------|------|------------------|-------|

| DC power supply                                          | Analog (and digital I/O and core)                       | _               | VA                | 1.71 | 1.89             | V     |

|                                                          | Battery                                                 | _               | VP                | 3.0  | 5.25             | V     |

| 9                                                        | alog inputs powered by VA (IREF+, FILT+) 1              | _               | V <sub>INAS</sub> | -0.3 | VA + 0.3         | V     |

| External voltage applied to an IN-, ISENSE+, ISENSE-,VSE | alog inputs powered by SPKRSUPPLY (IN+, ENSE+, VSENSE-) | _               | V <sub>INSS</sub> | -0.3 | SPKRSUPPLY + 0.3 | V     |

| External voltage applied to dig                          | gital inputs                                            | _               | V <sub>INDI</sub> | -0.3 | VA + 0.3         | V     |

| Ambient temperature                                      |                                                         | _               | TA                | -10  | +70              | °C    |

<sup>1.</sup> The maximum overvoltage/undervoltage is limited by the input current.

#### **Table 3-2. Absolute Maximum Ratings**

GNDA = GNDP = 0 V; all voltages with respect to ground. Operation at or beyond these limits may permanently damage the device.

| Parameters                                                     |         | Test Conditions | Symbol           | Min  | Max  | Units |

|----------------------------------------------------------------|---------|-----------------|------------------|------|------|-------|

| DC power supply                                                | Analog  | _               | VA               | -0.3 | 2.22 | V     |

|                                                                | Battery | _               | VP               | -0.3 | 6.0  | V     |

| Input current 1                                                |         | _               | I <sub>IN</sub>  | _    | ±10  | mA    |

| Ambient operating temperature (local to device, power applied) |         | _               | T <sub>A</sub>   | -40  | +115 | °C    |

| Junction operating temperature (power applied)                 |         | _               | TJ               | -40  | +150 | °C    |

| Storage temperature                                            |         | _               | T <sub>STG</sub> | -65  | +150 | °C    |

<sup>1.</sup>Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins do not cause SCR latch up.

#### **Table 3-3. DC Characteristics**

Test conditions, except where noted otherwise: VA = 1.8 V, VP = 3.6 V, VBST = 5.0 V, GNDA = GNDP = 0 V, TA = +25°C.

| Parameters                                     | Symbol             | Test Conditions        | Min | Typical | Max      | Units |

|------------------------------------------------|--------------------|------------------------|-----|---------|----------|-------|

| Differential Input resistance (IN+ to IN-)     | R <sub>INDIF</sub> | Amp gain = 9 dB        | _   | 63      | _        | kΩ    |

|                                                |                    | Amp gain = 12 dB       |     | 51      | _        | kΩ    |

|                                                |                    | Amp gain = 15 dB       |     | 40      | <u> </u> | kΩ    |

|                                                |                    | Amp gain = 18 dB       | _   | 31      | _        | kΩ    |

| FILT+ voltage                                  | _                  | _                      | _   | VA      | _        | _     |

| Overtemperature shutdown threshold             | T <sub>OP</sub>    | _                      | _   | 150     | _        | °C    |

| Overtemperature warning threshold              | T <sub>WRN</sub>   | _                      | _   | 135     | _        | °C    |

| Overtemperature warning threshold deviation    | _                  | _                      | _   | ±10     | _        | °C    |

| Low battery threshold                          | _                  | LOWBAT_TH = 00         | _   | 3.10    | _        | V     |

|                                                |                    | $LOWBAT_TH = 01$       |     | 3.20    | <u> </u> | V     |

|                                                |                    | LOWBAT_TH = 10         |     | 3.30    | _        | V     |

|                                                |                    | $LOWBAT_TH = 11$       | _   | 3.40    | _        | V     |

| Low-battery recovery threshold                 | _                  | LOWBAT_RECOV = 001     |     | 3.20    | _        | V     |

|                                                |                    | LOWBAT_RECOV = 010     |     | 3.30    | _        | V     |

|                                                |                    | LOWBAT_RECOV = 011     | _   | 3.40    | _        | V     |

|                                                |                    | LOWBAT_RECOV = 100     |     | 3.50    | _        | V     |

|                                                |                    | LOWBAT_RECOV = 101–11x | _   | 3.60    | _        | V     |

| VP undervoltage lockout threshold (VP falling) | UVLO               | <del>-</del>           |     | 2       | _        | V     |

| VP undervoltage lockout hysteresis             | _                  | <del>-</del>           |     | 100     | _        | mV    |

#### **Table 3-4. Boost Converter Characteristics**

Test conditions, except where noted otherwise: VA = 1.8 V, VP = 3.6 V, VBST = 5.0 V, amp gain = 12 dB, GNDA = GNDP = 0 V,  $TA = +25^{\circ}C$ ,  $MCLK_{INT} = 6 \text{ MHz}$ .  $MCLK_{INT}$  is explained in Section 4.13.1 and Section 7.7.

| Parameters                                    | Symbol               | Test Conditions                                          | Min        | Typical                | Max | Units |

|-----------------------------------------------|----------------------|----------------------------------------------------------|------------|------------------------|-----|-------|

| Boost output voltage                          | VBST                 | Boosting                                                 | VP*1.15    | _                      | 5.4 | V     |

| · -                                           |                      | Bypass                                                   | _          | VP                     | _   | V     |

| Boost output voltage tolerance                | ΔVBST                | No load: I <sub>LOAD</sub> =0 mA                         | <b>-</b> 5 | _                      | +5  | %     |

| Load regulation                               | $\Delta V_{(Load)}$  | 3.0 V < VP < 4.2 V; I <sub>LOAD</sub> = 0.25A to 1.5 A   | _          | 60                     | _   | mV/A  |

| Line regulation                               | $\Delta V_{(Line)}$  | 3.0 V <vp<4.2 i<sub="" v;="">LOAD = 0 A, 500 mA</vp<4.2> | _          | 40                     | _   | mV/V  |

| Boost FET peak-current limit                  | I <sub>MAX(B)</sub>  | BST_IPK = 0000 0000                                      |            | 2.89                   | _   | A     |

| (See Section 7.10.)                           |                      | BST_IPK = 0010 0000                                      |            | 3.30                   | _   | Α     |

|                                               |                      | BST_IPK = 0100 0000                                      |            | 3.72                   | _   | Α     |

|                                               |                      | BST_IPK = 0110 0000                                      |            | 4.14                   | _   | A     |

|                                               |                      | BST_IPK = 1000 0000                                      |            | 4.56                   | _   | Α     |

| Output switching frequency 1                  | f <sub>SW(B)</sub>   |                                                          | _          | MCLK <sub>INT</sub> /3 | _   | MHz   |

| Boost FET ON resistance                       | R <sub>DS(ON)B</sub> | $I_{OUT(B)} = 1 A$                                       | _          | 80                     | _   | mΩ    |

| Boost FET ON resistance temp coefficient      |                      | I <sub>OUT(B)</sub> = 1 A                                | _          | 0.2                    | _   | %/°C  |

| Rectifying FET ON resistance                  | R <sub>DS(ON)R</sub> | I <sub>OUT(B)</sub> = 1 A                                | _          | 150                    | _   | mΩ    |

| Rectifying FET ON resistance temp coefficient |                      | $I_{OUT(B)} = 1 A$                                       | _          | 0.2                    | _   | %/°C  |

| Overvoltage detection threshold               | V <sub>OVTH</sub>    | Boost enabled                                            | _          | 5.5                    | 5.7 | V     |

| Threshold Class G On, IN+ to IN-              | V <sub>IN1THON</sub> | VBST = VP = 3.6 V                                        | _          | 0.60                   | _   | V     |

| Threshold Class G Off, IN+ to IN-             | V <sub>IN1THOF</sub> |                                                          | _          | 0.33                   | _   | V     |

| Minimum Class G boost ON hold-off time        | _                    | VP = 3.6 V, VBST = 5 V                                   | _          | 8002                   | _   | ms    |

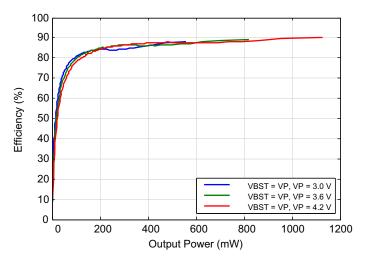

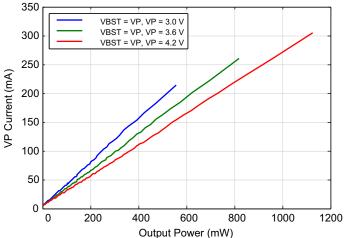

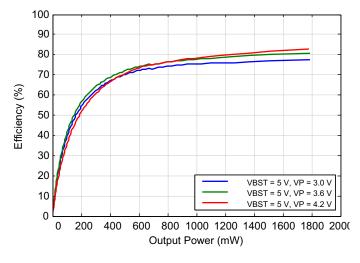

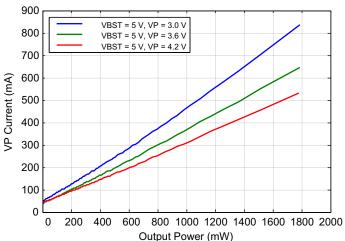

| Operating efficiency <sup>3</sup>             | $\eta_{B}$           | VBST = 5 V, I <sub>OUT(B)</sub> = 500 mA                 | _          | 90                     | _   | %     |

|                                               |                      | VBST = 5 V, $I_{OUT(B)} = 1.5 A$                         | _          | 85                     | _   | %     |

- 1.MCLKDIV2 (see p. 37) should be configured so MCLK<sub>INT</sub> is 6 or 6.1440 MHz (see Table 4-14) for boost-converter operation at 2 or 2.05 MHz.

- 2.Minimum Class G boost ON hold-off time is determined from when the low audio detection is latched until when the boost is turned off. The latching mechanism occurs in 800-ms intervals. If the audio level is detected as low between two sequential latches, the hold-off time is extended by the difference between when the detection occurs and the subsequent latch pulse. This may extend the hold-off time up to 1.6 s in extreme cases.

- 3. Efficiency specified here assumes the boost converter drives an external resistive load via the VBST pin, instead of the onboard Class D amplifier.

#### **Table 3-5. LED Drive Characteristics**

Test conditions, except where noted otherwise: VA = 1.8 V, VP = 3.6 V, VBST = 5.0 V, GNDA = GNDP = GNDPLED = 0 V, TA = +25°C.

| Parame                                               | eters                                                            | Min     | Typical      | Max     | Units    |

|------------------------------------------------------|------------------------------------------------------------------|---------|--------------|---------|----------|

| Flash Mode current settings, per LED <sup>1</sup>    | LED_FLCUR = 1111                                                 |         | 750          | _       | mA       |

| (Step size = 50 mA)                                  | LED_FLCUR = 0001                                                 | <u></u> | 50           | <u></u> | mA       |

| Flash Inhibit Mode current settings, per LED 1       | LED_FLINHCUR = 0111                                              |         | 350          | _       | mA       |

| (Step size = 50 mA)                                  | LED_FLINHCUR = 0001                                              | <u></u> | 50           | <u></u> | mA       |

| Movie Mode current settings, per LED <sup>1</sup>    | LED_MVCUR = 111                                                  |         | 150          | _       | mA       |

|                                                      | LED_MVCUR = 110                                                  |         | 120          | _       | mA       |

|                                                      | LED_MVCUR = 101<br>LED_MVCUR = 100                               | _       | 100          | _       | mA<br>m^ |

|                                                      | LED_MVCUR = 1001<br>LED_MVCUR = 011                              | _       | 80<br>60     | _       | mA<br>mA |

|                                                      | LED_MVCUR = 010                                                  |         | 40           |         | mA       |

|                                                      | LED_MVCUR = 001                                                  | _       | 20           | _       | mA       |

| LED current accuracy                                 |                                                                  | -10     | _            | +10     | %        |

| LED current matching                                 |                                                                  | _       | 10           | _       | %        |

| Flash timer (t <sub>flash</sub> )                    | MCLK <sub>INT</sub> = 6 MHz <sup>2</sup> ; TIMER = 1 0010–1 1111 | _       | 500          | _       | ms       |

|                                                      | TIMER = 0 0001                                                   | _       | 75           | _       | ms       |

|                                                      | TIMER = 0 0000                                                   | _       | 50           | _       | ms       |

|                                                      | MCLK <sub>INT</sub> = 6.144 MHz; TIMER = 1 0010–1 11111          | _       | 488.3        | _       | ms       |

|                                                      | TIMER = 0 0001<br>TIMER = 0 0000                                 | _       | 73.2<br>48.8 | _       | ms       |

|                                                      | HIMER = 0 0000                                                   |         | 40.8         |         | ms       |

| LED flash timer accuracy                             |                                                                  | 0       |              | +1      | ms       |

| LED flash inhibit time (FLINH high to LED current 3% | % settling)                                                      | _       | 40           | _       | μS       |

<sup>1.</sup> Flash or Movie Mode current is delivered from the boost converter's output, which provides a voltage higher than the LED voltage. Depending on the LED voltage requirement and on VP supply voltage, the boost converter is internally controlled to boost or be in bypass (rectifying FET fully on).

<sup>2.</sup> The flash time setting is generated from MCLK<sub>INT</sub>. MCLKDIV2 (see p. 37) should be configured so MCLK<sub>INT</sub> is 6 or 6.1440 MHz. See Table 4-14.

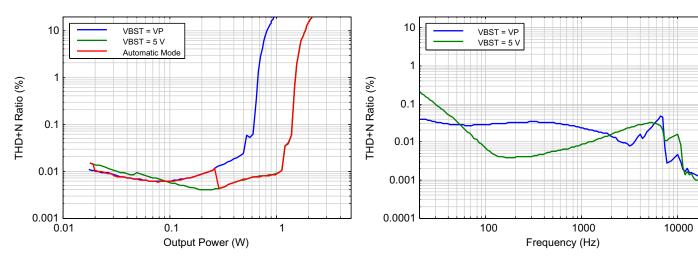

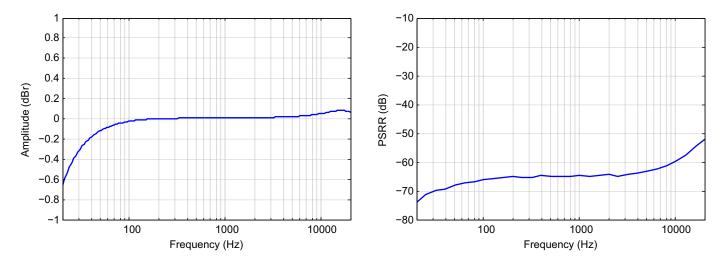

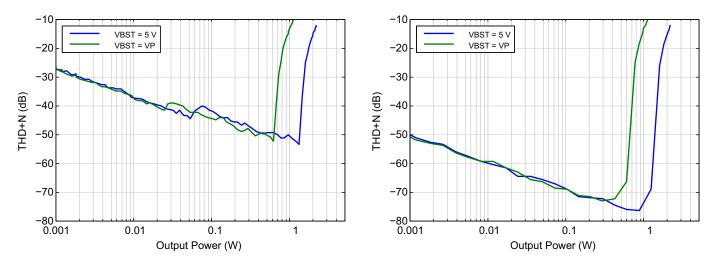

#### **Table 3-6. Speaker Amplifier Output Characteristics**

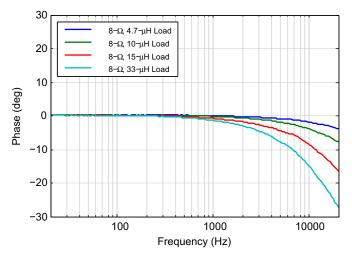

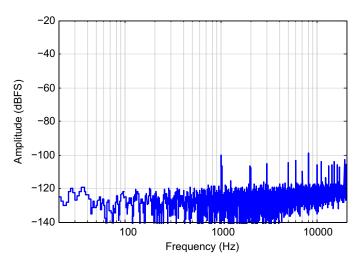

Test conditions, except where noted otherwise: VA = 1.8 V, VP = 3.6 V, VBST = 5.0 V, 1-kHz input, amp gain = 12 dB, GNDA = GNDP = 0 V, T<sub>A</sub> = +25°C, measurement bandwidth is 20 Hz to 20 kHz, Fs = 48 kHz, MCLK<sub>INT</sub> = 6 MHz. MCLK<sub>INT</sub> is explained in Section 4.13.1 and Section 7.7.

| Parameters                                   | Symbol               | Test Conditions                                                        | Min  | Typical | Max | Units |

|----------------------------------------------|----------------------|------------------------------------------------------------------------|------|---------|-----|-------|

| Continuous average power delivered to load 1 | Po                   | 8-Ω load, THD 10%                                                      | _    | 1.75    | _   | W     |

|                                              |                      | 8-Ω load, THD 1%                                                       | _    | 1.45    | _   | W     |

| THD+N                                        | THD+N                | 8-Ω load, 1.0 W                                                        | _    | 0.02    | _   | %     |

| Input voltage @ 1% THD+N                     | V <sub>ICLIP</sub>   | 8-Ω load                                                               | _    | 0.84    | _   | Vrms  |

| Signal to noise ratio                        | SNR                  | Referenced to output voltage @1% THD+N, A-weighted                     | _    | 102     | _   | dB    |

| Idle channel noise                           | ICN                  | VBST = VP, A-weighted                                                  | _    | 25      | _   | μVrms |

| Common-mode rejection ratio                  | CMRR                 | V <sub>ripple</sub> = 1 V <sub>PP</sub> , f <sub>ripple</sub> = 217 Hz | _    | 55      | _   | dB    |

| Frequency response                           | FR                   | 20 Hz to 20 kHz, No input DC blocking caps                             | -0.1 | 0       | 0.1 | dB    |

| Efficiency <sup>2</sup>                      | ηΑ                   | 8-Ω load 33 μH, 1.7 W                                                  | _    | 91      | _   | %     |

| Class D amplifier gain                       | _                    | AMP_GAIN = 000 (mute)                                                  |      | -80     | _   | dB    |

|                                              |                      | AMP_GAIN = 001                                                         | _    | 9       | _   | dB    |

|                                              |                      | $AMP\_GAIN = 010$                                                      |      | 12      | _   | dB    |

|                                              |                      | $AMP\_GAIN = 011$                                                      | _    | 15      | _   | dB    |

|                                              |                      | AMP_GAIN = 100                                                         | _    | 18      | _   | dB    |

| N-FET ON resistance                          | R <sub>DS ON,N</sub> | I <sub>FET</sub> = 0.5 A                                               | _    | 185     | _   | mΩ    |

|                                              | R <sub>DS ON,P</sub> |                                                                        | _    | 205     | _   | mΩ    |

| Output DC offset voltage                     | V <sub>OFFSET</sub>  | Inputs AC coupled to ground                                            |      | ±5      | _   | mV    |

| Time from shutdown to audio out              | t <sub>SD</sub>      | RESET deasserted, zero-crossing disabled                               | _    | 15      | _   | ms    |

1. Power delivered to the speaker from the 0.1- $\Omega$  load side terminal (refer to Fig. 2-1).

Efficiency collected using a 5-V external supply, as shown in the drawing. For this test, the VBST pin should not be connected to the SPKRSUPPLY pin.

#### **Table 3-7. Signal Monitoring Characteristics**

Test conditions, except where noted otherwise: VA = 1.8 V, VP = 3.6 V, VBST = 5.0 V, amp gain = 12 dB,  $0.1-\Omega$  sense resistor, GNDA = GNDP = 0 V,  $T_A = +25^{\circ}C$ . Measurement bandwidth is 20 Hz to 20 kHz, Fs = 48 kHz, Input Signal = 1 kHz,  $MCLK_{INT} = 6 \text{ MHz}$ ,  $MCLK_$

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Parameters                                                                     | Min                                                                                                                  | Typical         | Max                                         | Units           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------|-----------------|

| General ADC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power-up time: t <sub>PUP(ADC)</sub>                                           | _                                                                                                                    | 8.5             | [1]                                         | ms              |

| VSENSE± monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Data width                                                                     | _                                                                                                                    | 16              | _                                           | Bits            |

| characteristics (VMON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Dynamic range (unweighted), VSENSE± = ±5.0 V (10 V <sub>PP</sub> )             | _                                                                                                                    | 60              | _                                           | dB <sup>2</sup> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Total harmonic distortion + noise, –3.8 dBFS <sup>3</sup>                      | _                                                                                                                    | -60             | 8.5 [1] 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | dB <sup>2</sup> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Full-scale signal input voltage                                                | 6.59•VA                                                                                                              | 6.94•VA         | 7.29•VA                                     | $V_{PP}$        |

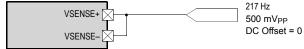

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Common-mode rejection ratio (217 Hz @ 500 mV <sub>PP</sub> ) <sup>4</sup>      | _                                                                                                                    | 60              | _                                           | dB <sup>2</sup> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Group delay 5                                                                  | _                                                                                                                    | 7.6/Fs          | _                                           | S               |

| ISENSE± monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Data width                                                                     | _                                                                                                                    | 16              | _                                           | Bits            |

| characteristics (IMON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Dynamic range (unweighted), ISENSE $\pm = \pm 0.625$ A (1.25 A <sub>PP</sub> ) | Power-up time: t <sub>PUP(ADC)</sub>                                                                                 | _               | dB <sup>2</sup>                             |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Total harmonic distortion, –29.5 dBFS 6                                        | _                                                                                                                    | -45             | — — — — — — — — — — — — — — — — — — —       | dB <sup>2</sup> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Full-scale signal input voltage                                                | monic distortion, -29.5 dBFS 6 — -45 — dB<br>Full-scale signal input voltage 1.56•VA 1.64•VA 1.72•VA V <sub>PI</sub> | $V_{PP}$        |                                             |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Full-scale signal input voltage   6.59*VA   6.94*VA   7.29*V                   | _                                                                                                                    | dB <sup>2</sup> |                                             |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Group delay 8                                                                  | _                                                                                                                    | 7.6/Fs          | _                                           | S               |

| VP monitoring characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Data width                                                                     | _                                                                                                                    | 8               | _                                           | Bits            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Voltage resolution (See the equation in Section 4.8.4.)                        | _                                                                                                                    | 35.3            | _                                           | mV              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (FF code) signal input voltage (VP)                                            | 2.89•VA                                                                                                              | 3.05•VA         | 3.20•VA                                     | V               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                |                                                                                                                      | _               | _                                           | V               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VPMON = 1011 0100                                                              | _                                                                                                                    | 2.835           | _                                           | V               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <br>VPMON = 1111 1111                                                          |                                                                                                                      |                 |                                             | <br>V           |

| characteristics (VMON)  Dynamic range (unweighted), VSENSE± = ±5.0 V (10 V Total harmonic distortion + noise, -3.8 dBF Full-scale signal input volt Common-mode rejection ratio (217 Hz @ 500 mVp Group delayer and the provided signal input volt Dynamic range (unweighted), ISENSE± = ±0.625 A (1.25 A Total harmonic distortion, -29.5 dBF Full-scale signal input volt VMON-to-IMON isolation Group delayer and VP monitoring characteristics  VP monitoring characteristics  Voltage resolution (See the equation in Section 4.8 (FF code) signal input voltage (VPMON = 1011 0 VPMON = 1011 0 VPMON = 1111 1 |                                                                                |                                                                                                                      | _               | V                                           |                 |

- 1. Typical value is specified with PDN\_AMP and PDN\_xMON bits initially set. Maximum power-up time is affected by the actual MCLK<sub>INT</sub> frequency.

- 2. Parameters given in dB are referred to the applicable typical full-scale voltages. Applies to all THD+N and resolution values in the table

- $3.VSENSE\pm$  THD is measured with the Class D amplifier as the audio source connected to an  $8-\Omega + 33\mu H$  speaker load, supplied by a  $6.3-V_{PP}$ , 1-kHz sine wave, operating under the typical performance test conditions to produce a large, unclipped audio signal. This setup produces a -3.8-dBFS VMON output. Larger Class D amplifier amplitudes begin to exhibit clipping behavior, increasing distortion of the signal supplied to VSENSE±

4. CMRR test setup for VSENSE±:

- 5.VMON group delay is measured from the time a signal is presented on the VSENSE± and pins until the MSB of the digitized signal exits the serial port. Fs is the LRCK rate.

- 6.For reference, injecting a 125-mVpp fully differential sine wave into the ISENSE± pins (equivalent to a ±0.625 A current with a 0.1-Ω ISENSE resistor) produces an IMON output of –29.5 dBFS (since typical full-scale is 1.64\*VA, in V<sub>PP</sub>). ISENSE± monitoring THD is measured using the Class D amplifier as the audio source, which is connected to an 8-Ω + 33-μH speaker load, supplied by a 7.0-V<sub>PP</sub>, 1-kHz sine wave, operating under the typical performance test conditions to produce a large, unclipped audio signal. This setup produces a –29.5-dBFS amplitude IMON output. Larger Class D amplifier amplitudes begin to exhibit clipping behavior, increasing the distortion of the signal supplied to ISENSE±.

- 7.VMON-to-IMON isolation is the error in the current sense due to VMON, expressed relative to full-scale sense current in decibels.

- 8.IMON group delay is measured from when a signal is presented on the ISENSE± pins until the MSB of the digitized signal exits the serial port. Fs is the LRCK rate.

#### **Table 3-8. Digital Interface Specifications and Characteristics**

Test conditions, except where noted otherwise: VA = 1.8 V, VP = 3.6 V, VBST = 5.0 V, GNDA = GNDP = 0 V, TA = +25°C.

| Parameter                           | s                         | Symbol          | Test Conditions                                       | Min     | Max     | Units |

|-------------------------------------|---------------------------|-----------------|-------------------------------------------------------|---------|---------|-------|

| Input leakage current (per pin) 1,2 | FLOUT2/AD0                | I <sub>IN</sub> | _                                                     | _       | ±7.5    | μΑ    |

|                                     | FLEN, FLINH, LRCK         |                 | _                                                     | _       | ±4.5    | μΑ    |

|                                     | MCLK, SCLK, SDOUT         |                 | _                                                     | _       | ±4.5    | μΑ    |

|                                     | SCL, SDA, INT, RESET      |                 | _                                                     | _       | ±0.1    | μΑ    |

| Input capacitance                   |                           | I <sub>IN</sub> | _                                                     | _       | 10      | pF    |

| VA logic I/Os                       | High-level output voltage | V <sub>OH</sub> | I <sub>OH</sub> = -67/-100 μA <sup>3</sup>            | VA-0.2  | _       | V     |

|                                     | Low-level output voltage  | $V_{OL}$        | All outputs, I <sub>OL</sub> = 67/100 μA <sup>3</sup> | _       | 0.20    | V     |

|                                     |                           |                 | INT, SDA, I <sub>OL</sub> = 3 mA                      | _       | 0.4     | V     |

|                                     | High-level input voltage  | V <sub>IH</sub> | _                                                     | 0.70•VA | _       | V     |

|                                     | Low-level input voltage   | $V_{IL}$        | _                                                     | _       | 0.30•VA | V     |

- 1. Specification includes current through internal pull up/down resistors, where applicable (as defined in Section 1).

- 2. Leakage current is measured with VA = 1.80 V, VP = 3.60 V, VBST = 3.60 V, and RESET asserted. Each pin is tested while driven high and low.

- 3. For the ADSP output SDOUT and potential outputs SCLK and LRCK (if M/S = 1), if ADSP\_DRIVE = 0 see Section 7.13,  $I_{OH}$  and  $I_{OL}$  are -100 and +100  $\mu$ A. If ADSP\_DRIVE = 1,  $I_{OH}$  and  $I_{OL}$  are -67 and +67  $\mu$ A. For other, non-ADSP\_DRIVE-affected outputs,  $I_{OH}$  and  $I_{OL}$  are -100 and +100  $\mu$ A.

#### Table 3-9. PSRR Characteristics

Test conditions, except where noted otherwise: VA = 1.8 V, VP = 3.6 V, VBST = VP, amp gain = 12 dB, GNDA = GNDP = 0 V, T<sub>A</sub> = +25°C.

| Parameters        | Conditions | Noise<br>Injected Into |         | Noise<br>Amplitude (mV) | Noise<br>Frequency (Hz) | Min | Typical | Max | Units |

|-------------------|------------|------------------------|---------|-------------------------|-------------------------|-----|---------|-----|-------|

| Speaker amplifier | VBST = VP  | VA                     | SPKOUT± | 100                     | 217                     | _   | 75      | _   | dB    |

| PSRR              |            |                        |         |                         | 1k                      | _   | 75      | _   | dB    |

|                   |            |                        |         |                         | 20k                     | _   | 70      | _   | dB    |

|                   |            | VP                     | SPKOUT± | 100                     | 217                     | _   | 70      | _   | dB    |

|                   |            |                        |         |                         | 1k                      | _   | 70      | _   | dB    |

|                   |            |                        |         |                         | 20k                     | _   | 55      | _   | dB    |

| VPMON PSRR        | VBST = VP  | VA                     | SDOUT   | 100                     | 217                     | _   | 36      | _   | dB    |

|                   |            |                        |         |                         | 1k                      | _   | 36      | _   | dB    |

|                   |            |                        |         |                         | 20k                     | _   | 33      | _   | dB    |

| VSENSE± PSRR 1    | VBST = VP  | VA                     | SDOUT   | 100                     | 217                     | _   | 60      | _   | dB    |

|                   |            |                        |         |                         | 1k                      | _   | 60      | _   | dB    |

|                   |            |                        |         |                         | 20k                     | _   | 50      | _   | dB    |

| ISENSE± PSRR      | VBST = VP  | VA                     | SDOUT   | 100                     | 217                     | _   | 60      | _   | dB    |

|                   |            |                        |         |                         | 1k                      | _   | 60      | _   | dB    |

|                   |            |                        |         |                         | 20k                     | _   | 60      | _   | dB    |

<sup>1.</sup> The speaker voltage monitor has a lower PSRR because its input path has an attenuation of 16.6 dB. The PSRR specification is referred to the input signal and, as such, includes the loss of 16.6 dB.

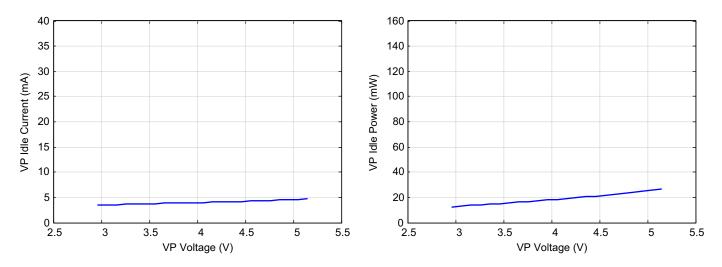

#### **Table 3-10. Power Consumption**

Test conditions, except where noted otherwise: VA = 1.8 V, VP = 3.6 V, VBST = VP, GNDA = GNDP = 0 V, T<sub>A</sub> = +25°C.

|                          | Use Configuration                                                                                                |      |      |       |

|--------------------------|------------------------------------------------------------------------------------------------------------------|------|------|-------|

|                          | Ose Configuration                                                                                                |      |      | Units |