# 17-V, 1.5-A, SYNCHRONOUS STEP-DOWN CONVERTER

Check for Samples: TPS62110-HT

#### **FEATURES**

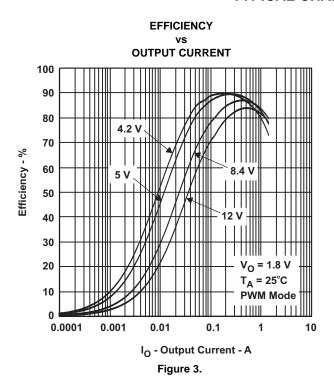

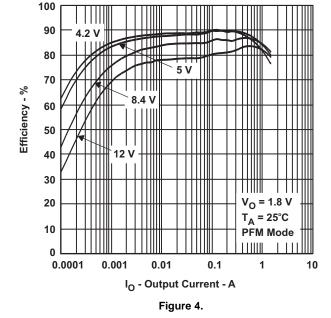

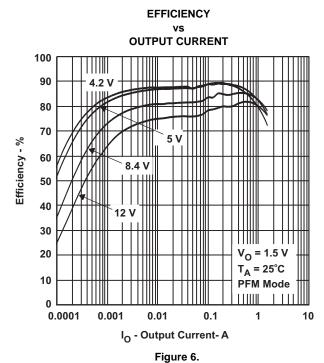

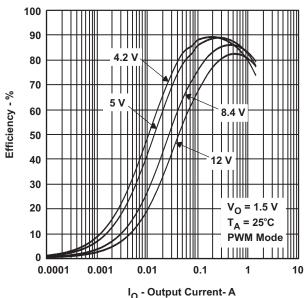

- High-Efficiency Synchronous Step-Down Converter With up to 95% Efficiency

- 3.1-V to 17-V Operating Input Voltage Range

- Adjustable Output Voltage Range From 1.2 V to 16 V

- Synchronizable to External Clock Signal up to 1.4 MHz

- Up to 1.5-A Output Peak Current (1)

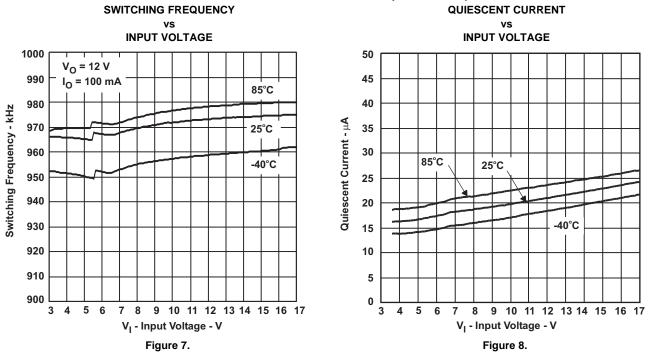

- 32-µA Quiescent Current (Typ)

- High Efficiency Over a Wide Load Current Range Due to PFM/PWM Operation Mode

- 100% Maximum Duty Cycle for Lowest Dropout

- Overtemperature and Overcurrent Protected

- Available in 16-Pin (PWP) QFP Package

## **APPLICATIONS**

- Down-Hole Drilling

- High Temperature Environments

- (1) Reduce life time may happen when 1.5-A limit is used for long time. Please refer to the EM calculations graph.

# SUPPORTS EXTREME TEMPERATURE APPLICATIONS

- Controlled Baseline

- One Assembly/Test Site

- One Fabrication Site

- Available in Extreme (–55°C/175°C)

Temperature Range<sup>(2)</sup>

- Extended Product Life Cycle

- · Extended Product-Change Notification

- Product Traceability

- Texas Instruments high temperature products utilize highly optimized silicon (die) solutions with design and process enhancements to maximize performance over extended temperatures.

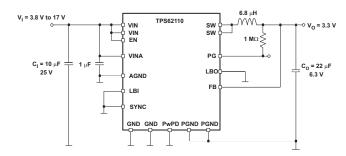

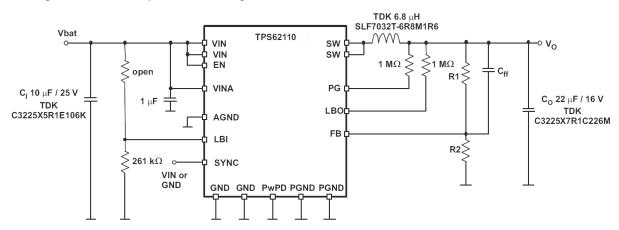

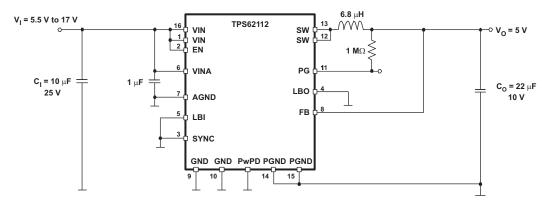

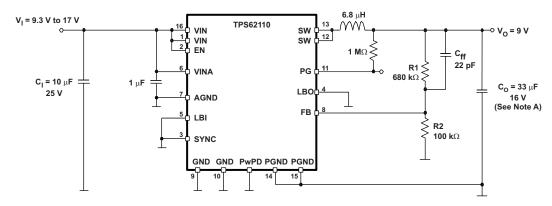

#### TYPICAL APPLICATION

(2) Custom temperature ranges available

#### DESCRIPTION/ORDERING INFORMATION

The TPS62110 is a low-noise synchronous step-down dc-dc converter that is ideally suited for systems powered from a 2-cell Li-ion battery or from a 12-V or 15-V rail.

The TPS62110 is a synchronous PWM converter with integrated N-channel and P-channel power MOSFET switches. Synchronous rectification is used to increase efficiency and to reduce external component count. To achieve highest efficiency over a wide load current range, the converter enters a power-saving, pulse-frequency modulation (PFM) mode at light load currents. Operating frequency is typically 1 MHz, allowing the use of small inductor and capacitor values. The device can be synchronized to an external clock signal in the range of 0.8 MHz to 1.4 MHz. For low noise operation, the converter can be operated in PWM-only mode. In the shutdown mode, the current consumption is reduced to less than 2 μA. The TPS62110 is available in the 16-pin (PWP) QFP package, and operates over a free-air temperature range of –55°C to 175°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

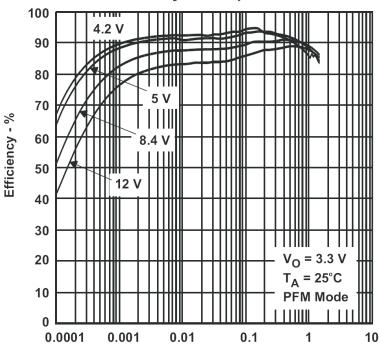

# TPS62110 Efficiency vs Output Current

I<sub>O</sub> - Output Current- A

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|------------------------|-----------------------|------------------|

| –55°C to 175°C | (PWP) QFP              | TPS62110HPWP          | TPS62110HPWP     |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

## ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                  |                                                              | UNIT                     |

|------------------|--------------------------------------------------------------|--------------------------|

| V <sub>CC</sub>  | Supply voltage at VIN, VINA                                  | -0.3 V to 20 V           |

|                  | Voltage at SW                                                | −0.3 V to V <sub>I</sub> |

| VI               | Voltage at EN, SYNC, LBO, PG                                 | –0.3 V to 20 V           |

|                  | Voltage at LBI, FB                                           | –0.3 V to 7 V            |

| Io               | Output current at SW                                         | 1500 mA                  |

| TJ               | Maximum junction temperature                                 | 190°C                    |

| T <sub>stg</sub> | Storage temperature                                          | -65°C to 175°C           |

|                  | Lead temperature 1,6 mm (1/16-inch) from case for 10 seconds | 300°C                    |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|               | THERMAL METRIC <sup>(1)</sup>                         | TPS62110<br>PWP | UNITS |

|---------------|-------------------------------------------------------|-----------------|-------|

|               |                                                       | 16 PINS         |       |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance <sup>(2)</sup> | 32.63           | °C/W  |

| ΨЈТ           | Junction-to-top characterization parameter (3)        | 0.848           | C/VV  |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

#### RECOMMENDED OPERATING CONDITIONS

|                |                                              | MIN | MAX   | UNIT |

|----------------|----------------------------------------------|-----|-------|------|

| $V_{CC}$       | Supply voltage at VIN, VINA                  | 3.1 | 17    | V    |

|                | Maximum voltage at power-good, LBO, EN, SYNC |     | 17    | V    |

|                | Continuous load current <sup>(1)</sup>       |     | 0.375 | Α    |

| T <sub>A</sub> | Operating temperature                        | -55 | 175   | °C   |

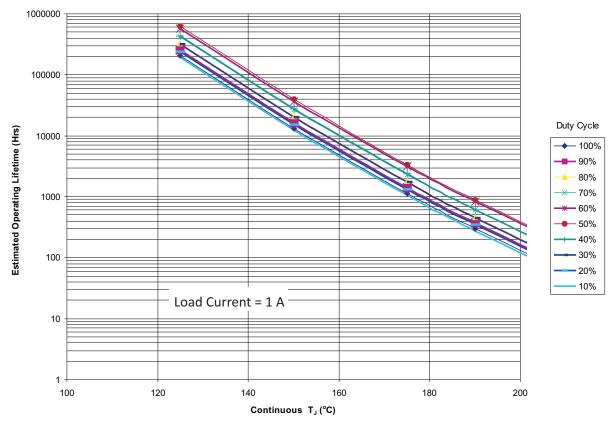

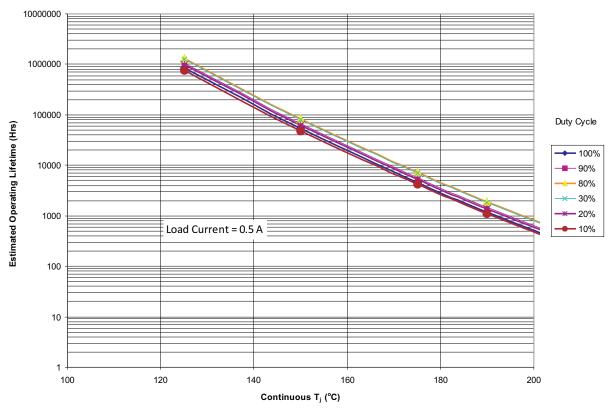

<sup>(1)</sup> Higher values of continuous load current may affect long-term reliability of the device at higher operating temperatures. Please refer to Figure 1 and Figure 2.

Product Folder Link(s): TPS62110-HT

## **ELECTRICAL CHARACTERISTICS**

$V_{I} = 12 \text{ V}, V_{O} = 3.3 \text{ V}, I_{O} = 600 \text{ mA}, EN = V_{I}$

|                      | PARAMETER                                                    | TEST CONDITIONS                                                      | T <sub>A</sub> = - | T <sub>A</sub> = -55°C to 125°C |      | T <sub>A</sub> = 175°C |          |      | UNIT     |

|----------------------|--------------------------------------------------------------|----------------------------------------------------------------------|--------------------|---------------------------------|------|------------------------|----------|------|----------|

|                      | FARAWETER                                                    | TEST CONDITIONS                                                      | MIN                | TYP                             | MAX  | MIN                    | TYP      | MAX  | UNIT     |

| SUPPLY               | CURRENT                                                      |                                                                      |                    |                                 |      |                        |          |      |          |

| VI                   | Input voltage range (1)                                      |                                                                      | 3.1                |                                 | 17   | 3.1                    |          | 17   | V        |

|                      | Operating guidesent current                                  | $I_{O}$ = 0 mA, SYNC = GND, $V_{I}$ = 7.2 V, $T_{A}$ = 25°C $^{(2)}$ |                    | 20                              |      |                        | 32       |      | lΛ       |

| I <sub>(Q)</sub>     | Operating quiescent current                                  | $I_O = 0$ mA, SYNC = GND,<br>$V_I = 17$ V $^{(2)}$                   |                    | 23                              | 30   |                        | 35       | 70   | μA       |

|                      | Chartelesses                                                 | EN = GND, V <sub>I</sub> = 12 V                                      |                    | 1.5                             | 5    |                        | 9.5      | 45   |          |

| I <sub>(SD)</sub>    | Shutdown current                                             | EN = GND, V <sub>I</sub> = 17 V                                      |                    | 1.5                             | 6    |                        | 10.2     | 45   | μA       |

| ENABLE               |                                                              |                                                                      | ·                  |                                 |      |                        |          |      |          |

| V <sub>IH</sub>      | EN high-level input voltage                                  |                                                                      | 1.3                |                                 |      | 1.3                    |          |      | V        |

| V <sub>IL</sub>      | EN low-level input voltage                                   |                                                                      |                    |                                 | 0.3  |                        |          | 0.3  | V        |

|                      | EN trip-point hysteresis                                     |                                                                      |                    | 170                             |      |                        | 170      |      | mV       |

| I <sub>IKG</sub>     | EN input leakage current                                     | EN = GND or V <sub>I</sub> , V <sub>I</sub> = 17 V                   |                    | 0.07                            | 0.2  |                        | 0.07     | 0.2  | μA       |

| I <sub>(EN)</sub>    | EN input current                                             | 0.6 V ≤ V <sub>(EN)</sub> ≤ 4 V                                      |                    | 10                              |      |                        | 5        |      | μA       |

| V <sub>(UVLO)</sub>  | Undervoltage lockout threshold                               | Input voltage falling                                                | 2.8                | 3                               | 3.1  | 2.8                    | 3        | 3.1  | V        |

|                      | Undervoltage lockout hysteresis                              |                                                                      |                    | 250                             |      |                        | 225      |      | mV       |

| POWER                | SWITCH                                                       | ·                                                                    | <u> </u>           |                                 |      |                        |          |      | -        |

| r <sub>DS(ON)</sub>  | P-channel MOSFET on-resistance                               | V <sub>I</sub> ≥ 5.4 V, I <sub>O</sub> = 350 mA                      |                    | 165                             | 250  |                        | 165      | 325  | mΩ       |

|                      | P-channel MOSFET leakage current                             | V <sub>DS</sub> = 17 V                                               |                    | 0.1                             | 1    |                        | 2        | 7    | μA       |

|                      | P-channel MOSFET current limit                               | V <sub>I</sub> = 7.2 V, V <sub>O</sub> = 3.3 V                       |                    | 2400                            |      |                        | 2600     |      | mA       |

| r <sub>DS(ON)</sub>  | N-channel MOSFET on-resistance                               | V <sub>I</sub> ≥ 5.4 V, I <sub>O</sub> = 350 mA                      |                    | 145                             | 200  |                        | 185      | 270  | mΩ       |

|                      | N-channel MOSFET<br>leakage<br>current                       | V <sub>DS</sub> = 17 V                                               |                    | 0.1                             | 3    |                        | 2.1      | 18   | μΑ       |

| POWER                | GOOD OUTPUT, LBI, LBO                                        |                                                                      |                    |                                 |      |                        |          |      |          |

| V <sub>(PG)</sub>    | Power good trip voltage                                      |                                                                      | \                  | / <sub>O</sub> – 1.6%           |      | Vo                     | o – 1.6% |      | V        |

|                      |                                                              | V <sub>O</sub> ramping positive                                      |                    | 50                              |      |                        | 57       |      |          |

|                      | Power good delay time                                        | V <sub>O</sub> ramping negative                                      |                    | 190                             |      |                        | 200      |      | μs       |

| V <sub>OL</sub>      | PG, LBO output low voltage                                   | $V_{(FB)} = 1.1 \times V_O$ nominal, $I_{OL} = 1$ mA                 |                    |                                 | 0.3  |                        |          | 0.3  | V        |

| I <sub>OL</sub>      | PG, LBO sink current                                         |                                                                      |                    | 1                               |      |                        | 1        |      | mA       |

| -                    | PG, LBO output leakage current                               | V <sub>(FB)</sub> = V <sub>O</sub> nominal                           |                    | 0.01                            | 0.25 |                        | 0.01     | 0.25 | μA       |

|                      | Minimum supply voltage for valid power good, LBI, LBO signal |                                                                      |                    | 3                               |      |                        | 3        |      | <b>V</b> |

| $V_{LBI}$            | Low battery input trip voltage                               | Input voltage falling                                                |                    | 1.256                           |      |                        | 1.260    |      | V        |

| ILBI                 | LBI input leakage current                                    |                                                                      |                    | 10                              | 100  |                        | 10       | 100  | nA       |

|                      | Low battery input trip-point accuracy                        |                                                                      |                    | 1.5                             |      |                        | 1.5      |      | %        |

| V <sub>LBI,HYS</sub> | Low battery input hysteresis                                 |                                                                      |                    | 25                              |      |                        | 25       |      | mV       |

<sup>(1)</sup> Not production tested(2) Device is not switching.

www.ti.com

## **ELECTRICAL CHARACTERISTICS (continued)**

$V_{I} = 12 \text{ V}, V_{O} = 3.3 \text{ V}, I_{O} = 600 \text{ mA}, EN = V_{I}$

|                     | PARAMETER                                                        | TEST CONDITIONS                                                                   | T <sub>A</sub> = -55°C to 125°C |       |      | T <sub>A</sub> = 175°C |       |      | UNIT |

|---------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------|-------|------|------------------------|-------|------|------|

| FARAINETER          |                                                                  | TEST CONDITIONS                                                                   | MIN TYP MA                      |       | MAX  | MIN TYP MAX            |       | UNII |      |

| OSCILL              | _ATOR                                                            |                                                                                   |                                 |       |      |                        |       |      |      |

| f <sub>S</sub>      | Oscillator frequency                                             |                                                                                   | 900                             | 1000  | 1100 | 900                    | 1000  | 1100 | kHz  |

| f <sub>(SYNC)</sub> | Synchronization range                                            | CMOS-logic clock signal on SYNC pin                                               | 800                             |       | 1410 | 800                    |       | 1410 | kHz  |

| V <sub>IH</sub>     | SYNC high-level input voltage                                    |                                                                                   | 1.5                             |       |      | 1.5                    |       |      | V    |

| $V_{IL}$            | SYNC low-level input voltage                                     |                                                                                   |                                 |       | 0.3  |                        |       | 0.3  | V    |

| I <sub>lkg</sub>    | SYNC input leakage current                                       | SYNC = GND or VIN                                                                 |                                 | 0.01  | 0.2  |                        | 0.07  | 0.2  | μA   |

|                     | SYNC trip-point hysteresis                                       |                                                                                   |                                 | 170   |      |                        | 170   |      | mV   |

|                     | SYNC input current                                               | 0.6 V ≤ V <sub>(SYNC)</sub> ≤ 4 V                                                 |                                 | 10    | 20   |                        | 5     | 20   | μΑ   |

|                     | Duty cycle of external clock signal                              |                                                                                   | 30                              |       | 90   | 30                     |       | 90   | %    |

| OUTPU               | Т                                                                |                                                                                   |                                 |       |      |                        |       |      |      |

| Vo                  | Adjustable output voltage range                                  |                                                                                   | 1.153                           |       | 16   | 1.153                  |       | 16   | V    |

| $V_{FB}$            | Feedback voltage                                                 |                                                                                   |                                 | 1.153 |      |                        | 1.153 |      | V    |

|                     | FB leakage current                                               |                                                                                   |                                 | 10    | 100  |                        | 290   | 2100 | nA   |

|                     | Feedback voltage tolerance                                       | V <sub>I</sub> = 3.1 V to 17 V,<br>0 mA < I <sub>O</sub> < 1500 mA <sup>(4)</sup> | -6                              |       | 7.5  | -7                     |       | 8    | %    |

|                     |                                                                  | V <sub>I</sub> ≥ 3 V (once undervoltage lockout voltage exceeded)                 |                                 | 100   |      |                        | 100   |      |      |

| Io                  | Maximum output current                                           | V <sub>i</sub> ≥ 3.5 V                                                            |                                 | 500   |      |                        | 500   |      | mA   |

| O                   |                                                                  | V <sub>1</sub> ≥ 4.3 V                                                            |                                 | 1200  |      |                        | 1100  |      |      |

|                     |                                                                  | V <sub>1</sub> ≥ 6 V                                                              |                                 | 1500  |      |                        | 1500  |      |      |

|                     | Current into internal voltage divider for fixed voltage versions |                                                                                   |                                 | 5     |      |                        | 5     |      | μA   |

|                     |                                                                  | V <sub>I</sub> = 7.2 V, V <sub>O</sub> = 3.3 V, I <sub>O</sub> = 600 mA           |                                 | 92    |      |                        | 82    |      |      |

| η                   | Efficiency                                                       | V <sub>I</sub> = 12 V, V <sub>O</sub> = 5 V, I <sub>O</sub> = 600 mA              |                                 | 92    |      |                        | 82    |      | %    |

|                     | Duty cycle range for main switches (3)                           | at 1 MHz                                                                          | 10                              |       | 100  | 10                     |       | 100  | %    |

|                     | Minimum t <sub>on</sub> time for main switch                     |                                                                                   |                                 | 100   |      |                        | 100   |      | ns   |

|                     | Start-up time                                                    | I <sub>O</sub> = 800 mA, V <sub>I</sub> = 12 V, V <sub>O</sub> = 3.3 V            |                                 |       |      |                        | 1     |      | ms   |

<sup>(3)</sup> Not production tested

© 2010–2011, Texas Instruments Incorporated

The maximum output current depends on the input voltage. See the maximum output current for further restrictions on the minimum input voltage.

- (1) See datasheet for absolute maximum and minimum recommended operating conditions.

- (2) Silicon operating life design goal is 10 years at 105°C junction temperature (does not include package interconnect life).

- (3) The predicted operating lifetime vs. junction temperature is based on reliability modeling using electromigration as the dominant failure mechanism affecting device wearout for the specific device process and design characteristics.

Figure 1. TPS62110HPWP Operating Life Derating Chart (Load Current = 1 A)

- (1) See datasheet for absolute maximum and minimum recommended operating conditions.

- (2) Silicon operating life design goal is 10 years at 105°C junction temperature (does not include package interconnect life)

- (3) The predicted operating lifetime vs. junction temperature is based on reliability modeling using electromigration as the dominant failure mechanism affecting device wearout for the specific device process and design characteristics.

Figure 2. TPS62110HPWP Operating Life Derating Chart (Load Current = 0.5 A)

7

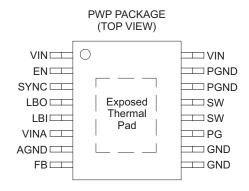

## **DEVICE INFORMATION**

## **PIN ASSIGNMENT TOP VIEW**

## **TERMINAL FUNCTIONS**

| TERMIN    | IAL    | I/O | DESCRIPTION                                                                                                                                                                                                            |

|-----------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.    | 1/0 | DESCRIPTION                                                                                                                                                                                                            |

| EN        | 2      | I   | Enable. A logic high enables the converter; logic low forces the device into shutdown mode reducing the supply current to less than 2 $\mu$ A.                                                                         |

| FB        | 8      | I   | Feedback pin for the fixed output voltage option. For the adjustable version, an external resistive divider is connected to this pin. The internal voltage divider is disabled for the adjustable version.             |

| LBO       | 4      | 0   | Open-drain, low-battery output. This pin is pulled low if LBI is below its threshold.                                                                                                                                  |

| GND       | 9, 10  | I   | Ground                                                                                                                                                                                                                 |

| LBI       | 5      | I   | Low-battery input                                                                                                                                                                                                      |

| sw        | 12, 13 | 0   | Connect the inductor to this pin. This pin is the switch pin and connected to the drain of the internal power MOSFETS.                                                                                                 |

| PG        | 11     | 0   | Power good comparator output. This is an open-drain output. A pullup resistor should be connected between PG and VOUT. The output goes active high when the output voltage is greater than 98.4% of the nominal value. |

| PGND      | 14, 15 | - 1 | Power ground. Connect all power grounds to this pin.                                                                                                                                                                   |

| AGND      | 7      | - 1 | Analog ground, connect to GND and PGND                                                                                                                                                                                 |

|           |        |     | Input for synchronization to external clock signal. Synchronizes the converter switching frequency to an external clock signal with CMOS level:                                                                        |

| SYNC      | 3      | I   | SYNC = HIGH: Low-noise mode enabled, fixed frequency PWM operation is forced                                                                                                                                           |

|           |        |     | SYNC = LOW (GND): Power save mode enabled, PFM/PWM mode enabled                                                                                                                                                        |

| VIN       | 1, 16  | 1   | Supply voltage input (power stage)                                                                                                                                                                                     |

| VINA      | 6      | I   | Supply voltage input (support circuits)                                                                                                                                                                                |

| PowerPAD™ |        |     | Connect to AGND                                                                                                                                                                                                        |

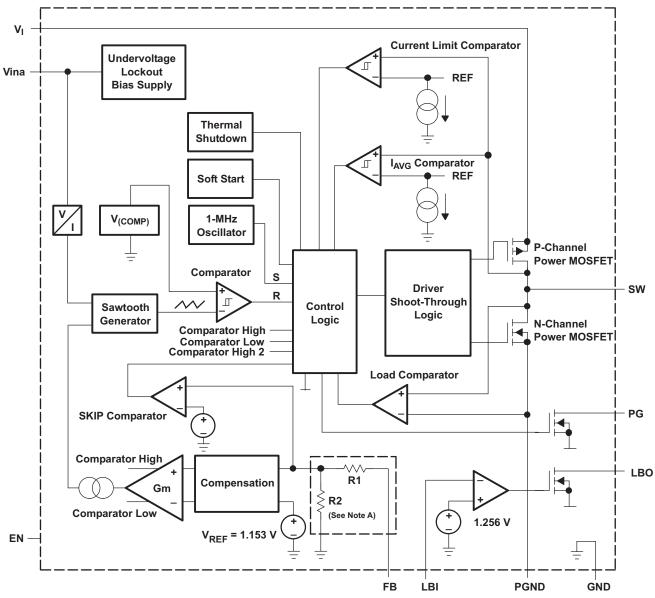

#### **FUNCTIONAL BLOCK DIAGRAM**

A. For the adjustable version (TPS62110), the internal feedback divider is disabled and the FB pin is directly connected to the internal GM amplifier.

## **TYPICAL CHARACTERISTICS**

**EFFICIENCY**

vs

**OUTPUT CURRENT**

Figure 5.

## TYPICAL CHARACTERISTICS (continued)

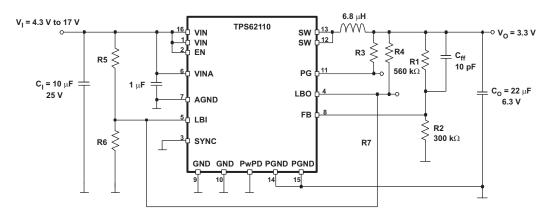

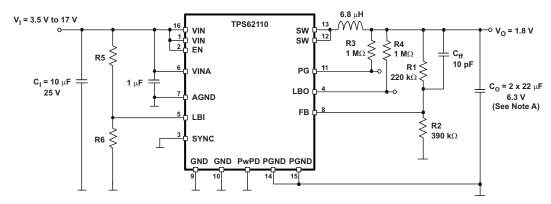

The graphs were generated using the EVM with the setup according to Figure 9 unless otherwise noted. The output voltage divider was adjusted according to Table 4

Figure 9. Test Setup

#### **DETAILED DESCRIPTION**

#### **OPERATION**

The TPS62110 is a synchronous step-down converter that operates with a 1-MHz fixed frequency pulse width modulation (PWM) at moderate-to-heavy load currents and enters the power save mode at light load current.

During PWM operation, the converter uses a unique fast response voltage mode control scheme with input voltage feedforward. Good line and load regulation is achieved with the use of small input and output ceramic capacitors. At the beginning of each clock cycle initiated by the clock signal (S), the P-channel MOSFET switch is turned on, and the inductor current ramps up until the comparator trips and the control logic turns the switch off. The switch is turned off by the current limit comparator if the current limit of the P-channel switch is exceeded. After the dead time prevents current shoot through, the N-channel MOSFET rectifier is turned on, and the inductor current ramps down. The next cycle is initiated by the clock signal turning off the N-channel rectifier, and turning on the P-channel switch.

The error amplifier as well as the input voltage determines the rise time of the sawtooth generator. Therefore, any change in input voltage or output voltage directly controls the duty cycle of the converter giving a very good line and load transient regulation.

## **CONSTANT FREQUENCY MODE OPERATION (SYNC = HIGH)**

In constant frequency mode, the output voltage is regulated by varying the duty cycle of the PWM signal in the range of 100% to 10%. Connecting the SYNC pin to a voltage greater than 1.5 V forces the converter to operate permanently in the PWM mode even at light or no-load currents. The advantage is that the converter operates with a fixed switching frequency that allows simple filtering of the switching frequency for noise-sensitive applications. In this mode, the efficiency is lower compared to the power save mode during light loads. The N-MOSFET of the devices stay on even when the current into the output drops to zero. This prevents the device from going into discontinuous mode, and the device transfers unused energy back to the input. Therefore, there is no ringing at the output, which usually occurs in discontinuous mode. The duty cycle range in constant frequency mode is 100% to 10%.

It is possible to switch from forced PWM mode to the power save mode during operation by pulling the SYNC pin LOW. The flexible configuration of the SYNC pin during operation of the device allows efficient power management by adjusting the operation of the TPS62110 to the specific system requirements.

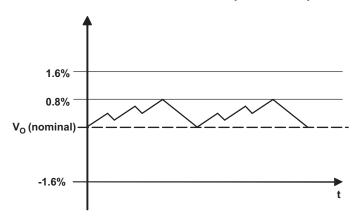

### POWER SAVE MODE OPERATION (SYNC = LOW)

As the load current decreases, the converter enters the power save mode operation. During power save mode, the converter operates with reduced switching frequency in pulse frequency modulation (PFM), and with a minimum quiescent current to maintain high efficiency. Whenever the average output current goes below the skip threshold, the converter enters the power save mode. The average current depends on the input voltage. It is about 200 mA at low input voltages and up to 400 mA with maximum input voltage. The average output current must be below the threshold for at least 32 clock cycles to enter the power save mode. During the power save mode, the output voltage is monitored with a comparator and the output voltage is regulated in to a typical value between the nominal output voltage and 0.8% above the nominal output voltage. When the output voltage falls below the nominal output voltage, the P-channel switch turns on. The P-channel switch is turned off as the peak switch current is reached. The N-channel rectifier is turned on, and the inductor current ramps down. As the inductor current approaches zero, the N-channel rectifier is turned off and the switch is turned on starting the next pulse. When the output voltage can not be reached with a single pulse, the device continues to switch with its normal operating frequency until the comparator detects the output voltage to be 0.8% above the nominal output voltage. This control method reduces the quiescent current to 20 µA (typical), and reduces the switching frequency to a minimum that achieves the highest converter efficiency.

### **DETAILED DESCRIPTION (continued)**

Figure 10. Power Save Mode Output Voltage Thresholds

The typical PFM (SKIP) current threshold for the TPS62110 is given by:

$$I_{SKIP} \approx \frac{V_I}{25 \Omega}$$

(1)

Equation 1 is valid for input voltages up to 7 V. For higher voltages, the skip current threshold is not increased further. The converter enters the fixed frequency PWM mode as soon as the output voltage falls below  $V_O - 1.6\%$  (nominal).

#### SOFT START

The TPS62110 has an internal soft-start circuit that limits the inrush current during start-up. This prevents possible voltage drops of the input voltage when a battery or a high-impedance power source is connected to the input of the TPS62110.

The soft start is implemented as a digital circuit increasing the switch current in steps of 300 mA, 600 mA, 1200 mA. The typical switch current limit is 2.4 A. Therefore, the start-up time depends on the output capacitor and load current. Typical start-up time with a 22-µF output capacitor and 800-mA load current is 1 ms.

## 100% DUTY CYCLE LOW DROPOUT OPERATION

The TPS62110 offers the lowest possible input to output voltage difference while still maintaining operation with the use of the 100% duty cycle mode. In this mode, the P-channel switch is constantly turned on. This is particularly useful in battery-powered applications to achieve the longest operation time, taking full advantage of the whole battery voltage range. The minimum input voltage to maintain regulation depends on the load current and output voltage, and is calculated as:

$$V_I \min = V_O \max + I_O \max \cdot \left( r_{DS(on)} \max + R_{(L)} \right)$$

(2)

with:

I<sub>O</sub>max = maximum output current plus inductor ripple current

$r_{DS(on)}$ max = maximum P-channel switch  $r_{DS(on)}$

$R_{(L)}$  = dc resistance of the inductor

V<sub>O</sub>max = nominal output voltage plus maximum output voltage tolerance

© 2010–2011, Texas Instruments Incorporated

## **DETAILED DESCRIPTION (continued)**

#### **ENABLE**

Logic low on EN forces the TPS62110 into shutdown. In shutdown, the power switch, drivers, voltage reference, oscillator, and all other functions are turned off. The supply current is reduced to less than 2  $\mu$ A in the shutdown mode. When the device is in thermal shutdown, the bandgap is forced to be switched on even if the device is set into shutdown by pulling EN to GND.

If an output voltage is present when the device is disabled, which could be due to an external voltage source or a super capacitor, the reverse leakage current is specified under electrical characteristics. Pulling the enable pin high starts up the TPS62110 with the soft start. If the EN pin is connected to any voltage other than  $V_I$  or GND, an increased leakage current of typically 10  $\mu$ A and up to 20  $\mu$ A can occur.

#### UNDERVOLTAGE LOCKOUT

The undervoltage lockout circuit prevents the device from misoperation at low-input voltages. It prevents the converter from turning on the switch or rectifier MOSFET under undefined conditions. The minimum input voltage to start up the TPS62110 is 3.4 V (worst case). The device shuts down at 2.8 V minimum.

#### SYNCHRONIZATION

If no clock signal is applied, the converter operates with a typical switching frequency of 1 MHz. It is possible to synchronize the converter to an external clock within a frequency range from 0.8 MHz to 1.4 MHz. The device automatically detects the rising edge of the first clock and synchronizes immediately to the external clock. If the clock signal is stopped, the converter automatically switches back to the internal clock and continues operation. The switch over is initiated if no rising edge on the SYNC pin is detected for a duration of four clock cycles. Therefore, the maximum delay time can be 6.25 µs if the internal clock has its minimum frequency of 800 kHz.

If the device is synchronized to an external clock, the power save mode is disabled, and the devices stay in forced PWM mode.

Connecting the SYNC pin to the GND pin enables the power save mode. The converter operates in the PWM mode at moderate-to-heavy loads, and in the PFM mode during light loads, which maintains high efficiency over a wide load current range.

### POWER GOOD COMPARATOR

The power good (PG) comparator has an open-drain output capable of sinking 1 mA (typical). The PG is active only when the device is enabled (EN=high). When the device is disabled (EN=low), the PG pin is pulled to GND.

The PG output is valid only after a 250- $\mu$ s delay when the device is enabled, and the supply voltage is greater than the undervoltage lockout  $V_{(I|V|O)}$ . PG is low during the first 250  $\mu$ s after shutdown and in shutdown.

The PG pin becomes active high when the output voltage exceeds 98.4% (typical) of its nominal value. Leave the PG pin unconnected when not used.

#### LOW-BATTERY DETECTOR

The low-battery output (LBO) is an open-drain type which goes low when the voltage at the low-battery input (LBI) falls below the trip point of 1.256 V  $\pm$ 1.5%. The voltage at which the low-battery warning is issued can be adjusted with a resistive divider as shown in Figure 11. The sum of resistors (R1 + R2) as well as the sum of (R5 + R6) is recommended to be in the 100 k $\Omega$  to 1 M $\Omega$  range for high efficiency at low output current. An external pullup resistor can be connected to OUT, or any other voltage rail in the voltage range of 0 V to 16 V. During start-up, the LBO output signal is invalid for the first 500  $\mu$ s. LBO is high impedance when the device is disabled. If the low-battery comparator function is not used, connect LBI to ground. The low-battery detector is disabled when the device is disabled.

The logic level of the LBO pin is not defined for the first 500 µs after EN is pulled high.

When the LBI is used to supervise the battery voltage and shut down the TPS62111 at low-input voltages, the battery voltage rises when the current drops to zero. The implemented hysteresis on the LBI pin may not be sufficient for all types of batteries. Figure 11 shows how an additional external hysteresis can be implemented.

## **DETAILED DESCRIPTION (continued)**

Figure 11. LBI With Increased Hysteresis

#### NO LOAD OPERATION

When the converter operates in the forced PWM mode and there is no load connected to the output, the converter regulates the output voltage by allowing the inductor current to reverse for a short time.

#### THEORY OR OPERATION / DESIGN PROCEDURE

| Table 1. List of Inductors (1)(2) | Table | 1 I | ist of | Inductors | (1)(2 |

|-----------------------------------|-------|-----|--------|-----------|-------|

|-----------------------------------|-------|-----|--------|-----------|-------|

| MANUFACTURER (3) | TYPE             | INDUCTANCE | DC RESISTANCE | SATURATION CURRENT |

|------------------|------------------|------------|---------------|--------------------|

| Coilcraft        | MSS6132-682      | 6.8 µH     | 65 mR (max)   | 1.5 A              |

| Epcos            | B82462G4682M     | 6.8 µH     | 50 mR (max)   | 1.5 A              |

| Sumida           | CDRH5D28-6R2     | 6.2 µH     | 33 mR (typ)   | 1.8 A              |

|                  | SLF6028T-6R8M1R5 | 6.8 µH     | 35 mR (typ)   | 1.5 A              |

| TDK              | SLF7032T-6R8M1R6 | 6.8 µH     | 41 mR (typ)   | 1.6 A              |

|                  | 7447789006       | 6.8 µH     | 44 mR (typ)   | 2.75 A             |

| Wurth            | 7447779006       | 6.8 µH     | 33 mR (typ)   | 3.3 A              |

|                  | 744053006        | 6.2 µH     | 45 mR (typ)   | 1.8 A              |

- (1) Component selections are for 25°C only and will change for new temperature range.

- (2) Components have not been validated for extreme high temperature operation.

- (3) The manufacturer's part numbers are used for test purposes only.

## **Inductor Selection**

The control loop of the TPS62110 family requires a certain value for the output inductor and the output capacitor for stable operation. As long as the nominal value of L × C  $\geq$  6.2  $\mu$ H × 22  $\mu$ F, the control loop has enough phase margin and the device is stable. Reducing the inductor value without increasing the output capacitor (or vice versa) may cause stability problems. There are applications where it may be useful to increase the value of the output capacitor, e.g., for a low transient output voltage change. From a stability point of view, the inductor value could be decreased to keep the L × C product constant. However, there are drawbacks if the inductor value is decreased. A low inductor value causes a high inductor ripple current and therefore reduces the maximum dc output current. Table 2 gives the advantages and disadvantages when designing the inductor and output capacitor.

Product Folder Link(s): TPS62110-HT

## Table 2. Advantages and Disadvantages When Designing the Inductor and Output Capacitor

|                        | INFLUENCE ON STABILITY                              | ADVANTAGE                                                                | DISADVANTAGE                                                                                                                    |

|------------------------|-----------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                        |                                                     | Less output voltage ripple                                               |                                                                                                                                 |

| Increase Cout (>22 μF) | Uncritical                                          | Less output voltage overshoot / undershoot during load transient         | None                                                                                                                            |

|                        |                                                     |                                                                          | Higher output voltage ripple                                                                                                    |

| Decrease Cout (<22 μF) | Critical<br>Increase inductor value >6.8 µH<br>also | None                                                                     | High output voltage overshoot / undershoot during load transient                                                                |

|                        |                                                     |                                                                          | Less gain and phase margin                                                                                                      |

|                        |                                                     | Less inductor current ripple                                             | More energy stored in the inductor → higher voltage overshoot during load transient                                             |

| Increase L (>6.8 µH)   | Uncritical                                          | Higher dc output current possible if operated close to the current limit | Smaller current rise → higher voltage undershoot during load transient → do not decrease the value of Cout due to these effects |

| Decrease L (<6.8 µH)   | Critical                                            | Small voltage overshoot / undershoot                                     | High inductor current ripple                                                                                                    |

|                        | Increase output capacitor value > 22 µF also        | during load transient                                                    | especially at high input voltage and low output voltage                                                                         |

As it is shown in Table 2, the inductor value can be increased to higher values. For good performance, the peak-to-peak inductor current ripple should be less than 30% of the maximum dc output current. Especially at input voltages above 12 V, it makes sense to increase the inductor value to keep the inductor current ripple low. In such applications, the inductor value can be increased to 10  $\mu$ H or 22  $\mu$ H. Values above 22  $\mu$ H should be avoided to keep the voltage overshoot during load transient in an acceptable range.

After choosing the inductor value, two additional inductor parameters should be considered:

- current rating of the inductor

- 2. dc resistance

The dc resistance of the inductance directly influences the efficiency of the converter. Therefore, an inductor with lowest dc resistance should be selected for highest efficiency. To avoid saturation of the inductor, the inductor should be rated at least for the maximum output current plus the inductor ripple current which is calculated as:

$$\Delta I_L = V_O \times \frac{1 - \frac{V_O}{V_I}}{L \times f} \qquad I_L \text{ m ax} = I_O \text{ m ax} + \frac{\Delta I_L}{2}$$

(3)

Where:

f = Switching frequency (1000 kHz typical)

L = Inductor value

$\Delta I_L$  = Peak-to-peak inductor ripple current

$I_{L}(max) = Maximum inductor current$

The highest inductor current occurs at maximum V<sub>I</sub>. A more conservative approach is to select the inductor current rating just for the maximum switch current of the TPS62110, which is 2.4 A (typically). See Table 1 for recommended inductors.

#### **OUTPUT CAPACITOR SELECTION**

A 22- $\mu$ F (typical) output capacitor is needed with a 6.8  $\mu$ H inductor. For an output voltage greater than 5 V, a 33- $\mu$ F (minimum) output capacitor is required for stability. For best performance, a low ESR ceramic output capacitor is needed.

The RMS ripple current is calculated as:

Submit Documentation Feedback

© 2010–2011, Texas Instruments Incorporated

www.ti.com

$$I_{RMS}(C_O) = V_O \times \frac{1 - \frac{V_O}{V_I}}{L \times f} \times \frac{1}{2 \times \sqrt{3}}$$

(4)

The overall output ripple voltage is the sum of the voltage spike caused by the output capacitor ESR plus the voltage ripple caused by charge and discharging the output capacitor:

$$\Delta V_O = V_O \times \frac{1 - \frac{V_O}{V_I}}{L \times f} \times \left( \frac{1}{8 \times C_O \times f} + R_{ESR} \right)$$

(5)

Where the highest output voltage ripple occurs at the highest input voltage V<sub>I</sub>.

#### INPUT CAPACITOR SELECTION

The nature of the buck converter is a pulsating input current; therefore, a low ESR input capacitor is required for best input voltage filtering, and minimizing the interference with other circuits caused by high input voltage spikes. The input capacitor should have a minimum value of 10 µF and can be increased without any limit for better input voltage filtering. The input capacitor should be rated for the maximum input ripple current calculated as:

$$I_{RMS} = I_{O} \text{ max} \times \sqrt{\frac{V_{O}}{V_{I}} \times \left(1 - \frac{V_{O}}{V_{I}}\right)}$$

(6)

The worst-case RMS ripple current occurs at D = 0.5 and is calculated as:  $I_{RMS} = I_{O}/2$ . Ceramic capacitors show a good performance because of their low ESR value, and they are less sensitive against voltage transients compared to tantalum capacitors. Place the input capacitor as close as possible to the input pin of the IC for best performance

#### FEEDFORWARD CAPACITOR SELECTION

The feedforward capacitor ( $C_{\rm ff}$ ) is needed to compensate for parasitic capacitance from the feedback pin to GND. Typically, a value of 4.7 pF to 22 pF is needed for an output voltage divider with a equivalent resistance (R1 in parallel with R2) in the 150 k $\Omega$  range. The value can be chosen based on best transient performance and lowest output voltage ripple in PFM mode.

#### RECOMMENDED CAPACITORS

It is recommended that only X5R or X7R ceramic capacitors be used as input/output capacitors. Ceramic capacitors show a dc-bias effect. This effect reduces the effective capacitance when a dc-bias voltage is applied across a ceramic capacitor, as on the output and input capacitor of a dc/dc converter. The effect may lead to a significant capacitance drop especially for high input/output voltages and small capacitor packages. See the manufacturer's data sheet about the performance with a dc bias voltage applied. It may be necessary to choose a higher voltage rating or nominal capacitance value to get the required value at the operating point. The capacitors listed in Table 3 have been tested with the TPS62110 with good performance.

Table 3. List of Capacitors (1)(2)

| MANUFACTURER | PART NUMBER     | SIZE | VOLTAGE | CAPACITANCE | TYPE    |

|--------------|-----------------|------|---------|-------------|---------|

| Toise Vuden  | TMK316BJ106KL   | 1206 | 25 V    | 10 μF       | Coromio |

| Taiyo Yuden  | EMK325BJ226KM   | 1210 | 16 V    | 22 µF       | Ceramic |

|              | C3225X5R1E106M  | 1210 | 25 V    | 10 μF       |         |

| TDK          | C3225X7R1C226M  | 1210 | 16 V    | 22 µF       | Ceramic |

|              | C3216X5R1E106MT | 1206 | 25 V    | 10 μF       |         |

- (1) Component selections are for 25°C only and will change for new temperature range.

- (2) Components have not been validated for extreme high temperature operation.

#### **APPLICATION INFORMATION**

A. For an output voltage lower than 2.5 V, an output capacitor of 33 μF or greater is recommended to improve load transient.

Figure 12. Standard Connection for Adjustable Version

$$V_{O} = V_{FB} \times \frac{R_{1} + R_{2}}{R_{2}}$$

$R_{1} = R_{2} \times \left(\frac{V_{O}}{V_{FB}}\right) - R_{2}$  (7)

$V_{FB} = 1.153 \text{ V}$

Table 4. Recommended Resistors (1)(2)

| OUTPUT VOLTAGE | R1     | R2     | NOMINAL VOLTAGE | TYPICAL Cff |

|----------------|--------|--------|-----------------|-------------|

| 9 V            | 680 kΩ | 100 kΩ | 8.993 V         | 22 pF       |

| 5 V            | 510 kΩ | 150 kΩ | 5.073 V         | 10 pF       |

| 3.3 V          | 560 kΩ | 300 kΩ | 3.305 V         | 10 pF       |

| 2.5 V          | 390 kΩ | 330 kΩ | 2.515 V         | 10 pF       |

| 1.8 V          | 220 kΩ | 390 kΩ | 1.803 V         | 10 pF       |

| 1.5 V          | 100 kΩ | 330 kΩ | 1.502 V         | 10 pF       |

- (1) Component selections are for 25°C only and will change for new temperature range..

- (2) Components have not been validated for extreme high temperature operation.

Figure 13. Standard Connection for Fixed Voltage Version

A. For an output voltage greater than 5 V, an output capacitor of 33 μF minimum is required for stability.

Figure 14. Application With 9 V Output

© 2010–2011, Texas Instruments Incorporated

## PACKAGE OPTION ADDENDUM

11-Apr-2013

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | U       | Pins | U   | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|-----|----------------------------|------------------|---------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      | Qty | (2)                        |                  | (3)                 |              | (4)               |         |

| TPS62110HPWP     | ACTIVE | HTSSOP       | PWP     | 16   | 90  | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -55 to 175   | S62110H           | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS62110-HT:

Catalog: TPS62110

11-Apr-2013

• Automotive: TPS62110-Q1

● Enhanced Product: TPS62110-EP

#### NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Automotive Q100 devices qualified for high-reliability automotive applications targeting zero defects

- Enhanced Product Supports Defense, Aerospace and Medical Applications

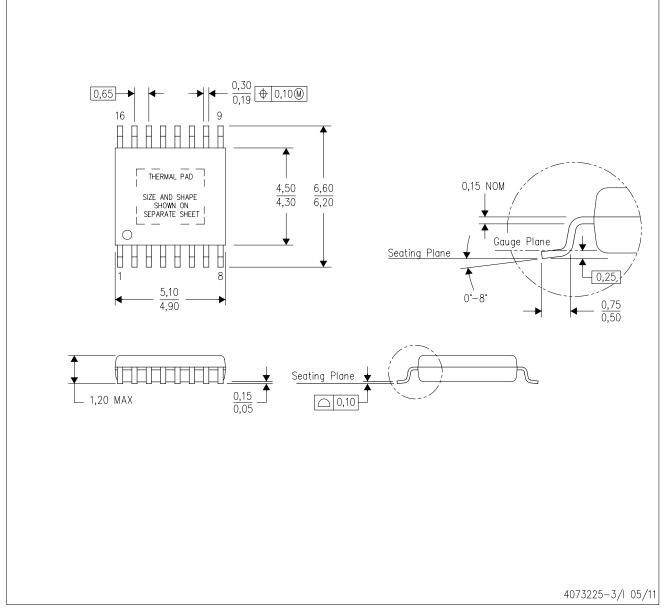

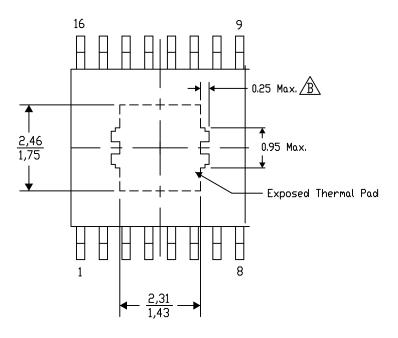

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PWP (R-PDSO-G16)

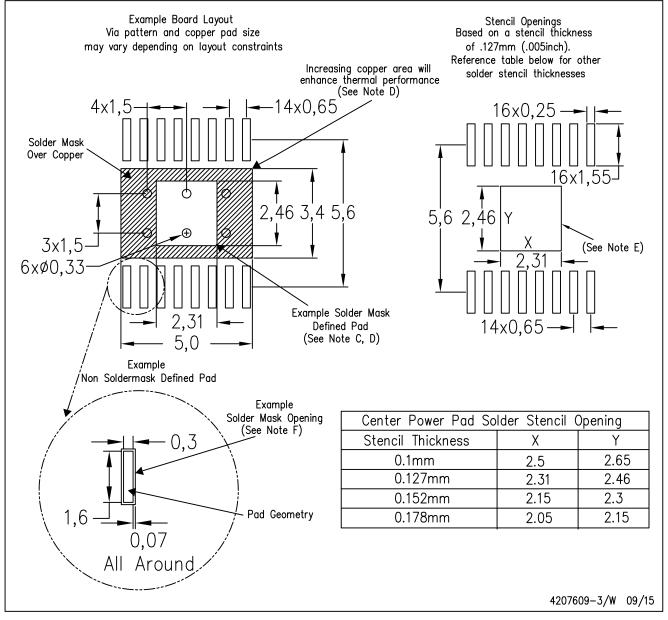

## PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# PWP (R-PDSO-G16) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-6/AO 01/16

NOTE: A. All linear dimensions are in millimeters

🛕 Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

## PWP (R-PDSO-G16)

## PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Texas Instruments: