#### Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

FAIRCHILD

January 2016

# Single-Channel: 6N137M, HCPL2601M, HCPL2611M Dual-Channel: HCPL2630M, HCPL2631M 8-Pin DIP High-Speed 10 MBit/s Logic Gate Optocouplers

#### **Features**

- Very High Speed 10 MBit/s

- Superior CMR 10 kV/µs

- Fan-out of 8 Over -40°C to +85°C

- · Logic Gate Output

- Strobable Output

- Wired OR-open Collector

- · Safety and Regulatory Approvals

- UL1577, 5,000 VAC<sub>RMS</sub> for 1 Minute

- DIN EN/IEC60747-5-5

## **Applications**

- · Ground Loop Elimination

- LSTTL to TTL, LSTTL or 5 V CMOS

- · Line Receiver, Data Transmission

- · Data Multiplexing

- Switching Power Supplies

- · Pulse Transformer Replacement

- Computer-peripheral Interface

## Description

The 6N137M, HCPL2601M, HCPL2611M single-channel and HCPL2630M, HCPL2631M dual-channel optocouplers consist of a 850 nm AlGaAS LED, optically coupled to a very high speed integrated photo-detector logic gate with a strobable output. This output features an open collector, thereby permitting wired OR outputs. The switching parameters are guaranteed over the temperature range of -40°C to +85°C. A maximum input signal of 5 mA will provide a minimum output sink current of 13 mA (fan out of 8).

An internal noise shield provides superior common mode rejection of typically 10 kV/µs. The HCPL2601M and HCPL2631M has a minimum CMR of 5 kV/µs. The HCPL2611M has a minimum CMR of 10 kV/µs.

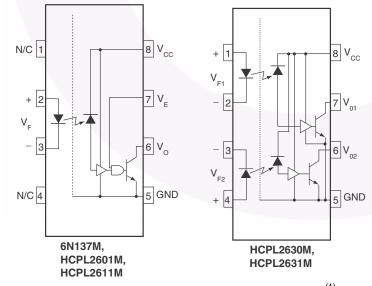

#### **Schematics**

A 0.1 $\mu$ F bypass capacitor must be connected between pins 8 and 5<sup>(1)</sup>.

Figure 1. Schematics

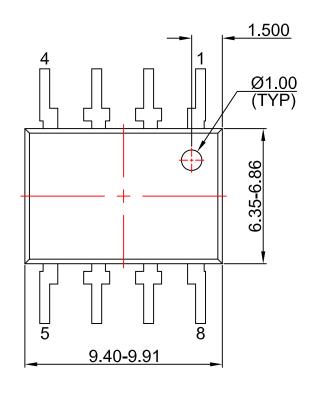

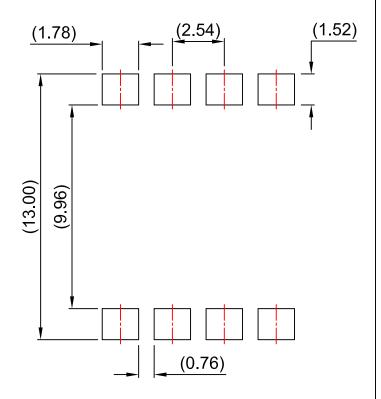

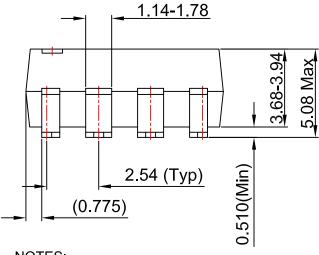

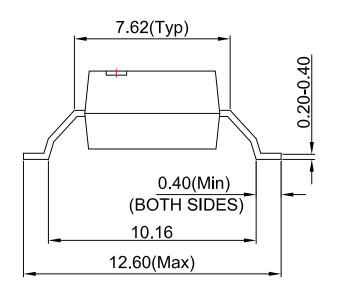

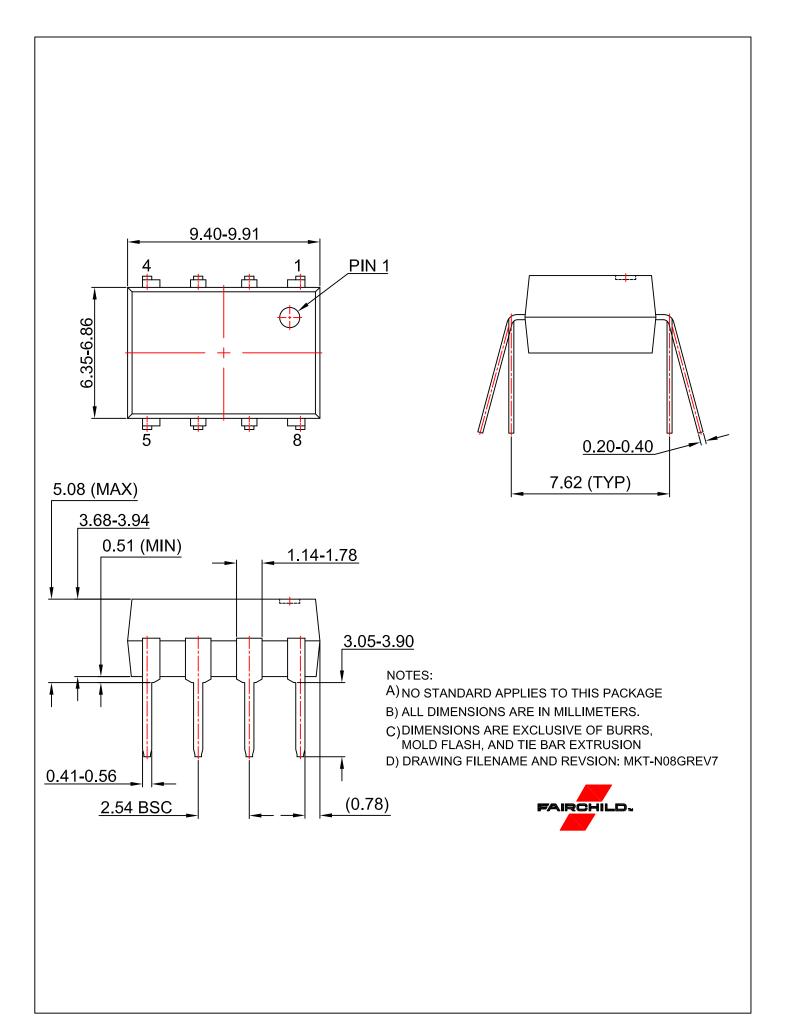

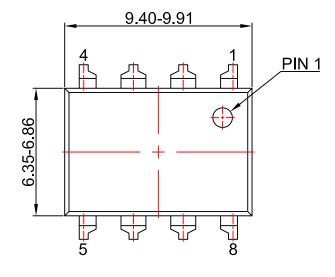

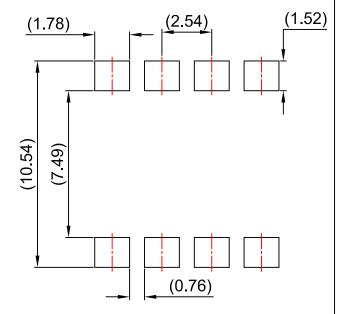

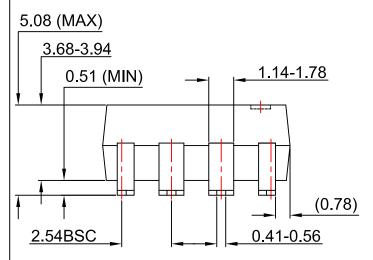

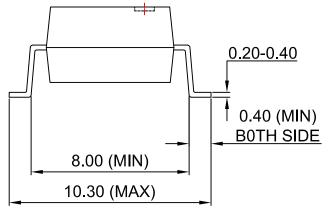

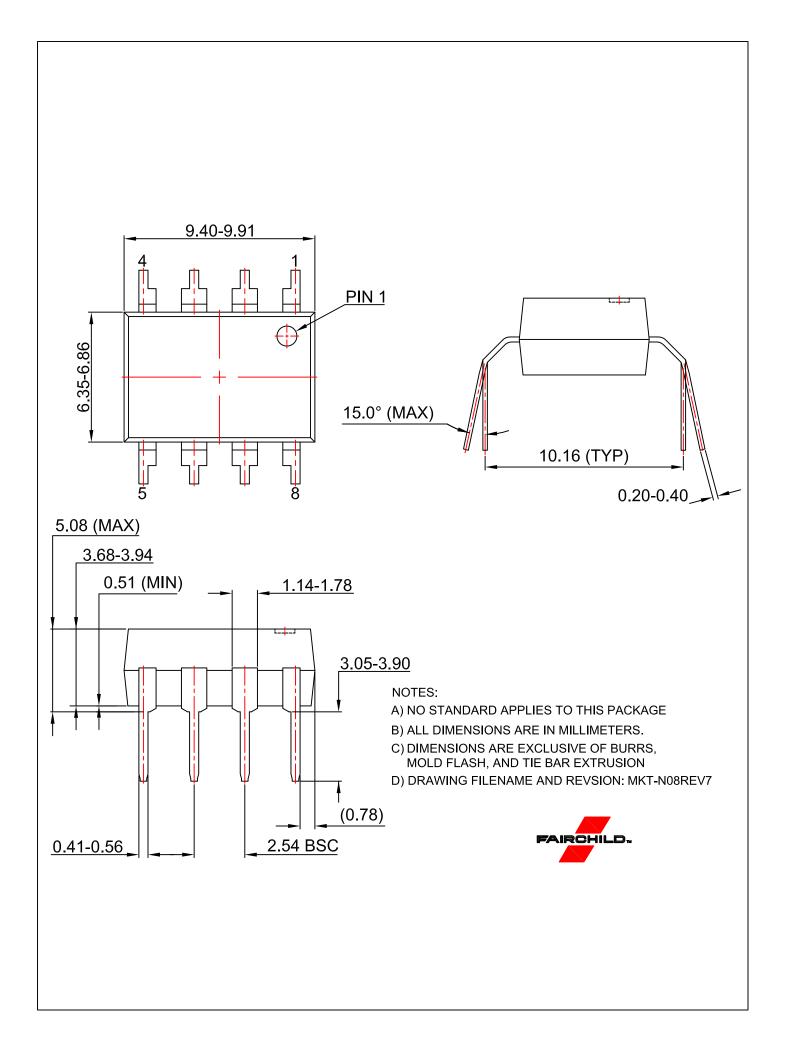

## **Package Outlines**

Figure 2. Package Options

Truth Table (Positive Logic)

| Tradit Table (Footsto Logic) |                   |  |  |  |

|------------------------------|-------------------|--|--|--|

| Enable                       | Output            |  |  |  |

| Н                            | L                 |  |  |  |

| Н                            | Н                 |  |  |  |

| L                            | Н                 |  |  |  |

| L                            | Н                 |  |  |  |

| NC                           | L                 |  |  |  |

| NC                           | Н                 |  |  |  |

|                              | Enable H H L L NC |  |  |  |

## Safety and Insulation Ratings

As per DIN EN/IEC 60747-5-5, this optocoupler is suitable for "safe electrical insulation" only within the safety limit data. Compliance with the safety ratings shall be ensured by means of protective circuits.

| Parameter                                                                           |  | Characteristics        |           |

|-------------------------------------------------------------------------------------|--|------------------------|-----------|

|                                                                                     |  | < 150 V <sub>RMS</sub> | I–IV      |

| Installation Classifications per DIN VDE 0110/1.89 Table 1, For Rated Mains Voltage |  | < 300 V <sub>RMS</sub> | I–IV      |

|                                                                                     |  | < 450 V <sub>RMS</sub> | I–III     |

|                                                                                     |  | < 600 V <sub>RMS</sub> | I–III     |

| Climatic Classification                                                             |  |                        | 40/100/21 |

| Pollution Degree (DIN VDE 0110/1.89)                                                |  |                        | 2         |

| Comparative Tracking Index                                                          |  |                        | 175       |

| Symbol                | Parameter                                                                                                                                 | Value             | Unit              |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|

| V                     | Input-to-Output Test Voltage, Method A, $V_{IORM} \times 1.6 = V_{PR}$ , Type and Sample Test with $t_m = 10$ s, Partial Discharge < 5 pC | 1,335             | V <sub>peak</sub> |

| V <sub>PR</sub>       | Input-to-Output Test Voltage, Method B, $V_{IORM}$ x 1.875 = $V_{PR}$ , 100% Production Test with $t_m$ = 1 s, Partial Discharge < 5 pC   | 1,669             | V <sub>peak</sub> |

| $V_{IORM}$            | Maximum Working Insulation Voltage                                                                                                        | 890               | $V_{peak}$        |

| $V_{IOTM}$            | Highest Allowable Over-Voltage                                                                                                            | 6,000             | $V_{peak}$        |

|                       | External Creepage                                                                                                                         | ≥ 8.0             | mm                |

|                       | External Clearance                                                                                                                        | ≥ 7.4             | mm                |

|                       | External Clearance (for Option TV, 0.4" Lead Spacing)                                                                                     | ≥ 10.16           | mm                |

| DTI                   | Distance Through Insulation (Insulation Thickness)                                                                                        | ≥ 0.5             | mm                |

| T <sub>S</sub>        | Case Temperature <sup>(2)</sup>                                                                                                           | 150               | °C                |

| I <sub>S,INPUT</sub>  | Input Current <sup>(2)</sup>                                                                                                              | 200               | mA                |

| P <sub>S,OUTPUT</sub> | Output Power (Duty Factor ≤ 2.7%) <sup>(2)</sup>                                                                                          | 300               | mW                |

| R <sub>IO</sub>       | Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500 V <sup>(2)</sup>                                                          | > 10 <sup>9</sup> | Ω                 |

#### Notes:

- 1. The  $V_{CC}$  supply to each optoisolator must be bypassed by a 0.1  $\mu$ F capacitor or larger. This can be either a ceramic or solid tantalum capacitor with good high frequency characteristic and should be connected as close as possible to the package V<sub>CC</sub> and GND pins of each device.

- 2. Safety limit value maximum values allowed in the event of a failure.

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_A = 25$ °C unless otherwise specified.

| Symbol               | Parameter                                                                         | Value          | Unit           |       |  |

|----------------------|-----------------------------------------------------------------------------------|----------------|----------------|-------|--|

| T <sub>STG</sub>     | Storage Temperature                                                               |                | -40 to +125    | °C    |  |

| T <sub>OPR</sub>     | Operating Temperature                                                             |                | -40 to +100    | °C    |  |

| TJ                   | Junction Temperature                                                              |                | -40 to +125    | °C    |  |

| T <sub>SOL</sub>     | Lead Solder Temperature                                                           |                | 260 for 10 sec | °C    |  |

| Symbol               | Parameter                                                                         | Device         | Value          | Unit  |  |

| EMITTER              |                                                                                   | •              |                |       |  |

| l (o)(a)             | DC/Average Ferward Input Current Per Channel                                      | Single Channel | 50             | m A   |  |

| I <sub>F</sub> (avg) | DC/Average Forward Input Current Per Channel  Dual Channel                        |                | 30             | mA    |  |

| V <sub>E</sub>       | Enable Input Voltage Not to Exceed V <sub>CC</sub> by more than 500 mV Single Cha |                | 5.5            | V     |  |

| $V_{R}$              | Reverse Input Voltage Per Channel                                                 | All            | 5.0            | V     |  |

| D                    | Input Pawar Dissinction Per Channel                                               | Single Channel | 100            | mW    |  |

| P <sub>I</sub>       | Input Power Dissipation Per Channel                                               | Dual Channel   | 45             | IIIVV |  |

| DETECTOR             |                                                                                   |                |                |       |  |

| V <sub>CC</sub>      | Supply Voltage                                                                    | All            | -0.5 to 7.0    | V     |  |

| I <sub>O</sub> (avg) | Average Output Current Per Channel                                                | All            | 25             |       |  |

| I <sub>O</sub> (pk)  | Peak Output Current Per Channel All                                               |                | 50             | mA    |  |

| Vo                   | Output Voltage Per Channel                                                        | All            | -0.5 to 7.0    | V     |  |

| D .                  | Output Power Discipation Per Channel                                              | Single Channel | 85             | mW    |  |

| P <sub>O</sub>       | Output Power Dissipation Per Channel  Dual C                                      |                | 60             | IIIVV |  |

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol          | Parameter                     | Min.               | Max.            | Unit |

|-----------------|-------------------------------|--------------------|-----------------|------|

| V <sub>CC</sub> | Supply Voltage                | 4.5                | 5.5             | V    |

| I <sub>FL</sub> | Input Current, Low Level      | 0                  | 250             | μA   |

| I <sub>FH</sub> | Input Current, High Level     | 6.3 <sup>(3)</sup> | 20.0            | mA   |

| V <sub>EL</sub> | Enable Voltage, Low Level     | 0                  | 0.8             | V    |

| V <sub>EH</sub> | Enable Voltage, High Level    | 2.0                | V <sub>CC</sub> | V    |

| T <sub>A</sub>  | Ambient Operating Temperature | -40                | +85             | °C   |

| N               | Fan Out (TTL load)            |                    | 8               |      |

#### Note:

3. 6.3 mA is a guard banded value which allows for at least 20% CTR degradation. Initial input current threshold value is 5.0 mA or less.

Individual Component Characteristics ( $V_{CC} = 5.5 \text{ V}$ ,  $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$  unless otherwise specified)

| Symbol                    | Parameter                                  | Device         | Test Conditions                                                    | Min. | Тур. | Max. | Unit     |

|---------------------------|--------------------------------------------|----------------|--------------------------------------------------------------------|------|------|------|----------|

| EMITTER                   |                                            |                |                                                                    |      |      |      |          |

| V <sub>F</sub>            | Input Forward Voltage                      | All            | $I_F = 10 \text{ mA}, T_A = 25^{\circ}\text{C}$                    |      | 1.45 | 1.70 | V        |

| ٧F                        | iliput Forward voltage                     | All            | I <sub>F</sub> = 10 mA                                             |      |      | 1.80 | <b>"</b> |

| B <sub>VR</sub>           | Input Reverse Breakdown<br>Voltage         | All            | Ι <sub>R</sub> = 10 μΑ                                             | 5.0  |      |      | V        |

| C <sub>IN</sub>           | Input Capacitance                          | All            | $V_F = 0, f = 1 \text{ MHz}$                                       |      | 60   |      | pF       |

| $\Delta V_F / \Delta T_A$ | Temperature Coefficient of Forward Voltage | All            | I <sub>F</sub> = 10 mA                                             |      | -1.4 |      | mV/°C    |

| DETECTO                   | R                                          |                |                                                                    |      |      |      |          |

| 1                         | La ria Lava Caranta Caranta                | Single Channel | $I_F = 10 \text{ mA}, V_O = \text{Open},$<br>$V_E = 0.5 \text{ V}$ |      | 8    | 13   | mΛ       |

| ICCL                      | Logic Low Supply Current                   | Dual Channel   | $I_{F1} = I_{F2} = 10 \text{ mA},$<br>$V_O = \text{Open}$          |      | 14   | 21   | 21 mA    |

| I <sub>CCH</sub>          | Logic High Supply Current                  | Single Channel | $I_F = 0$ mA, $V_O = Open$ ,<br>$V_E = 0.5$ V                      |      | 6    | 10   | mA       |

|                           | 27                                         | Dual Channel   | $I_F = 0 \text{ mA}, V_O = \text{Open},$                           |      | 10   | 15   |          |

| I <sub>EL</sub>           | Low Level Enable Current                   | Single Channel | V <sub>E</sub> = 0.5 V                                             |      | -0.7 | -1.6 | mA       |

| I <sub>EH</sub>           | High Level Enable Current                  | Single Channel | V <sub>E</sub> = 2.0 V                                             |      | -0.5 | -1.6 | mA       |

| V <sub>EL</sub>           | Low Level Enable Voltage                   | Single Channel | $I_F = 10 \text{ mA}^{(4)}$                                        |      |      | 0.8  | V        |

| V <sub>EH</sub>           | High Level Enable Voltage                  | Single Channel | I <sub>F</sub> = 10 mA                                             | 2.0  |      |      | V        |

#### Note:

4. Enable Input – No pull up resistor required as the device has an internal pull up resistor.

**Transfer Characteristics** ( $V_{CC} = 5.5 \text{ V}$ ,  $T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$  unless otherwise specified)

| Symbol          | Parameter                 | Device | Test Conditions                                                        | Min. | Тур. | Max. | Unit |

|-----------------|---------------------------|--------|------------------------------------------------------------------------|------|------|------|------|

| I <sub>FT</sub> | Input Threshold Current   | All    | $V_O = 0.6 \text{ V}, V_E = 2.0 \text{ V}, I_{OL} = 13 \text{ mA}$     |      | 3    | 5    | mA   |

| I <sub>OH</sub> | HIGH Level Output Current | All    | $V_O = 5.5 \text{ V}, I_F = 250 \mu\text{A}, \ V_E = 2.0 V$            |      |      | 100  | μΑ   |

| V <sub>OL</sub> | LOW Level Output Voltage  | All    | $I_F = 5 \text{ mA}, V_E = 2.0 \text{ V},$<br>$I_{OL} = 13 \text{ mA}$ |      | 0.4  | 0.6  | ٧    |

### **Electrical Characteristics** (Continued)

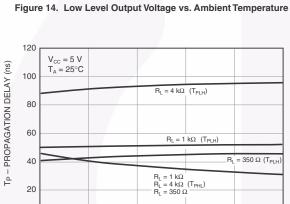

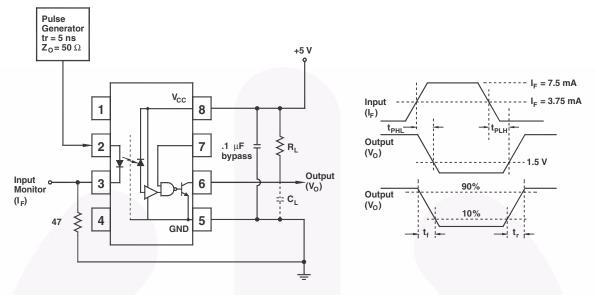

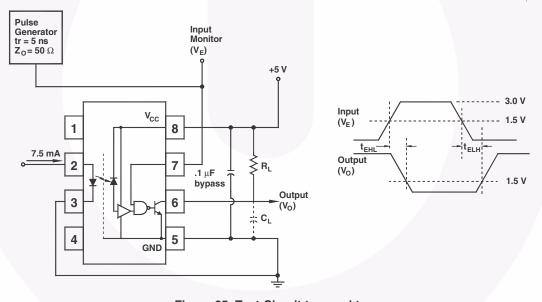

**Switching Characteristics** ( $V_{CC} = 5 \text{ V}$ ,  $I_F = 7.5 \text{ mA}$ ,  $T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$  unless otherwise specified)

| Symbol                             | Parameter                                                | Device                  | Test Conditions                                                                                                                                                                                                 | Min.   | Тур.   | Max. | Unit |

|------------------------------------|----------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------|------|

| t <sub>PHL</sub>                   | Propagation Delay                                        | All                     | $R_L = 350 \Omega$ , $C_L = 15 pF$ ,<br>$T_A = 25^{\circ}C^{(5)}$ (Fig. 14)                                                                                                                                     | 25     | 40     | 75   | - ns |

| PHL                                | Time to Logic LOW                                        | 7 til                   | $R_L = 350 \ \Omega, \ C_L = 15 \ pF^{(5)}$ (Fig. 14)                                                                                                                                                           |        |        | 100  | 113  |

| tou                                | Propagation Delay                                        | All                     | $R_L = 350 \Omega$ , $C_L = 15 pF$<br>$T_A = 25^{\circ}C^{(6)}$ (Fig. 14)                                                                                                                                       | 20     | 40     | 75   | - ns |

| <sup>t</sup> PLH                   | Time to Logic HIGH                                       | 7 til                   | $R_L = 350 \ \Omega, \ C_L = 15 \ pF^{(6)}$ (Fig. 14)                                                                                                                                                           |        |        | 100  | 113  |

| t <sub>PHL</sub> -t <sub>PLH</sub> | Pulse Width Distortion                                   | All                     | $R_L = 350 \Omega, C_L = 15 pF$ (Fig. 14)                                                                                                                                                                       |        | 1      | 35   | ns   |

| t <sub>R</sub>                     | Output Rise Time (10% to 90%)                            | All                     | $R_L = 350 \Omega, C_L = 15 pF^{(7)}$ (Fig. 14)                                                                                                                                                                 |        | 30     |      | ns   |

| t <sub>F</sub>                     | Output Fall Time (90% to 10%)                            | All                     | $R_L = 350 \Omega, C_L = 15 pF^{(8)}$ (Fig. 14)                                                                                                                                                                 |        | 10     |      | ns   |

| t <sub>EHL</sub>                   | Enable Propagation<br>Delay Time to Output<br>LOW Level  | Single Channel          | $V_{EH} = 3.5 \text{ V}, R_L = 350 \Omega,$ $C_L = 15 \text{ pF}^{(9)} \text{ (Fig. 15)}$                                                                                                                       |        | 15     |      | ns   |

| t <sub>ELH</sub>                   | Enable Propagation<br>Delay Time to Output<br>HIGH Level | Single Channel          | $V_{EH} = 3.5 \text{ V}, R_L = 350 \Omega,$ $C_L = 15 \text{ pF}^{(10)} \text{ (Fig. 15)}$                                                                                                                      |        | 15     |      | ns   |

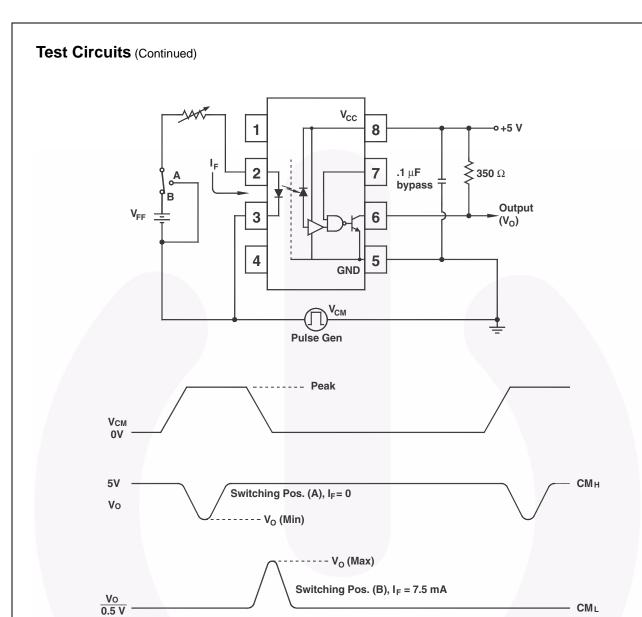

|                                    |                                                          | 6N137M,<br>HCPL2630M    | $I_F = 0 \text{ mA}, V_{CM} = 50 V_{PEAK}, R_L = 350 \Omega, T_A = 25^{\circ}C^{(11)}$                                                                                                                          |        | 10,000 |      |      |

| CM <sub>H</sub>                    | Common Mode<br>Transient Immunity                        | HCPL2601M,<br>HCPL2631M | (Fig. 16)                                                                                                                                                                                                       | 5000   | 10,000 |      | V/µs |

|                                    | at Logic High                                            | HCPL2611M               | $ \begin{aligned} & I_{\text{F}} = 0 \text{ mA, V}_{\text{CM}} = 400 \text{ V}_{\text{PEAK}}, \\ & R_{\text{L}} = 350 \ \Omega,  T_{\text{A}} = 25^{\circ}\text{C}^{(11)} \\ & (\text{Fig. 16}) \end{aligned} $ | 10,000 | 15,000 |      |      |

|                                    |                                                          | 6N137M,<br>HCPL2630M    | $V_{CM} = 50 V_{PEAK}$                                                                                                                                                                                          |        | 10,000 |      |      |

| CM <sub>L</sub>                    | Common Mode<br>Transient Immunity                        | HCPL2601M,<br>HCPL2631M | R <sub>L</sub> = 350 $\Omega$ , T <sub>A</sub> = 25°C <sup>(11)</sup> (Fig. 16)                                                                                                                                 | 5000   | 10,000 |      | V/µs |

|                                    | at Logic Low                                             | HCPL2611M               | $V_{CM} = 400 V_{PEAK},$ $R_L = 350 \Omega, T_A = 25^{\circ}C^{(11)}$ (Fig. 16)                                                                                                                                 | 10,000 | 15,000 |      |      |

#### Notes:

- 5. t<sub>PHL</sub> Propagation delay is measured from the 3.75 mA level on the LOW to HIGH transition of the input current pulse to the 1.5 V level on the HIGH to LOW transition of the output voltage pulse.

- 6. t<sub>PLH</sub> Propagation delay is measured from the 3.75 mA level on the HIGH to LOW transition of the input current pulse to the 1.5 V level on the LOW to HIGH transition of the output voltage pulse.

- 7. t<sub>R</sub> Rise time is measured from the 90% to the 10% levels on the LOW to HIGH transition of the output pulse.

- 8. t<sub>F</sub> Fall time is measured from the 10% to the 90% levels on the HIGH to LOW transition of the output pulse.

- 9. t<sub>EHL</sub> Enable input propagation delay is measured from the 1.5 V level on the LOW to HIGH transition of the input voltage pulse to the 1.5 V level on the HIGH to LOW transition of the output voltage pulse.

- 10.  $t_{\text{ELH}}$  Enable input propagation delay is measured from the 1.5 V level on the HIGH to LOW transition of the input voltage pulse to the 1.5 V level on the LOW to HIGH transition of the output voltage pulse.

- 11. Common mode transient immunity in logic high level is the maximum tolerable (positive)  $dV_{cm}/dt$  on the leading edge of the common mode pulse signal,  $V_{CM}$ , to assure that the output will remain in a logic high state (i.e.,  $V_O > 2.0 \text{ V}$ ). Common mode transient immunity in logic low level is the maximum tolerable (negative)  $dV_{cm}/dt$  on the trailing edge of the common mode pulse signal,  $V_{CM}$ , to assure that the output will remain in a logic low state (i.e.,  $V_O < 0.8 \text{ V}$ ).

## **Electrical Characteristics** (Continued)

Isolation Characteristics (T<sub>A</sub> =25°C unless otherwise specified.)

| Symbol           | Parameter                                  | Device | Test Conditions                                                                                      | Min.  | Тур.             | Max. | Unit               |

|------------------|--------------------------------------------|--------|------------------------------------------------------------------------------------------------------|-------|------------------|------|--------------------|

| V <sub>ISO</sub> | Withstand Insulation<br>Test Voltage       | All    | Relative Humidity $\leq$ 50%, $I_{I-O} \leq$ 10 $\mu$ A, $t=1$ min, $f=50$ Hz <sup>(12)(13)</sup>    | 5,000 |                  |      | VAC <sub>RMS</sub> |

| R <sub>I-O</sub> | Resistance<br>(Input to Output)            | All    | V <sub>I-O</sub> = 500 V <sub>DC</sub> <sup>(12)</sup>                                               |       | 10 <sup>11</sup> |      | Ω                  |

| C <sub>I-O</sub> | Capacitance<br>(Input to Output)           | All    | $f = 1 \text{ MHz}, V_{I-O} = 0 V_{DC}^{(12)}$                                                       |       | 1                |      | pF                 |

| I <sub>I-O</sub> | Input-Output Insulation<br>Leakage Current | All    | Relative Humidity $\leq$ 45%,<br>V <sub>I-I</sub> = 3000 V <sub>DC</sub> , t = 5 sec <sup>(12)</sup> |       |                  | 1.0  | μA                 |

#### Notes:

- 12. Device is considered a two terminal device: pins 1, 2, 3 and 4 are shorted together and pins 5, 6, 7 and 8 are shorted together.

- 13. 5000 VAC $_{RMS}$  for 1 minute duration is equivalent to 6000 VAC $_{RMS}$  for 1 second duration.

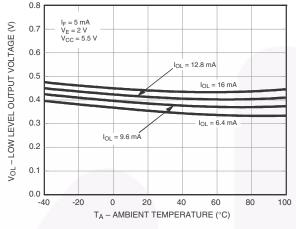

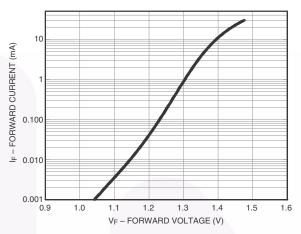

## **Typical Performance Curves**

For Single-Channel Devices: 6N137M, HCPL2601M, and HCPL2611M

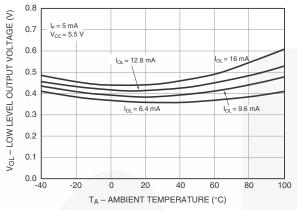

Figure 3. Low Level Output Voltage vs. Ambient Temperature

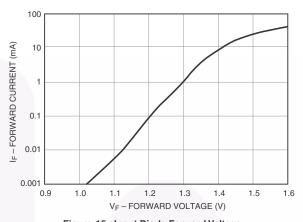

Figure 4. Input Diode Forward Voltage vs. Forward Current

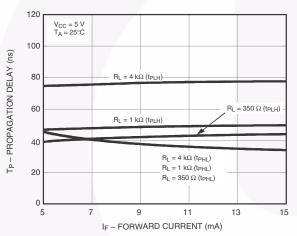

Figure 5. Switching Time vs. Forward Current

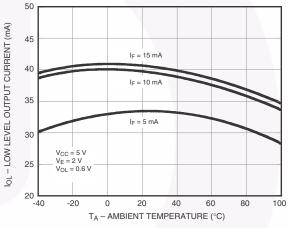

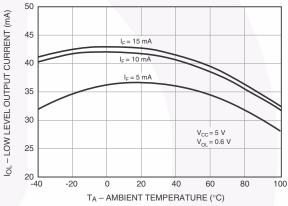

Figure 6. Low Level Output vs. Ambient Temperature

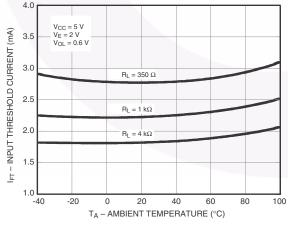

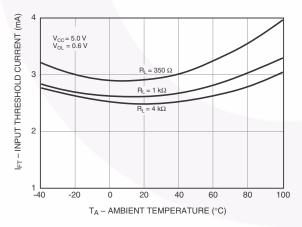

Figure 7. Input Threshold Current vs. Ambient Temperature

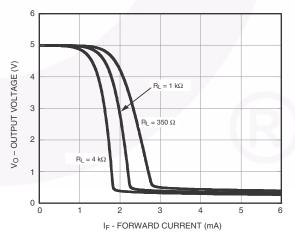

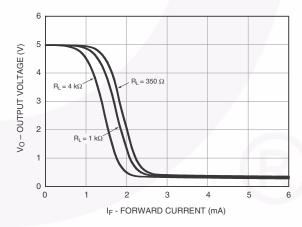

Figure 8. Output Voltage vs. Input Forward Current

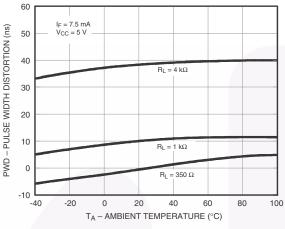

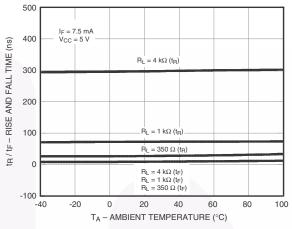

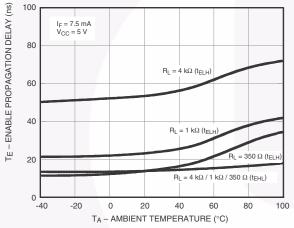

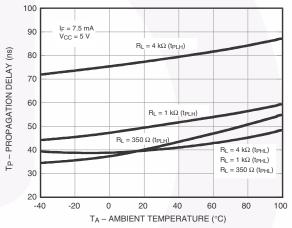

## **Typical Performance Curves** (Continued)

For Single-Channel Devices: 6N137M, HCPL2601M, HCPL2611M

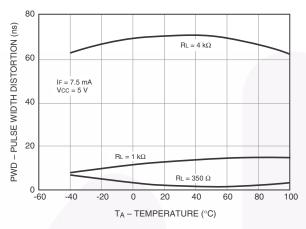

Figure 9. Pulse Width Distortion vs. Temperature

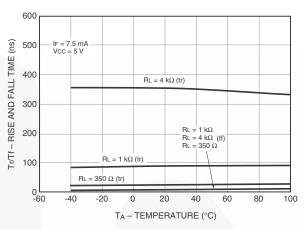

Figure 10. Rise and Fall Time vs. Temperature

Figure 11. Enable Propagation Delay vs. Temperature

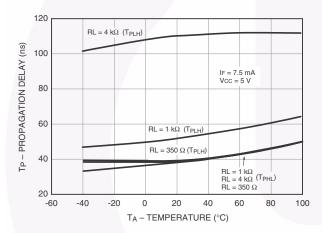

Figure 12. Switching Time vs. Temperature

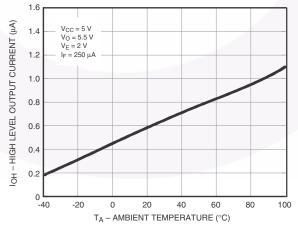

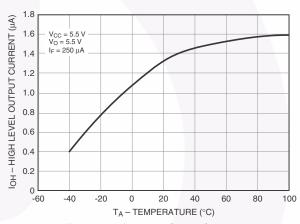

Figure 13. High Level Output Current vs. Temperature

## **Typical Performance Curves** (Continued)

For Dual-Channel Devices: HCPL2630M and HCPL2631M

$\label{eq:if-port} I_F - \text{FORWARD CURRENT (mA)}$  Figure 16. Switching Time vs. Forward Current

Figure 18. Input Threshold Current vs. Ambient Temperature

Figure 15. Input Diode Forward Voltage vs. Forward Current

Figure 17. Low Level Output Current vs. Ambient Temperature

Figure 19. Output Voltage vs. Input Forward Current

0 5

## **Typical Performance Curves** (Continued)

For Dual-Channel Devices: HCPL2630M and HCPL2631M

Figure 20. Pulse Width Distortion vs. Temperature

Figure 21. Rise and Fall Time vs. Temperature

Figure 22. Switching Time vs. Temperature

Figure 23. High Level Output Current vs.Temperature

### **Test Circuits**

Figure 24. Test Circuit and Waveforms for  $t_{\text{PLH}}$ ,  $t_{\text{PHL}}$ ,  $t_{\text{r}}$  and  $t_{\text{f}}$

Figure 25. Test Circuit  $t_{\text{EHL}}$  and  $t_{\text{ELH}}$

Figure 26. Test Circuit Common Mode Transient Immunity

CML

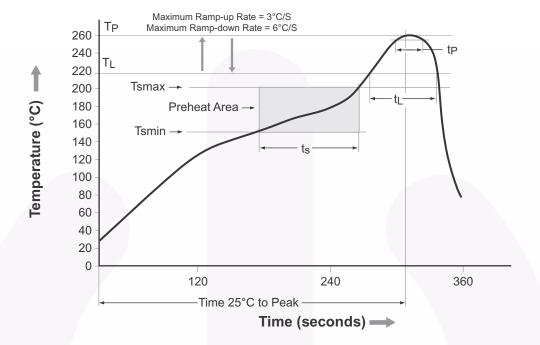

### **Reflow Profile**

| Profile Freature                                          | Pb-Free Assembly Profile |

|-----------------------------------------------------------|--------------------------|

| Temperature Min. (Tsmin)                                  | 150°C                    |

| Temperature Max. (Tsmax)                                  | 200°C                    |

| Time (t <sub>S</sub> ) from (Tsmin to Tsmax)              | 60 to 120 s              |

| Ramp-up Rate (t <sub>L</sub> to t <sub>P</sub> )          | 3°C/second maximum       |

| Liquidous Temperature (T <sub>L</sub> )                   | 217°C                    |

| Time (t <sub>L</sub> ) Maintained Above (T <sub>L</sub> ) | 60 to 150 s              |

| Peak Body Package Temperature                             | 260°C +0°C / -5°C        |

| Time (t <sub>P</sub> ) within 5°C of 260°C                | 30 s                     |

| Ramp-down Rate (T <sub>P</sub> to T <sub>L</sub> )        | 6°C/s maximum            |

| Time 25°C to Peak Temperature                             | 8 minutes maximum        |

Figure 27. Reflow Profile

## **Ordering Information**

| Part Number | Package                                                   | Packing Method                       |

|-------------|-----------------------------------------------------------|--------------------------------------|

| 6N137M      | DIP 8-Pin                                                 | Tube (50 units per tube)             |

| 6N137SM     | SMT 8-Pin (Lead Bend)                                     | Tube (50 units per tube)             |

| 6N137SDM    | SMT 8-Pin (Lead Bend)                                     | Tape and Reel (1,000 units per reel) |

| 6N137VM     | DIP 8-Pin, DIN EN/IEC 60747-5-5 Option                    | Tube (50 units per tube)             |

| 6N137SVM    | SMT 8-Pin (Lead Bend), DIN EN/IEC 60747-5-5 Option        | Tube (50 units per tube)             |

| 6N137SDVM   | SMT 8-Pin (Lead Bend), DIN EN/IEC 60747-5-5 Option        | Tape and Reel (1,000 units per reel) |

| 6N137TVM    | DIP 8-Pin, 0.4" Lead Spacing, DIN EN/IEC 60747-5-5 Option | Tube (50 units per tube)             |

| 6N137TSVM   | SMT 8-Pin, 0.4" Lead Spacing, DIN EN/IEC 60747-5-5 Option | Tube (50 units per tube)             |

| 6N137TSR2VM | SMT 8-Pin, 0.4" Lead Spacing, DIN EN/IEC 60747-5-5 Option | Tape and Reel (1,000 units per reel) |

#### Note:

The product orderable part number system listed in this table also applies to the HCPL2601M, HCPL2611M, HCPL2630M and HCPL2631M product families.

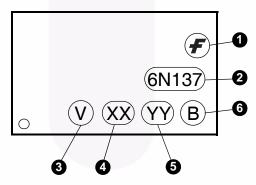

## **Marking Information**

Figure 28. Top Mark

| Defini | Definitions                                                                     |  |  |  |

|--------|---------------------------------------------------------------------------------|--|--|--|

| 1      | Fairchild Logo                                                                  |  |  |  |

| 2      | Device Number                                                                   |  |  |  |

| 3      | DIN EN/IEC60747-5-5 Option (only appears on component ordered with this option) |  |  |  |

| 4      | Two Digit Year Code, e.g., '16'                                                 |  |  |  |

| 5      | Two Digit Work Week Ranging from '01' to '53'                                   |  |  |  |

| 6      | Assembly Package Code                                                           |  |  |  |

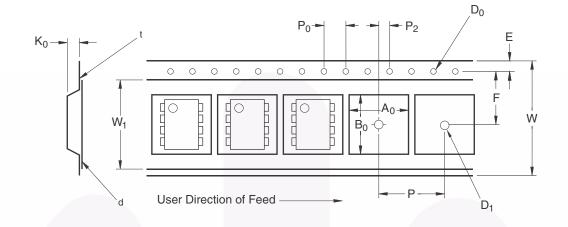

## **Carrier Tape Specifications (Option SD)**

| Symbol         | Description                        | Dimension in mm |

|----------------|------------------------------------|-----------------|

| W              | Tape Width                         | $16.0 \pm 0.3$  |

| t              | Tape Thickness                     | $0.30 \pm 0.05$ |

| P <sub>0</sub> | Sprocket Hole Pitch                | 4.0 ± 0.1       |

| D <sub>0</sub> | Sprocket Hole Diameter             | 1.55 ± 0.05     |

| Е              | Sprocket Hole Location             | 1.75 ± 0.10     |

| F              | Pocket Location                    | 7.5 ± 0.1       |

| P <sub>2</sub> |                                    | 2.0 ± 0.1       |

| Р              | Pocket Pitch                       | 12.0 ± 0.1      |

| A <sub>0</sub> | Pocket Dimensions                  | 10.30 ±0.20     |

| B <sub>0</sub> |                                    | 10.30 ±0.20     |

| K <sub>0</sub> |                                    | 4.90 ±0.20      |

| W <sub>1</sub> | Cover Tape Width                   | 13.2 ± 0.2      |

| d              | Cover Tape Thickness               | 0.1 Maximum     |

|                | Maximum Component Rotation or Tilt | 10°             |

| R              | Minimum Bending Radius             | 30              |

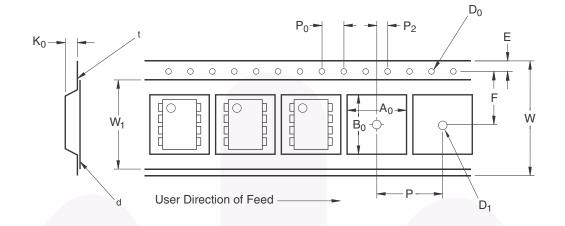

## **Carrier Tape Specifications (Option TSR2)**

| Symbol         | Description                        | Dimension in mm |

|----------------|------------------------------------|-----------------|

| W              | Tape Width                         | $24.0 \pm 0.3$  |

| t              | Tape Thickness                     | $0.40 \pm 0.1$  |

| P <sub>0</sub> | Sprocket Hole Pitch                | $4.0 \pm 0.1$   |

| D <sub>0</sub> | Sprocket Hole Diameter             | 1.55 ± 0.05     |

| Е              | Sprocket Hole Location             | 1.75 ± 0.10     |

| F              | Pocket Location                    | 11.5 ± 0.1      |

| P <sub>2</sub> |                                    | 2.0 ± 0.1       |

| Р              | Pocket Pitch                       | 16.0 ± 0.1      |

| A <sub>0</sub> | Pocket Dimensions                  | 12.80 ± 0.1     |

| B <sub>0</sub> |                                    | 10.35 ± 0.1     |

| K <sub>0</sub> |                                    | 5.7 ±0.1        |

| W <sub>1</sub> | Cover Tape Width                   | 21.0 ± 0.1      |

| d              | Cover Tape Thickness               | 0.1 Maximum     |

|                | Maximum Component Rotation or Tilt | 10°             |

| R              | Minimum Bending Radius             | 30              |

- A) NO STANDARD APPLIES TO THIS PACKAGE

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSION

- D) DWG FILENAME AND REVISION: MKT-N08Lrev2.

#### NOTES:

- A) NO STANDARD APPLIES TO THIS PACKAGE

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSION

- D) DRAWING FILENAME AND REVSION: MKT-N08Hrev7.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Fairchild Semiconductor:

HCPL2630SM HCPL2630SDM