## CY8CLED08

# EZ-Color™ HB LED Controller

## Features

- HB LED Controller

- Configurable Dimmers Support up to Eight Independent LED Channels

- 8 to 32 Bits of Resolution per Channel

- Dvnamic Reconfiguration Enables LED Controller Plus Other Features: CapSense, Battery Charging, and Motor Control

- Visual Embedded Design

- LED-Based Drivers

- Binning Compensation

- Temperature Feedback

- Optical Feedback

- DMX512

- PrISM Modulation Technology

- Reduces Radiated EMI

- Reduces Low Frequency Blinking

- Powerful Harvard Architecture Processor

- M8C Processor Speeds to 24 MHz

- 3.0 to 5.25V Operating Voltage

- Operating Voltages Down to 1.0V using On-Chip Switch Mode Pump (SMP)

- Industrial Temperature Range: -40°C to +85°C •

#### Flexible On-Chip Memory

- 16K Flash Program Storage 50,000 Erase/Write Cycles

- 256 bytes SRAM Data Storage

In-System Serial Programming (ISSP)

- Partial Flash Updates

- Flexible Protection Modes

- EEPROM Emulation in Flash

- Advanced Peripherals (PSoC<sup>®</sup> Blocks)

- Eight Digital PSoC Blocks Provide:

- · 8 to 32-Bit Timers, Counters, and PWMs ·

- Up to Two Full-Duplex UARTs

- Multiple SPI Masters or Slaves

- · Connectable to all GPIO pins

- 12 Rail-to-Rail Analog PSoC Blocks Provide:

- Up to 14-Bit ADCs

- Up to 9-Bit DACs

- Programmable Gain Amplifiers

- Programmable Filters and Comparators

- Complex peripherals by Combining Blocks

- Programmable Pin Configurations

- 25 mA Sink, 10 mA Source on all GPIO

- Pull Up, Pull Down, High Z, Strong, or Open Drain Drive Modes on all GPIO

- Up to 12 Analog Inputs on GPIO

- Four 30 mA Analog Outputs on GPIO

- Configurable interrupt on all GPIO

- Complete Development Tools

- Free Development Software

- PSoC Designer™

- Full Featured, In-Circuit Emulator and Programmer

- Full Speed Emulation

- Complex Breakpoint Structure

- 128 KBytes Trace Memory

## Logic Block Diagram

## CY8CLED08

## Contents

| 1. EZ-Color™ Functional Overview      |    |

|---------------------------------------|----|

| 1.1 Target Applications               |    |

| 1.2 The PSoC Core                     |    |

| 1.3 The Digital System                |    |

| 1.4 The Analog System                 | 5  |

| 1.1 Additional System Resources       | 6  |

| 1.2 EZ-Color Device Characteristics   |    |

| 2. Getting Started                    | 6  |

| 2.1 Development Kits                  | 6  |

| 2.2 Technical Training Modules        | 6  |

| 2.3 Consultants                       | 6  |

| 2.4 Technical Support                 | 6  |

| 2.5 Application Notes                 | 6  |

| 3. Development Tools                  | 7  |

| 3.1 PSoC Designer Software Subsystems | 7  |

| 3.2 In-Circuit Emulator               | 7  |

| 4. Document Conventions               | 8  |

| 4.1 Acronyms Used                     | 8  |

| 4.2 Units of Measure                  | 8  |

| 4.3 Numeric Naming                    | 8  |

| 5. Pin Information                    | 9  |

| 5.1 Pinouts                           | 9  |

| 6. Register Reference                 | 12 |

| 6.1 Register Conventions              | 12 |

| 6.2 Register Mapping Tables           |    |

|                                       |    |

| 7. Electrical Specifications                | 15 |

|---------------------------------------------|----|

| 7.1 Absolute Maximum Ratings                |    |

| 7.2 Operating Temperature                   |    |

| 7.3 DC Electrical Characteristics           |    |

| 7.4 AC Electrical Characteristics           |    |

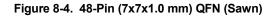

| 8. Packaging Information                    |    |

| 8.1 Packaging Dimensions                    |    |

| 8.1 Thermal Impedances                      |    |

| 8.2 Capacitance on Crystal Pins             |    |

| 8.3 Solder Reflow Peak Temperature          |    |

| 9. Development Tool Selection               |    |

| 9.1 Software Tools                          |    |

| 9.2 Hardware Tools                          | 39 |

| 9.3 Evaluation Tools                        |    |

| 9.4 Device Programmers                      |    |

| 9.5 Accessories (Emulation and Programming) | 41 |

| 9.6 Third Party Tools                       |    |

| 9.7 Build a PSoC Emulator into Your Board   | 41 |

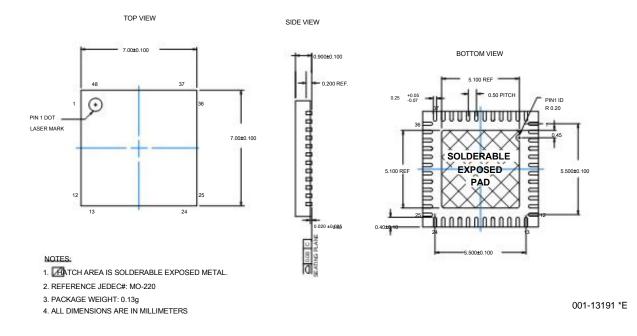

| 10. Ordering Information                    | 42 |

| 10.1 Key Device Features                    |    |

| 10.2 Ordering Code Definitions              |    |

| 11. Document History Page                   |    |

| 12. Sales, Solutions, and Legal Information |    |

| 12.1 Worldwide Sales and Design Support     |    |

| 12.2 Products                               |    |

## 1. EZ-Color<sup>™</sup> Functional Overview

Cypress' EZ-Color family of devices offers the ideal control solution for High Brightness LED applications requiring intelligent dimming control. EZ-Color devices combine the power and flexibility of PSoC (Programmable System-on-Chip). Cypress' PrISM (precise illumination signal modulation) modulation technology provides lighting designers a fully customizable and

technology provides lighting designers a fully customizable and integrated lighting solution platform.

The EZ-Color family supports a range of independent LED channels from 4 channels at 32 bits of resolution each, up to 16 channels at 8 bits of resolution each. This enables lighting designers the flexibility to choose the LED array size and color quality. PSoC Designer software, with lighting specific drivers, can significantly cut development time and simplify implementation of fixed color points through temperature, optical, and LED binning compensation. EZ-Color's virtually limitless analog and digital customization enable simple integration of features in addition to intelligent lighting, such as battery charging, image stabilization, and motor control during the development process. These features, along with Cypress' best-in-class quality and design support, make EZ-Color the ideal choice for intelligent HB LED control applications.

#### **1.1 Target Applications**

- LCD Backlight

- Large Signs

- General Lighting

- Architectural Lighting

- Camera/Cell Phone Flash

- Flashlights

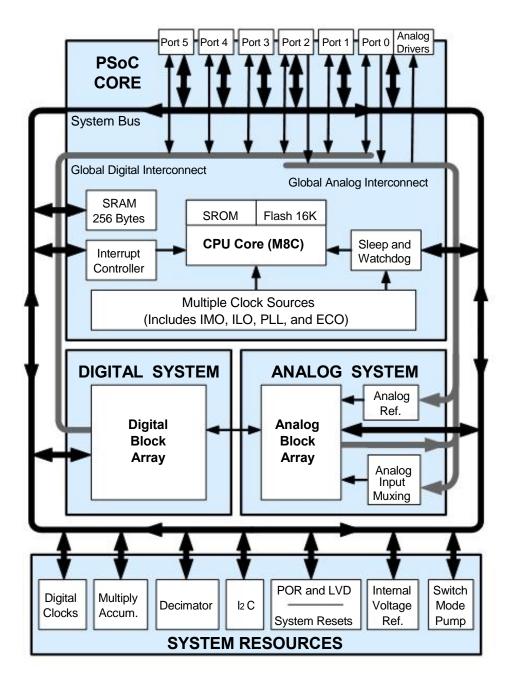

### 1.2 The PSoC Core

The PSoC Core is a powerful engine that supports a rich feature set. The core includes a CPU, memory, clocks, and configurable GPIO (General Purpose I/O).

The M8C CPU core is a powerful processor with speeds up to 48 MHz, providing a four MIPS 8-bit Harvard architecture microprocessor. The CPU uses an interrupt controller with 17 vectors, to simplify programming of real time embedded events. Program execution is timed and protected using the included Sleep and Watch Dog Timers (WDT).

Memory encompasses 16K of Flash for program storage, 256 bytes of SRAM for data storage, and up to 2K of EEPROM emulated using the Flash. Program Flash uses four protection levels on blocks of 64 bytes, allowing customized software IP protection.

The EZ-Color family incorporates flexible internal clock generators, including a 24 MHz IMO (internal main oscillator) accurate to 2.5% over temperature and voltage. The 24 MHz IMO can also be doubled to 48 MHz for use by the digital system. A low power 32 kHz ILO (internal low speed oscillator) is provided for the Sleep timer and WDT. If crystal accuracy is desired, the ECO (32.768 kHz external crystal oscillator) is available for use as a Real Time Clock (RTC) and can optionally generate a

crystal-accurate 24 MHz system clock using a PLL. The clocks, together with programmable clock dividers (as a System

Resource), provide the flexibility to integrate almost any timing requirement into the EZ-Color device.

EZ-Color GPIOs provide connection to the CPU, digital and analog resources of the device. Each pin's drive mode may be selected from eight options, allowing great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

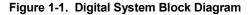

### 1.3 The Digital System

The Digital System is composed of 8 digital blocks. Each block is an 8-bit resource that can be used alone or combined with other blocks to form 8, 16, 24, and 32-bit peripherals, which are called user module references.

Digital peripheral configurations include the following:

PrISM (8 to 32 bit)

- PWMs (8 to 32 bit)

- PWMs with Dead band (8 to 32 bit)

- Counters (8 to 32 bit)

- Timers (8 to 32 bit)

- UART 8 bit with selectable parity (up to 2)

- SPI slave and master (up to 2)

- I2C slave and multi-master (1 available as a System Resource) -

Cyclical Redundancy Checker/Generator (8 to 32 bit)

- IrDA (up to 2)

- Generators (8 to 32 bit)

The digital blocks can be connected to any GPIO through a series of global buses that can route any signal to any pin. The buses also enable signal multiplexing and for performing logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

Digital blocks are provided in rows of four, where the number of blocks varies by EZ-Color device family. This allows you the optimum choice of system resources for your application. Family resources are shown in the table titled EZ-Color Device Characteristics.

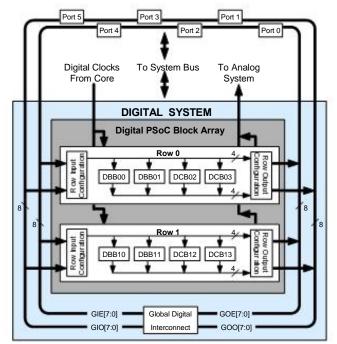

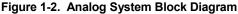

#### 1.4 The Analog System

The analog system is composed of 12 configurable blocks, each comprised of an opamp circuit allowing the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common EZ-Color analog functions (most available as user modules) are as follows:

- Analog-to-digital converters (up to 4, with 6- to 14-bit resolution, selectable as Incremental, Delta Sigma, and SAR)

- Filters (2, 4, 6, and 8 pole band-pass, low-pass, and notch)

Amplifiers (up to 4, with selectable gain to 48x)

Instrumentation amplifiers (up to 2, with selectable gain to 93x) =

Comparators (up to 4, with 16 selectable thresholds)

- DACs (up to 4, with 6- to 9-bit resolution)

- Multiplying DACs (up to 4, with 6- to 9-bit resolution)

- High current output drivers (four with 30 mA drive as a Core Resource)

- 1.3V reference (as a System Resource)

- DTMF Dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analog blocks are provided in columns of three, which includes one CT (Continuous Time) and two SC (Switched Capacitor) blocks, as shown in the figure below.

#### 1.1 Additional System Resources

System Resources, some of which have been previously listed, provide additional capability useful to complete systems. Additional resources include a multiplier, decimator, switch mode pump, low voltage detection, and power on reset. Statements describing the merits of each system resource are below.

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks can be routed to both the digital and analog systems. Additional clocks can be generated using digital blocks as clock dividers.

- Multiply accumulate (MAC) provides fast 8-bit multiplier with 32-bit accumulate, to assist in general math and digital filters.

- The decimator provides a custom hardware filter for digital signal processing applications including the creation of Delta Sigma ADCs.

- The I2C module provides 100 and 400 kHz communication over two wires. Slave, master, and multi-master modes are all supported.

- Low Voltage Detection (LVD) interrupts can signal the application of falling voltage levels, while the advanced POR (Power On Reset) circuit eliminates the need for a system supervisor.

- An internal 1.3V reference provides an absolute reference for the analog system, including ADCs and DACs.

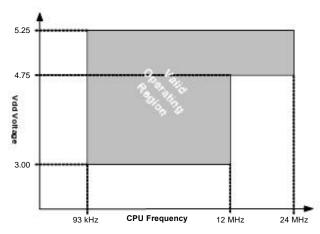

- An integrated switch mode pump (SMP) generates normal operating voltages from a single 1.2V battery cell, providing a low cost boost converter.

#### 1.2 EZ-Color Device Characteristics

Depending on your EZ-Color device characteristics, the digital and analog systems can have 16, 8, or 4 digital blocks and 12, 6, or 4 analog blocks. The following table lists the resources available for specific EZ-Color device groups. The device covered by this data sheet is shown in the highlighted row of the table

Table 1-1. EZ-Color Device Characteristics

| Part Number | LED<br>Channels | Digital<br>I/O | Di gi tal<br>Rows | Digital<br>Blocks | Analog<br>Inputs | Analog<br>Outputs | Analog<br>Columns | Analog<br>Blocks | SRA M<br>Size | Flash<br>Size | CapSense |

|-------------|-----------------|----------------|-------------------|-------------------|------------------|-------------------|-------------------|------------------|---------------|---------------|----------|

| CY8CLED02   | 2               | 16             | 1                 | 4                 | 8                | 0                 | 2                 | 4                | 256 Bytes     | 4K            | No       |

| CY8CLED04   | 4               | 56             | 1                 | 4                 | 48               | 2                 | 2                 | 6                | 1K            | 16K           | Yes      |

| CY8CLED08   | 8               | 44             | 2                 | 8                 | 12               | 4                 | 4                 | 12               | 256 Bytes     | 16K           | No       |

| CY8CLED16   | 16              | 44             | 4                 | 16                | 12               | 4                 | 4                 | 12               | 2K            | 32K           | No       |

## 2. Getting Started

The quickest path to understanding the EZ-Color silicon is by reading this data sheet and using the PSoC Designer Integrated Development Environment (IDE). This data sheet is an overview of the EZ-Color integrated circuit and presents specific pin, register, and electrical specifications.

For up-to-date Ordering, Packaging, and Electrical Specification information, reference the latest device data sheets on the web at http://www.cypress.com/ez-color.

### 2.1 Development Kits

Development Kits are available from the following distributors: Digi-Key, Avnet, Arrow, and Future. The Cypress Online Store contains development kits, **C** compilers, and all accessories for PSoC development. Go to the Cypress Online Store web site at http://www.cypress.com/store, click Lighting & Power Control to view a current list of available items.

## 2.2 Technical Training Modules

Free PSoC technical training modules are available for users new to PSoC. Training modules cover designing, debugging, advanced analog and CapSense. Go to http://www.cypress.com/techtrain.

### 2.3 Consultants

Certified PSoC Consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC Consultant go to http://www.cypress.com, click on Design Support located at the center of the web page, and select CYPros Consultants.

### 2.4 Technical Support

Application engineers take pride in fast and accurate response. They can be reached with a 4-hour guaranteed response at http://www.cypress.com/support.

#### 2.5 Application Notes

A long list of application notes will assist you in every aspect of your design effort. To view the application notes, go to the http://www.cypress.com web site and select Application Notes under the Documentation tab.

## 3. Development Tools

PSoC Designer is a Microsoft<sup>®</sup> Windows-based, integrated development environment for the Programmable System-on-Chip (PSoC) devices. The PSoC Designer IDE runs on Windows XP or Windows Vista.

This system provides design database management by project, an integrated debugger with In-Circuit Emulator, in-system programming support, and built-in support for third-party assemblers and C compilers.

PSoC Designer also supports C language compilers developed specifically for the devices in the PSoC family.

### 3.1 PSoC Designer Software Subsystems

#### 3.1.1 System-Level View

A drag-and-drop visual embedded system design environment based on PSoC Designer. In the system level view you create a model of your system inputs, outputs, and communication interfaces. You define when and how an output device changes state based upon any or all other system devices. Based upon the design, PSoC Designer automatically selects one or more PSoC Mixed-Signal Controllers that match your system requirements. PSoC Designer generates all embedded code, then compiles and links it into a programming file for a specific PSoC device.

#### 3.1.2 Chip-Level View

The chip-level view is a more traditional Integrated Development Environment (IDE) based on PSoC Designer. Choose a base device to work with and then select different onboard analog and digital components called user modules that use the PSoC blocks. Examples of user modules are ADCs, DACs, Amplifiers, and Filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The device editor also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic configuration allows for changing configurations at run time.

#### 3.1.3 Hybrid Designs

You can begin in the system-level view, allow it to choose and configure your user modules, routing, and generate code, then switch to the chip-level view to gain complete control over on-chip resources. All views of the project share a common code editor, builder, and common debug, emulation, and programming tools.

#### 3.1.4 Code Generation Tools

PSoC Designer supports multiple third party C compilers and assemblers. The code generation tools work seamlessly within the PSoC Designer interface and have been tested with a full range of debugging tools. The choice is yours.

**Assemblers.** The assemblers allow assembly code to merge seamlessly with C code. Link libraries automatically use absolute addressing or are compiled in relative mode, and linked with other software modules to get absolute addressing.

**C Language Compilers.** C language compilers are available that support the PSoC family of devices. The products allow you to create complete C programs for the PSoC family devices. The optimizing C compilers provide all the features of C tailored to the PSoC architecture. They come complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### 3.1.5 Debugger

The PSoC Designer Debugger subsystem provides hardware in-circuit emulation, allowing you to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow the designer to read and program and read and write data memory, read and write I/O registers, read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The debugger also allows the designer to create a trace buffer of registers and memory locations of interest.

#### 3.1.6 Online Help System

The online help system displays online, context-sensitive help for the user. Designed for procedural and quick reference, each functional subsystem has its own context-sensitive help. This system also provides tutorials and links to FAQs and an Online Support Forum to aid the designer in getting started.

#### 3.2 In-Circuit Emulator

A low cost, high functionality In-Circuit Emulator (ICE) is available for development support. This hardware has the capability to program single devices.

The emulator consists of a base unit that connects to the PC by way of a USB port. The base unit is universal and operates with all PSoC devices. Emulation pods for each device family are available separately. The emulation pod takes the place of the PSoC device in the target board and performs full speed (24 MHz) operation.

## 4. Document Conventions

## 4.1 Acronyms Used

The following table lists the acronyms that are used in this document.

| Acronym | Description                                         |

|---------|-----------------------------------------------------|

| AC      | alternating current                                 |

| ADC     | analog-to-digital converter                         |

| API     | application programming interface                   |

| CPU     | central processing unit                             |

| СТ      | continuous time                                     |

| DAC     | digital-to-analog converter                         |

| DC      | direct current                                      |

| ECO     | external crystal oscillator                         |

| EEPROM  | electrically erasable programmable read-only memory |

| FSR     | full scale range                                    |

| GPIO    | general purpose I/O                                 |

| GUI     | graphical user interface                            |

| HBM     | human body model                                    |

| ICE     | in-circuit emulator                                 |

| ILO     | internal low speed oscillator                       |

| IMO     | internal main oscillator                            |

| I/O     | input/output                                        |

| IPOR    | imprecise power on reset                            |

| LSb     | least-significant bit                               |

| LVD     | low voltage detect                                  |

| MSb     | most-significant bit                                |

| PC      | program counter                                     |

| PLL     | phase-locked loop                                   |

| POR     | power on reset                                      |

| PPOR    | precision power on reset                            |

| PSoC®   | Programmable System-on-Chip                         |

| PWM     | pulse width modulator                               |

| SC      | switched capacitor                                  |

| SLIMO   | slow IMO                                            |

| SMP     | switch mode pump                                    |

| SRAM    | static random access memory                         |

#### 4.2 Units of Measure

A units of measure table is located in the Electrical Specifications section. Table 7-1 on page 15 lists all the abbreviations used to measure the devices.

### 4.3 Numeric Naming

Hexadecimal numbers are represented with all letters in uppercase with an appended lowercase 'h' (for example, '14h' or '3Ah'). Hexadecimal numbers may also be represented by a '0x' prefix, the C coding convention. Binary numbers have an appended lowercase 'b' (for example, 01010100b' or '01000011b'). Numbers not indicated by an 'h' or 'b' are decimal.

## 5. Pin Information

### 5.1 Pinouts

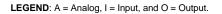

5.1.1 48-Pin Part Pinout SSOP

#### Table 5-1. 48-Pin Part Pinout (SSOP)

| Pin | Ту      | /pe     | Pin   |                                                                            | 1          |          | F                          | iaure 5                  | -1. 48-Pin Device                                                    |

|-----|---------|---------|-------|----------------------------------------------------------------------------|------------|----------|----------------------------|--------------------------|----------------------------------------------------------------------|

| No. | Digital | Analog  | Name  | Description                                                                |            |          |                            |                          |                                                                      |

| 1   | I/O     | 3 I -   | P0[7] | Analog column mux input.                                                   |            |          |                            | 1000                     |                                                                      |

| 2   | I/O     | I/O     | P0[5] | Analog column mux input and column output.                                 |            |          | A, I, P0[7]                | = <sup>0</sup> 1         | 48 🖕 Vdd                                                             |

| 3   | I/O     | I/O     | P0[3] | Analog column mux input and column output.                                 |            | А,       | IO, P0[5]                  | = 2                      | 47 🗖 P0[6], A, I                                                     |

| 4   | I/O     | 3       | P0[1] | Analog column mux input.                                                   |            |          | , IO, P0[3]                |                          | 46 🗖 P0[4], A, IO                                                    |

| 5   | I/O     |         | P2[7] |                                                                            |            |          | A, I, P0[1]                |                          | 45 📼 P0[2], A, IO                                                    |

| 6   | I/O     |         | P2[5] |                                                                            |            |          |                            | <b>5</b>                 | 44 <b>P</b> 0[0], A, I                                               |

| 7   | I/O     |         | P2[3] | Direct switched capacitor block input.                                     |            |          | P2[5]<br>A, I, P2[3]       |                          | 43 <b>=</b> P2[6], External VRef<br>42 <b>=</b> P2[4], External AGND |

| 8   | I/O     | 3 I     | P2[1] | Direct switched capacitor block input.                                     |            |          | A, I, P2[3]<br>A, I, P2[1] |                          | 41 P2[4], External AGND<br>41 P2[2], A, I                            |

| 9   | I/O     | 2       | P4[7] |                                                                            |            |          |                            | 9                        | 40 <b>P</b> 2[0], A, I                                               |

| 10  | I/O     |         | P4[5] |                                                                            |            |          | P4[5]                      | <b>=</b> 10              | 39 <b>–</b> P4[6]                                                    |

| 11  | I/O     |         | P4[3] |                                                                            |            |          |                            | <b>a</b> 11              | 38 <b>–</b> P4[4]                                                    |

| 12  | I/O     | <u></u> | P4[1] |                                                                            | 1          |          |                            | <b>a</b> 12              | SSOP 37 P4[2]                                                        |

| 13  | Po      | wer     | SMP   | Switch Mode Pump (SMP) connection to external components required.         |            |          |                            | <b>1</b> 3<br><b>1</b> 4 | 36 P P4[0]<br>35 XRES                                                |

| 14  | I/O     |         | P3[7] |                                                                            |            |          |                            | <b>a</b> 15              | 34 <b>–</b> P3[6]                                                    |

| 15  | I/O     |         | P3[5] |                                                                            |            |          |                            | <b>1</b> 6               | 33 <b>–</b> P3[4]                                                    |

| 16  | I/O     | 8       | P3[3] |                                                                            |            |          |                            | <b>1</b> 7               | 32 P3[2]                                                             |

| 17  | I/O     | 2       | P3[1] |                                                                            |            |          |                            | <b>18</b> 19             | 31 – P3[0]<br>30 – P5[2]                                             |

| 18  | I/O     |         | P5[3] |                                                                            | 1          | 12C S    | CL, P1[7]                  |                          | 29 <b>P</b> 5[0]                                                     |

| 19  | I/O     |         | P5[1] |                                                                            | 1          | I2C SI   | DA, P1[5]                  | <b>2</b> 1               | 28 <b>P</b> 1[6]                                                     |

| 20  | I/O     | 3       | P1[7] | I2C Serial Clock (SCL).                                                    | 1          |          | P1[3]                      | = 22                     | 27 P1[4], EXTCLK                                                     |

| 21  | I/O     |         | P1[5] | I2C Serial Data (SDA).                                                     | 12C S      | SCL, XTA | Lin, P1[1]                 |                          | 26 <b>–</b> P1[2]                                                    |

| 22  | I/O     |         | P1[3] |                                                                            | 1          |          | Vss                        | <b>a</b> 24              | 25 - P1[0], XTALout, I2C SDA                                         |

| 23  | I/O     |         | P1[1] | Crystal Input (XTALin), I2C Serial Clock (SCL), ISSP SCLK <sup>[1]</sup> . |            |          |                            |                          |                                                                      |

| 24  | Po      | wer     | Vss   | Ground connection.                                                         |            |          |                            |                          |                                                                      |

| 25  | I/O     | ĵ.      | P1[0] | Crystal Output (XTALout), I2C Serial Data (SDA), ISSP SDATA <sup>[1]</sup> |            |          |                            |                          |                                                                      |

| 26  | I/O     |         | P1[2] |                                                                            |            |          |                            |                          |                                                                      |

| 27  | I/O     |         | P1[4] | Optional External Clock Input (EXTCLK).                                    | Pin<br>No. | Digital  | Analog                     | Pin<br>Name              | Description                                                          |

| 28  | I/O     | 1       | P1[6] |                                                                            | 39         | I/O      |                            | P4[6]                    |                                                                      |

| 29  | I/O     | 1       | P5[0] |                                                                            | 39         | I/O      | 6                          | P4[6]                    | 8                                                                    |

| 30  | I/O     |         | P5[2] |                                                                            | 40         | I/O      | . I .                      | P2[0]                    | Direct switched capacitor block input.                               |

| 31  | I/O     |         | P3[0] |                                                                            | 41         | I/O      | 1                          | P2[2]                    | Direct switched capacitor block input.                               |

| 32  | I/O     | 3       | P3[2] |                                                                            | 42         | I/O      | 3                          | P2[4]                    | External Analog Ground (AGND).                                       |

| 33  | I/O     | 3       | P3[4] |                                                                            | 43         | I/O      | -                          | P2[6]                    | External Voltage Reference (VRef).                                   |

| 34  | I/O     |         | P3[6] |                                                                            | 44         | I/O      | <u> </u>                   | P0[0]                    | Analog column mux input.                                             |

| 35  |         | out     | XRES  | Active high external reset with internal pull down.                        | 45         | I/O      | I/O                        | P0[2]                    | Analog column mux input and column output.                           |

| 36  | I/O     |         | P4[0] |                                                                            | 46         | I/O      | I/O                        | P0[4]                    | Analog column mux input and column output.                           |

| 37  | I/O     | 1       | P4[2] |                                                                            | 47         | I/O      |                            | P0[6]                    | Analog column mux input.                                             |

| 38  | I/O     |         | P4[4] |                                                                            | 48         | Po       | wer                        | Vdd                      | Supply voltage.                                                      |

**LEGEND**: A = Analog, I = Input, and O = Output.

#### Note

1. These are the ISSP pins, which are not High Z at POR.

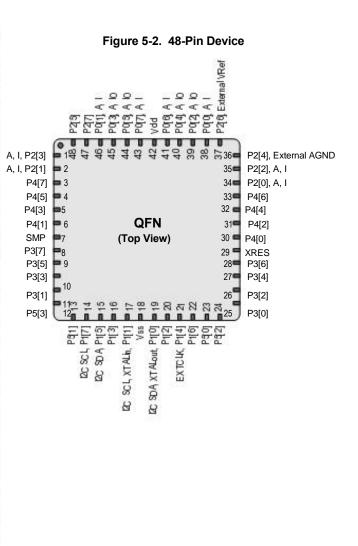

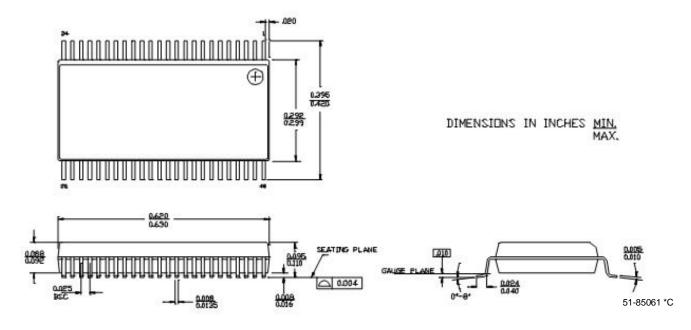

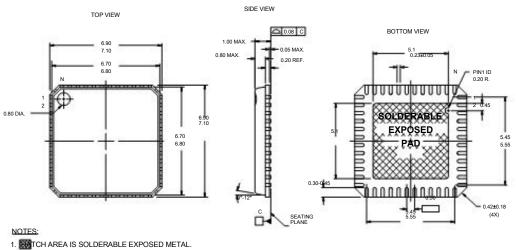

## 5.1.2 48-Pin Part Pinout QFN

| Table 5-2. | 48-Pin | Part | Pinout | (QFN) <sup>[2]</sup> |

|------------|--------|------|--------|----------------------|

|            |        |      | 1 mout | (~)                  |

|            | <u>а</u> т. |                | Pin          |                                                                              |

|------------|-------------|----------------|--------------|------------------------------------------------------------------------------|

| Pin<br>No. |             | pe<br>Analog   | Pin<br>Name  | Description                                                                  |

| 1          | Digital     | Analog         | P2[3]        | Direct switched capacitor block input.                                       |

| 2          | 1/O         | 6 I 8          | P2[1]        | Direct switched capacitor block input.                                       |

| 3          | 1/O         |                | P4[7]        | Direct Switched Capacitor block input.                                       |

| 4          | 1/O         |                | P4[5]        |                                                                              |

| 4<br>5     | 1/O         |                |              |                                                                              |

| -          | 1/0         |                | P4[3]        |                                                                              |

| 6<br>7     |             | wer            | P4[1]<br>SMP | Switch Made Dump (SMD) connection to external                                |

| <i>'</i>   | FU          |                | Sivir        | Switch Mode Pump (SMP) connection to external<br>components required.        |

| 8          | I/O         |                | P3[7]        |                                                                              |

| 9          | I/O         | S              | P3[5]        |                                                                              |

| 10         | I/O         |                | P3[3]        |                                                                              |

| 11         | I/O         |                | P3[1]        |                                                                              |

| 12         | I/O         | 8 3            | P5[3]        |                                                                              |

| 13         | I/O         | <u>i - i</u>   | P5[1]        |                                                                              |

| 14         | I/O         |                | P1[7]        | I2C Serial Clock (SCL).                                                      |

| 15         | I/O         | ĭ – ĭ          | P1[5]        | I2C Serial Data (SDA).                                                       |

| 16         | I/O         |                | P1[3]        |                                                                              |

| 17         | I/O         |                | P1[1]        | Crystal Input (XTALin), I2C Serial Clock (SCL),<br>ISSP-SCLK <sup>11</sup> . |

| 18         | Pov         | wer            | Vss          | Ground connection.                                                           |

| 19         | I/O         |                | P1[0]        | Crystal Output (XTALout), I2C Serial Data (SDA), ISSP-SDATA <sup>[1]</sup> . |

| 20         | I/O         |                | P1[2]        |                                                                              |

| 21         | I/O         |                | P1[4]        | Optional External Clock Input (EXTCLK).                                      |

| 22         | I/O         |                | P1[6]        |                                                                              |

| 23         | I/O         | 8              | P5[0]        |                                                                              |

| 24         | I/O         | S - S          | P5[2]        |                                                                              |

| 25         | I/O         |                | P3[0]        |                                                                              |

| 26         | I/O         |                | P3[2]        |                                                                              |

| 27         | I/O         | 8              | P3[4]        |                                                                              |

| 28         | I/O         |                | P3[6]        |                                                                              |

| 29         | Inp         | out            | XRES         | Active high external reset with internal pull down.                          |

| 30         | I/O         | 3 3 i          | P4[0]        |                                                                              |

| 31         | I/O         |                | P4[2]        |                                                                              |

| 32         | I/O         |                | P4[4]        |                                                                              |

| 33         | I/O         | 33             | P4[6]        |                                                                              |

| 34         | I/O         | 8 <b>-1</b> -8 | P2[0]        | Direct switched capacitor block input.                                       |

| 35         | I/O         | 1              | P2[2]        | Direct switched capacitor block input.                                       |

| 36         | I/O         | й — й          | P2[4]        | External Analog Ground (AGND).                                               |

| 37         | I/O         |                | P2[6]        | External Voltage Reference (VRef).                                           |

| 38         | I/O         |                | P0[0]        | Analog column mux input.                                                     |

| 39         | I/O         | I/O            | P0[2]        | Analog column mux input and column output.                                   |

| 40         | I/O         | I/O            | P0[4]        | Analog column mux input and column output.                                   |

| 41         | I/O         | 5 I 5          | P0[6]        | Analog column mux input.                                                     |

| 42         | Pov         |                | Vdd          | Supply voltage.                                                              |

| 43         | I/O         | S I S          | P0[7]        | Analog column mux input.                                                     |

| 44         | I/O         | I/O            | P0[5]        | Analog column mux input and column output.                                   |

| 45         | I/O         | I/O            | P0[3]        | Analog column mux input and column output.                                   |

| 46         | I/O         | 1              | P0[1]        | Analog column mux input.                                                     |

| 47         | 1/O         |                | P2[7]        |                                                                              |

| 48         | 1/O         |                | P2[5]        |                                                                              |

|            |             | nalog I –      |              |                                                                              |

LEGEND: A = Analog, I = Input, and O = Output. Note

The center pad on the QFN package should be connected to ground (Vss) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal.

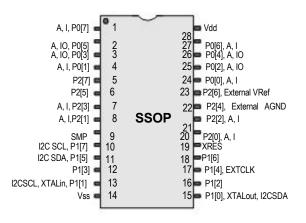

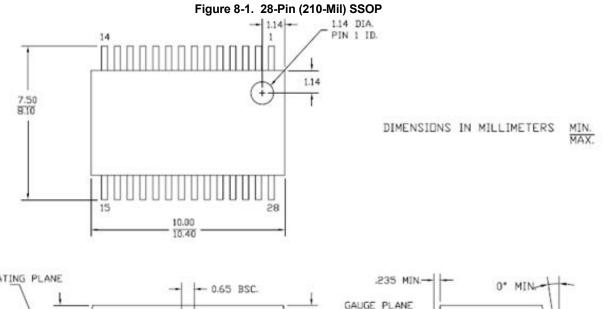

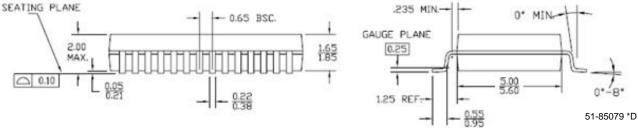

## 5.0.1 28-Pin Part Pinout

#### Table 5-3. 28-Pin Part Pinout (SSOP)

| Pin<br>No. | Ty<br>Digital | pe<br>Analog                                   | Pin<br>Name | Description                                                                  |

|------------|---------------|------------------------------------------------|-------------|------------------------------------------------------------------------------|

| 1          | I/O           | L I                                            | P0[7]       | Analog column mux input.                                                     |

| 2          | I/O           | I/O                                            | P0[5]       | Analog column mux input and column output.                                   |

| 3          | I/O           | I/O                                            | P0[3]       | Analog column mux input and column output.                                   |

| 4          | I/O           | 8 I S                                          | P0[1]       | Analog column mux input.                                                     |

| 5          | I/O           |                                                | P2[7]       |                                                                              |

| 6          | I/O           |                                                | P2[5]       |                                                                              |

| 7          | I/O           | 8_ <b>1</b> _8                                 | P2[3]       | Direct switched capacitor block input.                                       |

| 8          | I/O           | I                                              | P2[1]       | Direct switched capacitor block input.                                       |

| 9          | Po            | wer                                            | SMP         | Switch Mode Pump (SMP) connection to<br>external components required.        |

| 10         | I/O           | Ĩ. Î.                                          | P1[7]       | I2C Serial Clock (SCL).                                                      |

| 11         | I/O           | 8 8                                            | P1[5]       | I2C Serial Data (SDA).                                                       |

| 12         | I/O           | 8 - N                                          | P1[3]       |                                                                              |

| 13         | I/O           |                                                | P1[1]       | Crystal Input (XTALin), I2C Serial Clock (SCL), ISSP-SCLK <sup>[1]</sup> .   |

| 14         | Po            | wer                                            | Vss         | Ground connection.                                                           |

| 15         | I/O           | ×                                              | P1[0]       | Crystal Output (XTALout), I2C Serial Data (SDA), ISSP-SDATA <sup>[1]</sup> . |

| 16         | I/O           | 9 - A                                          | P1[2]       | 8                                                                            |

| 17         | I/O           |                                                | P1[4]       | Optional External Clock Input (EXTCLK).                                      |

| 18         | I/O           |                                                | P1[6]       |                                                                              |

| 19         | Ing           | out                                            | XRES        | Active high external reset with internal pull down.                          |

| 20         | I/O           | 8 I 3                                          | P2[0]       | Direct switched capacitor block input.                                       |

| 21         | I/O           | . I.,                                          | P2[2]       | Direct switched capacitor block input.                                       |

| 22         | I/O           | 1. 1                                           | P2[4]       | External Analog Ground (AGND).                                               |

| 23         | I/O           | с.<br>С. С. С | P2[6]       | External Voltage Reference (VRef).                                           |

| 24         | I/O           | 8 - k                                          | P0[0]       | Analog column mux input.                                                     |

| 25         | I/O           | I/O                                            | P0[2]       | Analog column mux input and column output.                                   |

| 26         | I/O           | I/O                                            | P0[4]       | Analog column mux input and column output.                                   |

| 27         | I/O           | 8-1-8                                          | P0[6]       | Analog column mux input.                                                     |

| 28         | Po            | wer                                            | Vdd         | Supply voltage.                                                              |

## CY8CLED08

## Figure 5-3. 28-Pin Device

## 6. Register Reference

This chapter lists the registers of the CY8CLED08 EZ-Color device.

### 6.1 Register Conventions

The register conventions specific to this section are listed in the following table. Register Mapping Tables

| Convention | Description                  |

|------------|------------------------------|

| R          | Read register or bit(s)      |

| W          | Write register or bit(s)     |

| L          | Logical register or bit(s)   |

| С          | Clearable register or bit(s) |

| #          | Access is bit specific       |

### 6.2 Register Mapping Tables

The device has a total register address space of 512 bytes. The register space is referred to as I/O space and is divided into two banks. The XOI bit in the Flag register (CPU\_F) determines which bank the user is currently in. When the XOI bit is set the user is in Bank 1.

Note In the following register mapping tables, blank fields are reserved and should not be accessed.

#### Table 6-1. Register Map Bank 0 Table: User Space

|          | Register ma  | J Dalik | o Table. O | ser opace    |        |          |              |        | _        | 2            |          |

|----------|--------------|---------|------------|--------------|--------|----------|--------------|--------|----------|--------------|----------|

| Name     | Addr (0,Hex) | Access  | Name       | Addr (0,Hex) | Access | Name     | Addr (0,Hex) | Access | Name     | Addr (0,Hex) | Access   |

| PRT0DR   | 00           | RW      | S          | 40           |        | ASC10CR0 | 80           | RW     |          | C0           | 2        |

| PRT0IE   | 01           | RW      |            | 41           |        | ASC10CR1 | 81           | RW     |          | C1           |          |

| PRT0GS   | 02           | RW      |            | 42           |        | ASC10CR2 | 82           | RW     |          | C2           | 3        |

| PRT0DM2  | 03           | RW      |            | 43           |        | ASC10CR3 | 83           | RW     |          | C3           |          |

| PRT1DR   | 04           | RW      | 8          | 44           |        | ASD11CR0 | 84           | RW     |          | C4           |          |

| PRT1IE   | 05           | RW      | 8          | 45           |        | ASD11CR1 | 85           | RW     |          | C5           |          |

| PRT1GS   | 06           | RW      | 8          | 46           |        | ASD11CR2 | 86           | RW     |          | C6           | 1        |

| PRT1DM2  | 07           | RW      | 8<br>1     | 47           |        | ASD11CR3 | 87           | RW     |          | C7           |          |

| PRT2DR   | 08           | RW      | 8          | 48           | 0      | ASC12CR0 | 88           | RW     |          | C8           | 2        |

| PRT2IE   | 09           | RW      | 8          | 49           |        | ASC12CR1 | 89           | RW     |          | C9           |          |

| PRT2GS   | 0A           | RW      | S          | 4A           |        | ASC12CR2 | 8A           | RW     |          | CA           |          |

| PRT2DM2  | 0B           | RW      | 2          | 4B           |        | ASC12CR3 | 8B           | RW     |          | СВ           |          |

| PRT3DR   | 0C           | RW      | 1          | 4C           |        | ASD13CR0 | 8C           | RW     |          | CC           |          |

| PRT3IE   | 0D           | RW      | 8          | 4D           |        | ASD13CR1 | 8D           | RW     |          | CD           |          |

| PRT3GS   | 0E           | RW      |            | 4E           |        | ASD13CR2 | 8E           | RW     |          | CE           |          |

| PRT3DM2  | 0F           | RW      | 3          | 4F           |        | ASD13CR3 | 8F           | RW     |          | CF           |          |

| PRT4DR   | 10           | RW      |            | 50           |        | ASD20CR0 | 90           | RW     |          | D0           |          |

| PRT4IE   | 11           | RW      | 2          | 51           |        | ASD20CR1 | 91           | RW     |          | D1           |          |

| PRT4GS   | 12           | RW      |            | 52           |        | ASD20CR2 | 92           | RW     |          | D2           |          |

| PRT4DM2  | 13           | RW      | S          | 53           |        | ASD20CR3 | 93           | RW     |          | D3           |          |

| PRT5DR   | 14           | RW      |            | 54           |        | ASC21CR0 | 94           | RW     |          | D4           | <u> </u> |

| PRT5IE   | 15           | RW      | 8 8        | 55           |        | ASC21CR1 | 95           | RW     |          | D5           |          |

| PRT5GS   | 16           | RW      |            | 56           |        | ASC21CR2 | 96           | RW     | I2C_CFG  | D6           | RW       |

| PRT5DM2  | 17           | RW      | 2          | 57           |        | ASC21CR3 | 97           | RW     | I2C_SCR  | D7           | #        |

|          | 18           |         |            | 58           |        | ASD22CR0 | 98           | RW     | I2C_DR   | D8           | RW       |

| £        | 19           | a (1)   | 2          | 59           |        | ASD22CR1 | 99           | RW     | I2C_MSCR | D9           | #        |

|          | 1A           |         |            | 5A           |        | ASD22CR2 | 9A           | RW     | INT_CLR0 | DA           | RW       |

|          | 1B           |         | 2          | 5B           |        | ASD22CR3 | 9B           | RW     | INT_CLR1 | DB           | RW       |

|          | 1C           |         | 2          | 5C           |        | ASC23CR0 | 9C           | RW     |          | DC           |          |

| 1        | 1D           |         | 3 3        | 5D           |        | ASC23CR1 | 9D           | RW     | INT_CLR3 | DD           | RW       |

| 5        | 1E           |         | 2          | 5E           |        | ASC23CR2 | 9E           | RW     | INT_MSK3 | DE           | RW       |

| 8        | 1F           | 2       | ¢          | 5F           |        | ASC23CR3 | 9F           | RW     |          | DF           |          |

| DBB00DR0 | 20           | #       | AMX_IN     | 60           | RW     |          | A0           |        | INT_MSK0 | E0           | RW       |

| DBB00DR1 | 21           | W       |            | 61           |        |          | A1           |        | INT_MSK1 | E1           | RW       |

| DBB00DR2 | 22           | RW      | 3          | 62           |        |          | A2           |        | INT_VC   | E2           | RC       |

| DBB00CR0 | 23           | #       | ARF_CR     | 63           | RW     |          | A3           |        | RES_WDT  | E3           | W        |

| DBB01DR0 | 24           | #       | CMP_CR0    | 64           | #      |          | A4           | SS     | DEC_DH   | E4           | RC       |

| DBB01DR1 | 25           | W       | ASY_CR     | 65           | #      |          | A5           |        | DEC_DL   | E5           | RC       |

| DBB01DR2 | 26           | RW      | CMP CR1    | 66           | RW     |          | A6           | 1      | DEC CR0  | E6           | RW       |

Blank fields are Reserved and should not be accessed.

# Access is bit specific.

### Table 6-1. Register Map Bank 0 Table: User Space (continued)

| Name     | Addr (0,Hex) | Access | Name     | Addr (0,Hex) | Access                                | Name    | Addr (0,Hex) | Access | Name     | Addr (0,Hex) | Access   |

|----------|--------------|--------|----------|--------------|---------------------------------------|---------|--------------|--------|----------|--------------|----------|

| DBB01CR0 | 27           | #      | 8 6      | 67           |                                       |         | A7           |        | DEC_CR1  | E7           | RW       |

| DCB02DR0 | 28           | #      | i        | 68           | · · · · · · · · · · · · · · · · · · · |         | A8           | S      | MUL_X    | E8           | W        |

| DCB02DR1 | 29           | W      |          | 69           |                                       |         | A9           |        | MUL_Y    | E9           | W        |

| DCB02DR2 | 2A           | RW     | ů.       | 6A           |                                       |         | AA           |        | MUL_DH   | EA           | R        |

| DCB02CR0 | 2B           | #      |          | 6B           |                                       |         | AB           |        | MUL_DL   | EB           | R        |

| DCB03DR0 | 2C           | #      | 8 8      | 6C           |                                       |         | AC           |        | ACC_DR1  | EC           | RW       |

| DCB03DR1 | 2D           | W      |          | 6D           |                                       |         | AD           |        | ACC_DR0  | ED           | RW       |

| DCB03DR2 | 2E           | RW     | 8        | 6E           |                                       |         | AE           |        | ACC_DR3  | EE           | RW       |

| DCB03CR0 | 2F           | #      |          | 6F           |                                       |         | AF           |        | ACC_DR2  | EF           | RW       |

| DBB10DR0 | 30           | #      | ACB00CR3 | 70           | RW                                    | RDI0RI  | B0           | RW     |          | F0           |          |

| DBB10DR1 | 31           | W      | ACB00CR0 | 71           | RW                                    | RDI0SYN | B1           | RW     |          | F1           |          |

| DBB10DR2 | 32           | RW     | ACB00CR1 | 72           | RW                                    | RDI0IS  | B2           | RW     |          | F2           |          |

| DBB10CR0 | 33           | #      | ACB00CR2 | 73           | RW                                    | RDI0LT0 | B3           | RW     |          | F3           |          |

| DBB11DR0 | 34           | #      | ACB01CR3 | 74           | RW                                    | RDI0LT1 | B4           | RW     |          | F4           |          |

| DBB11DR1 | 35           | W      | ACB01CR0 | 75           | RW                                    | RDI0RO0 | B5           | RW     |          | F5           |          |

| DBB11DR2 | 36           | RW     | ACB01CR1 | 76           | RW                                    | RDI0RO1 | B6           | RW     |          | F6           |          |

| DBB11CR0 | 37           | #      | ACB01CR2 | 77           | RW                                    |         | B7           |        | CPU_F    | F7           | RL       |

| DCB12DR0 | 38           | #      | ACB02CR3 | 78           | RW                                    | RDI1RI  | B8           | RW     |          | F8           | 2        |

| DCB12DR1 | 39           | W      | ACB02CR0 | 79           | RW                                    | RDI1SYN | B9           | RW     |          | F9           | <u> </u> |

| DCB12DR2 | 3A           | RW     | ACB02CR1 | 7A           | RW                                    | RDI1IS  | BA           | RW     |          | FA           |          |

| DCB12CR0 | 3B           | #      | ACB02CR2 | 7B           | RW                                    | RDI1LT0 | BB           | RW     |          | FB           | 2        |

| DCB13DR0 | 3C           | #      | ACB03CR3 | 7C           | RW                                    | RDI1LT1 | BC           | RW     |          | FC           |          |

| DCB13DR1 | 3D           | W      | ACB03CR0 | 7D           | RW                                    | RDI1RO0 | BD           | RW     |          | FD           |          |

| DCB13DR2 | 3E           | RW     | ACB03CR1 | 7E           | RW                                    | RDI1RO1 | BE           | RW     | CPU_SCR1 | FE           | #        |

| DCB13CR0 | 3F           | #      | ACB03CR2 | 7F           | RW                                    |         | BF           |        | CPU_SCR0 | FF           | #        |

Blank fields are Reserved and should not be accessed.

# Access is bit specific.

### Table 6-2. Register Map Bank 1 Table: Configuration Space

| Name    | Add (1,Hex) |    | Name     | Addr (1,Hex) | Access | Name     | Addr (1,Hex) | Access | Name                                   | Addr (1,Hex) | Access |

|---------|-------------|----|----------|--------------|--------|----------|--------------|--------|----------------------------------------|--------------|--------|

| PRT0DM0 | 00          | RW |          | 40           |        | ASC10CR0 | 80           | RW     |                                        | C0           |        |

| PRT0DM1 | 01          | RW |          | 41           | -      | ASC10CR1 | 81           | RW     |                                        | C1           |        |

| PRT0IC0 | 02          | RW |          | 42           |        | ASC10CR2 | 82           | RW     |                                        | C2           |        |

| PRT0IC1 | 03          | RW |          | 43           |        | ASC10CR3 | 83           | RW     | 8 H                                    | C3           |        |

| PRT1DM0 | 04          | RW | 1        | 44           |        | ASD11CR0 | 84           | RW     |                                        | C4           |        |

| PRT1DM1 | 05          | RW |          | 45           |        | ASD11CR1 | 85           | RW     | 8                                      | C5           |        |

| PRT1IC0 | 06          | RW |          | 46           |        | ASD11CR2 | 86           | RW     |                                        | C6           |        |

| PRT1IC1 | 07          | RW |          | 47           |        | ASD11CR3 | 87           | RW     | St                                     | C7           |        |

| PRT2DM0 | 08          | RW |          | 48           |        | ASC12CR0 | 88           | RW     |                                        | C8           | 1      |

| PRT2DM1 | 09          | RW | 8        | 49           |        | ASC12CR1 | 89           | RW     | 9 B                                    | C9           |        |

| PRT2IC0 | 0A          | RW | 1        | 4A           |        | ASC12CR2 | 8A           | RW     | 11 I I I I I I I I I I I I I I I I I I | CA           | 1      |

| PRT2IC1 | 0B          | RW | 1        | 4B           |        | ASC12CR3 | 8B           | RW     | 4                                      | СВ           |        |

| PRT3DM0 | 0C          | RW |          | 4C           |        | ASD13CR0 | 8C           | RW     | S                                      | CC           |        |

| PRT3DM1 | 0D          | RW |          | 4D           |        | ASD13CR1 | 8D           | RW     | 3 2                                    | CD           |        |

| PRT3IC0 | 0E          | RW | 6        | 4E           |        | ASD13CR2 | 8E           | RW     | S                                      | CE           |        |

| PRT3IC1 | 0F          | RW |          | 4F           |        | ASD13CR3 | 8F           | RW     | 10                                     | CF           | 1      |

| PRT4DM0 | 10          | RW |          | 50           |        | ASD20CR0 | 90           | RW     | GDI_O_IN                               | D0           | RW     |

| PRT4DM1 | 11          | RW | 1        | 51           |        | ASD20CR1 | 91           | RW     | GDI_E_IN                               | D1           | RW     |

| PRT4IC0 | 12          | RW |          | 52           |        | ASD20CR2 | 92           | RW     | GDI_O_OU                               | D2           | RW     |

| PRT4IC1 | 13          | RW |          | 53           |        | ASD20CR3 | 93           | RW     | GDI_E_OU                               | D3           | RW     |

| PRT5DM0 | 14          | RW |          | 54           |        | ASC21CR0 | 94           | RW     |                                        | D4           | 1      |

| PRT5DM1 | 15          | RW |          | 55           |        | ASC21CR1 | 95           | RW     |                                        | D5           |        |

| PRT5IC0 | 16          | RW | <u>1</u> | 56           |        | ASC21CR2 | 96           | RW     | S - S                                  | D6           |        |

| PRT5IC1 | 17          | RW |          | 57           |        | ASC21CR3 | 97           | RW     |                                        | D7           |        |

|         | 18          |    |          | 58           |        | ASD22CR0 | 98           | RW     | S                                      | D8           |        |

|         | 19          |    |          | 59           |        | ASD22CR1 | 99           | RW     |                                        | D9           |        |

|         | 1A          | 1  |          | 5A           |        | ASD22CR2 | 9A           | RW     |                                        | DA           | T      |

|         | 1B          |    |          | 5B           |        | ASD22CR3 | 9B           | RW     |                                        | DB           |        |

|         | 1C          |    | 8        | 5C           |        | ASC23CR0 | 9C           | RW     | 11. E                                  | DC           |        |

|         | 1D          |    |          | 5D           |        | ASC23CR1 | 9D           | RW     | OSC_GO_EN                              | DD           | RW     |

|         | 1E          |    | 8        | 5E           |        | ASC23CR2 | 9E           | RW     | OSC_CR4                                | DE           | RW     |

|         | 1F          | 1  |          | 5F           |        | ASC23CR3 | 9F           | RW     | OSC_CR3                                | DF           | RW     |

| DBB00FN | 20          | RW | CLK_CR0  | 60           | RW     |          | A0           |        | OSC_CR0                                | E0           | RW     |

| DBB00IN | 21          | RW | CLK_CR1  | 61           | RW     |          | A1           |        | OSC_CR1                                | E1           | RW     |

| DBB00OU | 22          | RW | ABF_CR0  | 62           | RW     |          | A2           | 1      | OSC CR2                                | E2           | RW     |

#### Table 6-2. Register Map Bank 1 Table: Configuration Space (continued)

| Name    | Add (1,Hex) | Access | Name     | Addr (1,Hex) | Access | Name    | Addr (1,Hex) | Access   | Name                                    | Addr (1,Hex) | Access |

|---------|-------------|--------|----------|--------------|--------|---------|--------------|----------|-----------------------------------------|--------------|--------|

|         | 23          |        | AMD_CR0  | 63           | RW     |         | A3           |          | VLT_CR                                  | E3           | RW     |

| DBB01FN | 24          | RW     | 8        | 64           |        |         | A4           |          | VLT_CMP                                 | E4           | R      |

| DBB01IN | 25          | RW     |          | 65           |        |         | A5           |          |                                         | E5           |        |

| DBB01OU | 26          | RW     | AMD_CR1  | 66           | RW     |         | A6           | 1        |                                         | E6           |        |

|         | 27          |        | ALT_CR0  | 67           | RW     |         | A7           |          |                                         | E7           |        |

| DCB02FN | 28          | RW     | ALT_CR1  | 68           | RW     |         | A8           |          | IMO_TR                                  | E8           | W      |

| DCB02IN | 29          | RW     | CLK_CR2  | 69           | RW     |         | A9           |          | ILO_TR                                  | E9           | W      |

| DCB02OU | 2A          | RW     | S        | 6A           |        |         | AA           |          | BDG_TR                                  | EA           | RW     |

| 2       | 2B          |        | 1        | 6B           |        |         | AB           |          | ECO_TR                                  | EB           | W      |

| DCB03FN | 2C          | RW     |          | 6C           |        |         | AC           | 3        | 2 3                                     | EC           |        |

| DCB03IN | 2D          | RW     | 12       | 6D           |        |         | AD           | 3        |                                         | ED           |        |

| DCB03OU | 2E          | RW     |          | 6E           |        |         | AE           | ( )<br>( | 2 · · · · · · · · · · · · · · · · · · · | EE           |        |

| ð.      | 2F          |        |          | 6F           |        |         | AF           |          | 8                                       | EF           |        |

| DBB10FN | 30          | RW     | ACB00CR3 | 70           | RW     | RDIORI  | B0           | RW       | ÷                                       | F0           |        |

| DBB10IN | 31          | RW     | ACB00CR0 | 71           | RW     | RDI0SYN | B1           | RW       | 3                                       | F1           |        |

| DBB10OU | 32          | RW     | ACB00CR1 | 72           | RW     | RDI0IS  | B2           | RW       | 10 - E                                  | F2           |        |

|         | 33          |        | ACB00CR2 | 73           | RW     | RDI0LT0 | B3           | RW       |                                         | F3           |        |

| DBB11FN | 34          | RW     | ACB01CR3 | 74           | RW     | RDI0LT1 | B4           | RW       |                                         | F4           |        |

| DBB11IN | 35          | RW     | ACB01CR0 | 75           | RW     | RDI0RO0 | B5           | RW       | S                                       | F5           |        |

| DBB11OU | 36          | RW     | ACB01CR1 | 76           | RW     | RDI0RO1 | B6           | RW       |                                         | F6           |        |

| 6       | 37          |        | ACB01CR2 | 77           | RW     |         | B7           |          | CPU_F                                   | F7           | RL     |

| DCB12FN | 38          | RW     | ACB02CR3 | 78           | RW     | RDI1RI  | B8           | RW       |                                         | F8           |        |

| DCB12IN | 39          | RW     | ACB02CR0 | 79           | RW     | RDI1SYN | B9           | RW       | 13                                      | F9           |        |

| DCB12OU | 3A          | RW     | ACB02CR1 | 7A           | RW     | RDI1IS  | BA           | RW       |                                         | FA           |        |

| 5       | 3B          |        | ACB02CR2 | 7B           | RW     | RDI1LT0 | BB           | RW       | 11. I                                   | FB           |        |

| DCB13FN | 3C          | RW     | ACB03CR3 | 7C           | RW     | RDI1LT1 | BC           | RW       |                                         | FC           |        |

| DCB13IN | 3D          | RW     | ACB03CR0 | 7D           | RW     | RDI1RO0 | BD           | RW       | 12                                      | FD           |        |

| DCB13OU | 3E          | RW     | ACB03CR1 | 7E           | RW     | RDI1RO1 | BE           | RW       | CPU_SCR1                                | FE           | #      |

|         | 3F          |        | ACB03CR2 | 7F           | RW     |         | BF           |          | CPU_SCR0                                | FF           | #      |

Blank fields are Reserved and should not be accessed.

# Access is bit specific.

## 7. Electrical Specifications

This section presents the DC and AC electrical specifications of the CY8CLED08 EZ-Color device. For the most up to date electrical specifications, confirm that you have the most recent data sheet by going to the web at <a href="http://www.cypress.com/ez-color">http://www.cypress.com/ez-color</a>.

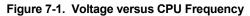

Specifications are valid for -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C and T<sub>J</sub>  $\leq$  100°C, except where noted. Specifications for devices running at greater than 12 MHz are valid for -40°C  $\leq$  T<sub>A</sub>  $\leq$  70°C and T<sub>J</sub>  $\leq$  82°C.

The following table lists the units of measure that are used in this section.

| Table 7-1. | Units of Measure |  |

|------------|------------------|--|

|------------|------------------|--|

| Symbol | Unit of Measure             | Symbol | Unit of Measure               |

|--------|-----------------------------|--------|-------------------------------|

| °C     | degree Celsius              | μVV    | microwatts                    |

| dB     | decibels                    | mA     | milli-ampere                  |

| fF     | femto farad                 | ms     | milli-second                  |

| Hz     | hertz                       | mV     | milli-volts                   |

| КВ     | 1024 bytes                  | nA     | nanoampere                    |

| Kbit   | 1024 bits                   | ns     | nanosecond                    |

| kHz    | kilohertz                   | nV     | nanovolts                     |

| kΩ     | kilohm                      | Ω      | ohm                           |

| MHz    | megahertz                   | рА     | picoampere                    |

| MΩ     | megaohm                     | pF     | picofarad                     |

| μA     | microampere                 | рр     | peak-to-peak                  |

| μF     | microfarad                  | ppm    | parts per million             |

| μH     | microhenry                  | ps     | picosecond                    |

| μS     | microsecond                 | sps    | samples per second            |

| μV     | microvolts                  | σ      | sigma: one standard deviation |

| μVrms  | microvolts root-mean-square | V      | volts                         |

## 7.1 Absolute Maximum Ratings

## Table 7-2. Absolute Maximum Ratings

| Symbol            | Description                                                      | Min       | Тур     | Max       | Units | Notes                                                                                                                                                                                                                                  |

|-------------------|------------------------------------------------------------------|-----------|---------|-----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub>  | Storage Temperature                                              | -55       | 25      | +100      | °C    | Higher storage temperatures will<br>reduce data retention time. Recom-<br>mended storage temperature is<br>$+25^{\circ}C \pm 25^{\circ}C$ . Extended duration<br>storage temperatures above $65^{\circ}C$ will<br>degrade reliability. |

| ΤΑ                | Ambient Temperature with Power Applied                           | -40       | -       | +85       | °C    |                                                                                                                                                                                                                                        |

| Vdd               | Supply Voltage on Vdd Relative to<br>Vss                         | -0.5      | -       | +6.0      | V     |                                                                                                                                                                                                                                        |

| Vio               | DC Input Voltage                                                 | Vss- 0.5  | -       | Vdd + 0.5 | V     |                                                                                                                                                                                                                                        |

| Vioz              | DC Voltage Applied to Tri-state                                  | Vss - 0.5 | -       | Vdd + 0.5 | V     |                                                                                                                                                                                                                                        |

| I <sub>MIO</sub>  | Maximum Current into any Port Pin                                | -25       | - 1     | +50       | mA    |                                                                                                                                                                                                                                        |

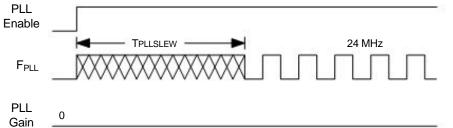

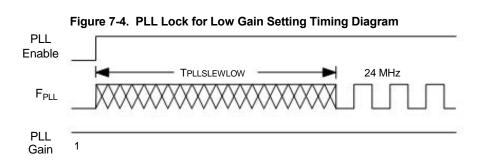

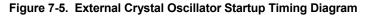

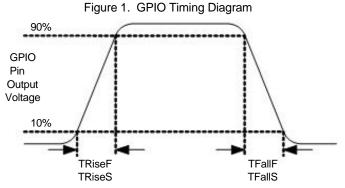

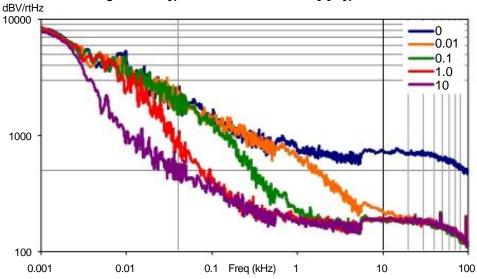

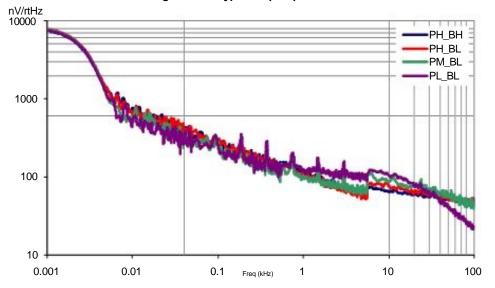

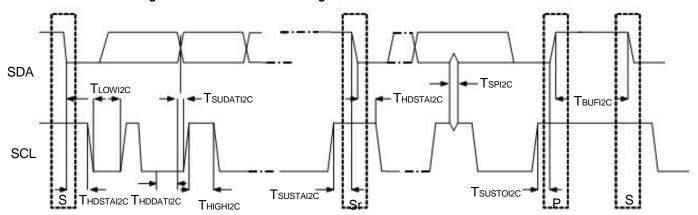

| I <sub>MAIO</sub> | Maximum Current into any Port Pin<br>Configured as Analog Driver | -50       | -       | +50       | mA    |                                                                                                                                                                                                                                        |