# MRF89XA Data Sheet

Ultra Low-Power, Integrated ISM Band Sub-GHz Transceiver

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, Keeloq, Keeloq logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## Ultra Low-Power, Integrated ISM Band Sub-GHz Transceiver

### **Features**

- · Fully integrated ultra low-power, sub-GHz transceiver

- · Wide band Half-duplex transceiver

- · Supports proprietary sub-GHz wireless protocols

- · Simple, 4-wire SPI-compatible interface

- CMOS/TTL-compatible I/Os

- · On-chip oscillator circuit

- · Dedicated clock output

- · Supports power-saving modes

- · Operating voltage: 2.1V-3.6V

- · Low-Current Consumption, Typically:

- 3 mA in RX mode

- 25 mA @ +10 dBm in TX mode

- 0.1  $\mu A$  (Typical) and 2  $\mu A$  (Maximum) in Sleep mode

- Supports Industrial Temperature

- Small, 32-pin TQFN package; complies with ETSI EN 300 220 and FCC part 15

## **RF/Analog Features**

- Supports ISM band sub-GHz frequency ranges: 863-870, 902-928 and 950-960 MHz

- · Modulation technique: Supports FSK and OOK

- Supports high data rates: Up to 200 kbps, NRZ coding

- Reception sensitivity: Down to -107 dBm at 25 kb/s in FSK, -113 dBm at 2 kb/s in OOK

- RF output power: +12.5 dBm programmable in eight steps

- Wide Received Signal Strength Indicator (RSSI), dynamic range: 70 dB from RX noise floor

- Signal-ended RF input/output

- · On-chip frequency synthesizer

- Supports PLL loop filter with lock detect

- Integrated Power Amplifier (PA) and Low Noise Amplifiers (LNA)

- · Channel filters

- · On-chip IF gain and mixers

- · Integrated low phase noise VCO

#### **Baseband Features**

- Packet handling feature with data whitening and automatic CRC generation

- · Incoming sync word (pattern) recognition

- Built-in bit synchronizer for incoming data, and clock synchronization and recovery

- 64-byte Transmit/Receive FIFO with preload in Standby mode

- Supports Manchester Encoding/Decoding Techniques

## **Typical Applications**

- · Home/industrial/building automation

- · Remote wireless control

- · Wireless PC peripherals

- · Remote keyless entry

- · Wireless sensor networks

- · Vehicle sensor monitoring

- Telemetry

- · Data logging systems

- · Wireless alarm

- · Remote automatic meter reading

- · Security systems for home/industrial environments

- · Automobile immobilizers

- · Sports and performance monitoring

- · Wireless toy controls

- · Medical applications

## **General Description**

The MRF89XA is a single chip FSK/OOK transceiver capable of operating in the 863-870 MHz and 902-928 MHz license-free ISM frequency bands, as well as the 950-960 MHz frequency band. The lowcost MRF89XA is optimized for very low-power consumption (3 mA in Receiver mode). It incorporates a baseband modem with data rates up to 200 kb/s. Data handling features include a 64-byte FIFO, packet handling, automatic CRC generation and data whitening. Its highly integrated architecture allows for minimum external component count while still maintaining design flexibility. All major RF communication parameters are programmable and most of them may be dynamically set. It complies with European (ETSI EN 300-220 V2.1.1) and North American (FCC Part 15.247 and 15.249) regulatory standards.

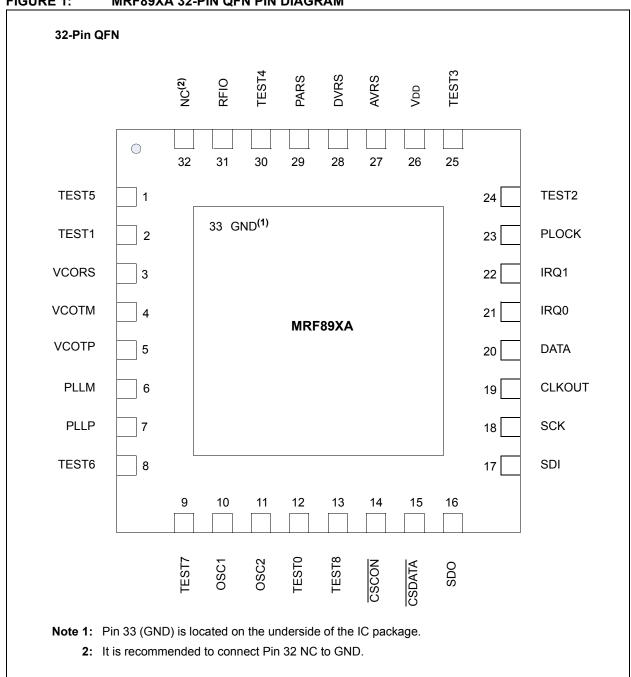

## Pin Diagram

The following diagram shows the top view pin arrangement of the 32-pin QFN package.

FIGURE 1: MRF89XA 32-PIN QFN PIN DIAGRAM

### **Table of Contents**

| 1.0   | Overview                         |   |

|-------|----------------------------------|---|

| 2.0   | Hardware Description             | 9 |

| 3.0   | Electrical Characteristics       | 1 |

|       | ndix A: Revision History         |   |

| The I | Aicrochip Web Site               | 2 |

| Custo | omer Change Notification Service | 2 |

|       | omer Support                     |   |

|       | er Response                      |   |

| Prod  | uct Identification System        | 2 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

## 1.0 OVERVIEW

Microchip Technology's MRF89XA is a fully integrated, half-duplex, sub-GHz transceiver. This low-power, single chip RF FSK and OOK baseband transceiver supports:

- · Super Heterodyne Architecture

- Multi-Channel, Multi-Band Synthesizer with Phase Lock Loop (PLL) for easy RF Design

- · Power Amplifier (PA)

- · Low Noise Amplifier (LNA)

- · I/Q Two Stage Down Converter Mixers

- I/Q Demodulator, FSK/OOK

- · Baseband Filters and Amplifiers

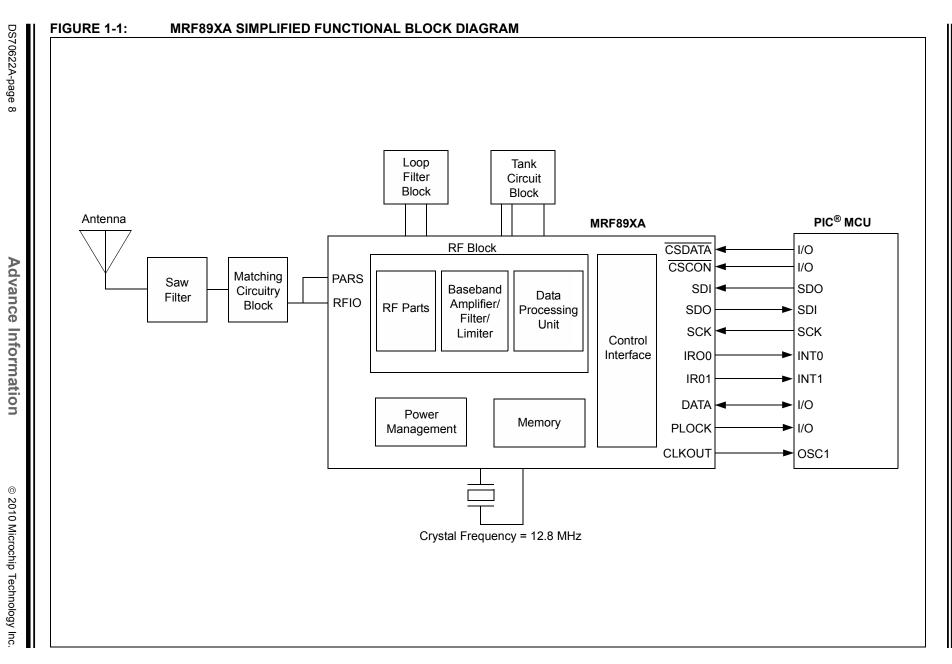

The simplified functional block diagram of MRF89XA is shown in Figure 1-1.

The MRF89XA is a good choice for low-cost, high-volume, low data rate (<256 kbps), two-way short range wireless applications. This is a single chip FSK and OOK transceiver capable of operation in the 863-870 MHz and 902-928 MHz license-free ISM frequency bands, as well as the 950-960 MHz frequency band.

The low-cost MRF89XA is optimized for very low-power consumption (3 mA in Receiver mode). It incorporates a baseband modem with data rates up to 200 kb/s in FSK and 32 kb/s in OOK. Data handling features include a 64-byte FIFO, packet handling, automatic CRC generation and data whitening. The device also supports Manchester coding techniques. Its highly integrated architecture allows for minimum external component count while still maintaining design flexibility. All major RF communication parameters are programmable and most of them may be dynamically set.

The MRF89XA complies with European (ETSI EN 300-220 V2.1.1) and North American (FCC Part 15.247 and 15.249) regulatory standards, and therefore, can be used for all applications looking for FCC, IC, or ETSI certification in the ISM band and licensed bands also.

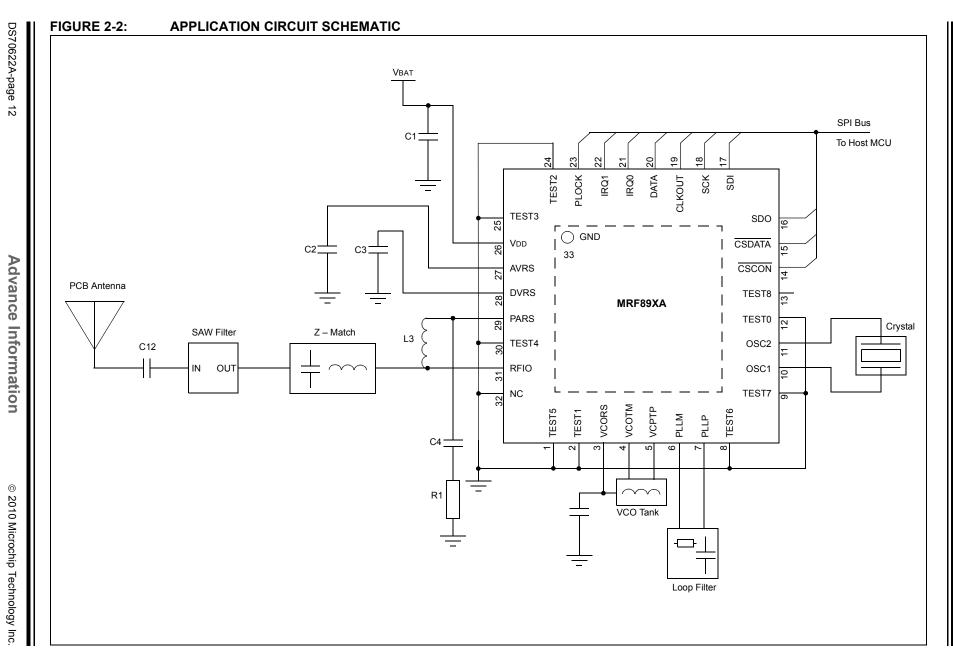

The MRF89XA supports a stable sensitivity and linearity characteristics for a wide supply range and is internally regulated. The frequency synthesizer of the MRF89XA is a fully integrated integer-N type PLL. The PLL circuit requires only five external components for the PLL loop filter and the VCO tank circuit. The PLL and low phase noise provides for excellent adjacent channel rejection capability, Bit Error Rate (BER) and larger communication coverage along with higher output power.

The crystal oscillator provided on the MRF89XA device provides the reference clock for the PLL. In order to minimize the total system cost, a communication link in most of the applications can be created using a low-cost, generic 12.8 MHz crystal, a bypass filter and an affordable microcontroller. The MRF89XA provides a clock signal for the microcontroller and avoids the need for a second crystal on the circuit board. The transceiver can be interfaced with many popular Microchip PIC<sup>®</sup> microcontrollers via a 4-wire SPI, interrupt (IRO), PLL lock and clock out. The interface between the microcontroller and MRF89XA is shown in Figure 1-1.

The MRF89XA supports the following digital data processing features:

- PLL and I/Q VCO Configuration

- · Receiver Signal Strength Indicator

- · Sync Word Recognition

- · Packet Handler

- · Interrupt and Flags

- Different Operating Modes (Continuous, Buffer and Packet)

- Data Filtering/Whitening/Encoding

- · Baseband Power Amplifier

- · TX/RX Data Buffer

The role is to interface the data to/from the modulator/demodulator and the microcontroller access points (SPI, IRQ and DATA pins). It also controls all the Configuration registers. The receiver's Baseband Bandwidth (BBBW) can be programmed to accommodate various deviations and data rates requirements.

The high-resolution PLL allows:

- The usage of multiple channels in any of the bands

- The rapid settling time allows for faster frequency hopping, bypassing multi-path fading and interference to achieve robust wireless links

An optional Bit Synchronizer (BitSync) is provided, to supply a synchronous clock and data stream to a companion microcontroller in Continuous mode, or to fill the FIFO with glitch-free data in Buffered mode. The transceiver is integrated with different power-saving modes and an internal wake-up time to keep track of the activities, which reduces the overall current consumption and extends the battery life. The small size and low-power consumption of the MRF89XA makes it ideal for various short range radio applications.

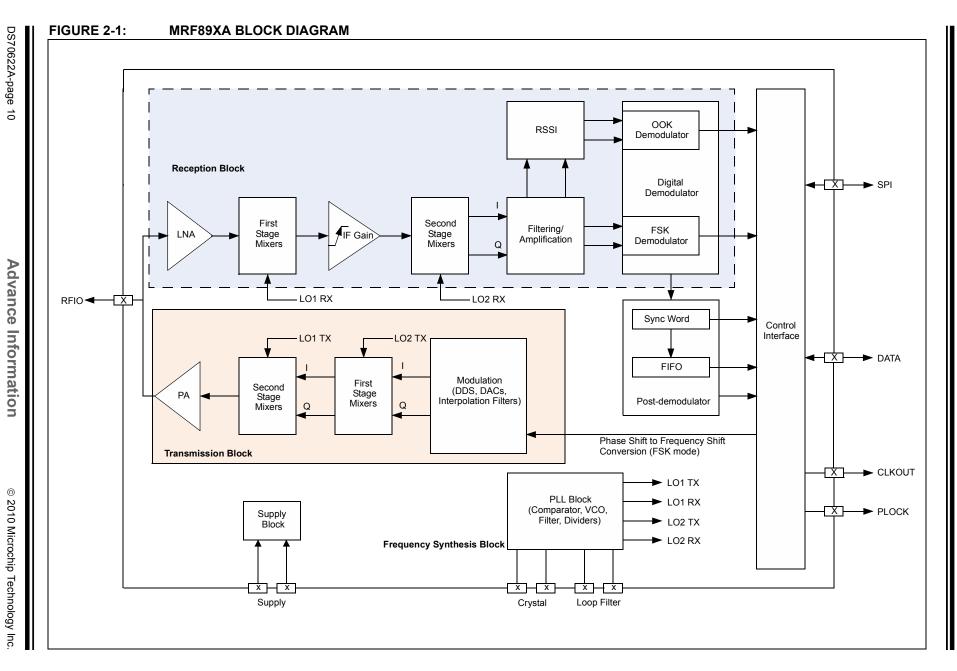

## 2.0 HARDWARE DESCRIPTION

The MRF89XA is an integrated, single chip, low-power ISM band sub-GHz transceiver. A simplified architectural block diagram of the MRF89XA is shown in Figure 2-1. The frequency synthesizer is clocked by an external 12.8 crystal, and frequency ranges from 863-870 MHz, 902-928 MHz and 950-960 MHz.

The MRF89XA receiver employs a super-heterodyne architecture. Here, the first IF is 1/9th of the RF frequency (approximately 100 MHz). The second down conversion down converts the I and Q signals to baseband in the case of the FSK receiver (Zero IF) and to a low-IF (IF2) for the OOK receiver. After the second down-conversion stage, the received signal is channel select filtered and amplified to a level adequate for demodulation. Both FSK and OOK demodulation are available. Image rejection is achieved by the SAW filter.

The baseband I and Q signals at the transmitter side are digitally generated by a DDS whose Digital-to-Analog Converters (DAC) followed by two anti-aliasing low-pass filters transform the digital signal into analog In-Phase (I) and Quadrature (Q) components whose frequency is the selected Frequency Deviation (Fdev). The transmitter supports both FSK and OOK modes of operation. The transmitter has a typical output power of +12.5 dBm. An

internal transmit/receive switch combines the transmitter and receiver circuits into a single-ended RFIO pin. This pin is connected to the impedance matching circuitry (Balun) and to the external antenna with power amplifier pin, if required. The device operates in the low-voltage range of 2.1V to 3.6V, and in Sleep mode, it operates at a very low-current state, typically 0.1  $\mu$ A.

The quality of the data is validated using the RSSI and bit synchronizer blocks built into the transceiver. Data is buffered in 64-byte transmitter registers and receiver FIFOs. The frequency synthesizer allows the use of a low-accuracy, low-cost crystal. CLKOUT can be used to clock the external controller. The transceiver is controlled via a 4-wire Serial Peripheral Interface (SPI), interrupt (IRO0 and IRO1), PLOCK, DATA and Chip Select pins for SPI.

The MRF89XA supports the following feature blocks:

- · Data Filtering and Whitening

- · Bit Synchronization

- · 64-Byte Transmit and Receive FIFO Buffer

- · General Configuration Registers

These features reduce the processing load, which allows the use of simple, low-cost 8-bit microcontrollers for data processing.

TABLE 2-1: PIN DESCRIPTIONS

| Pin<br>Number | Pin Name | Pin Type       | Description                                                         |  |  |

|---------------|----------|----------------|---------------------------------------------------------------------|--|--|

| 1             | TEST5    | Digital I/O    | Test Pin. Connect to Ground.                                        |  |  |

| 2             | TEST1    | Digital I/O    | Test Pin. Connect to Ground.                                        |  |  |

| 3             | VCORS    | Analog Output  | Regulated voltage supply of the VCO.                                |  |  |

| 4             | VCOTM    | Analog I/O     | VCO tank.                                                           |  |  |

| 5             | VCOTP    | Analog I/O     | VCO tank.                                                           |  |  |

| 6             | PLLM     | Analog I/O     | PLL loop filter.                                                    |  |  |

| 7             | PLLP     | Analog I/O     | PLL loop filter.                                                    |  |  |

| 8             | TEST6    | Digital I/O    | Test Pin. Connect to Ground.                                        |  |  |

| 9             | TEST7    | Digital I/O    | Test Pin. Connect to Ground.                                        |  |  |

| 10            | OSC1     | Analog Input   | •                                                                   |  |  |

| 11            | OSC2     | Analog Input   | Crystal connection.                                                 |  |  |

| 12            | TEST0    | Digital Input  | Test Pin. Connect to Ground.                                        |  |  |

| 13            | TEST8    | Digital I/O    | Test Pin. Used for POR (allow pin to float; do not connect signal). |  |  |

| 14            | CSCON    | Digital Input  | SPI Configure Chip Select.                                          |  |  |

| 15            | CSDATA   | Digital Input  | SPI Data Chip Select.                                               |  |  |

| 16            | SDO      | Digital Output | Serial data output interface from MRF89XA.                          |  |  |

| 17            | SDI      | Digital Input  | Serial data input interface to MRF89XA.                             |  |  |

| 18            | SCK      | Digital Input  | Serial clock interface.                                             |  |  |

| 19            | CLKOUT   | Digital Output | Clock output.                                                       |  |  |

| 20            | DATA     | Digital I/O    | NRZ data input and output (Continuous mode).                        |  |  |

| 21            | IRQ0     | Digital Output | Interrupt request output ('0').                                     |  |  |

| 22            | IRQ1     | Digital Output | Interrupt request output ('1').                                     |  |  |

| 23            | PLOCK    | Digital Output | PLL lock detection output.                                          |  |  |

| 24            | TEST2    | Digital I/O    | Test Pin. Connect to Ground.                                        |  |  |

| 25            | TEST3    | Digital I/O    | Test Pin. Connect to Ground.                                        |  |  |

| 26            | VDD      | Power          | Supply voltage.                                                     |  |  |

| 27            | AVRS     | Analog Output  | Regulated supply of the analog circuitry.                           |  |  |

| 28            | DVRS     | Analog Output  | Regulated supply of the digital circuitry.                          |  |  |

| 29            | PARS     | Analog Output  | Regulated supply of the PA.                                         |  |  |

| 30            | TEST4    | Digital I/O    | Connect to GND.                                                     |  |  |

| 31            | RFIO     | Analog I/O     | RF input/output.                                                    |  |  |

| 32            | NC       | _              | No Connection. Connect to Ground.                                   |  |  |

| 33            | Vss      | Ground         | Exposed Pad. Connect to Ground.                                     |  |  |

## 2.1 Memory Map for MRF89XA Configuration/Control/Status Registers

The memory in the MRF89XA transceiver is implemented as static RAM and is accessible via the SPI port. Each memory location functionally addresses the command, control, status or data/FIFO fields as shown in Table 2-2 and Table 2-3. The control registers provide

control, status and configuration information. The device address for the transceiver is done by indexing the base address in the RAM memory. The registers operate fundamentally on parameters common to transmit and receive modes, Interrupt registers, receiver parameters, Sync pattern, transmitter parameters, crystal oscillator parameters and packet handler parameters. The FIFO serves as a temporary buffer for data transmission and reception.

TABLE 2-2: CONFIGURATION/CONTROL/STATUS REGISTER DESCRIPTION

| General Parameters Configuration Registers: Size – 13 Bytes, Start Address – 00 |                     |                  |                                                                                                |                                                                                            |  |  |  |

|---------------------------------------------------------------------------------|---------------------|------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| SI. No.                                                                         | Register<br>Address | Register<br>Name | Register Description                                                                           | Related Control Functions                                                                  |  |  |  |

| 1.                                                                              | 0                   | GCONREG          | General Configuration Register                                                                 | Transceiver mode, frequency band selection, VCO trimming, PLL frequency dividers selection |  |  |  |

| 2.                                                                              | 1                   | DMODREG          | Data and Modulation Configuration Register  Modulation type, Data mode threshold type, IF gain |                                                                                            |  |  |  |

| 3.                                                                              | 2                   | FDEVREG          | Frequency Deviation Control Register                                                           | Frequency deviation in FSK Transmit mode                                                   |  |  |  |

| 4.                                                                              | 3                   | BRSREG           | Bit Rate Set Register                                                                          | Operational bit rate                                                                       |  |  |  |

| 5.                                                                              | 4                   | FLTHREG          | Floor Threshold Control Register                                                               | Floor threshold in OOK Receive mode                                                        |  |  |  |

| 6.                                                                              | 5                   | FIFOCREG         | FIFO Configuration Register                                                                    | FIFO size and threshold                                                                    |  |  |  |

| 7.                                                                              | 6                   | R1CNTSREG        | R1 Counter Set Register                                                                        | Value input for R1 counter                                                                 |  |  |  |

| 8.                                                                              | 7                   | P1CNTSREG        | P1 Counter Set Register                                                                        | Value input for P1 counter                                                                 |  |  |  |

| 9.                                                                              | 8                   | S1CNTSREG        | S1 Counter Set Register                                                                        | Value input for S1 counter                                                                 |  |  |  |

| 10.                                                                             | 9                   | R2CNTSREG        | R2 Counter Set Register                                                                        | Value input for R2 counter                                                                 |  |  |  |

| 11.                                                                             | 10                  | P2CNTSREG        | P2 Counter Set Register                                                                        | Value input for P2 counter                                                                 |  |  |  |

| 12.                                                                             | 11                  | S2CNTSREG        | S2 Counter Set Register                                                                        | Value input for S2 counter                                                                 |  |  |  |

| 13.                                                                             | 12                  | PACONREG         | Power Amplifier Control Register                                                               | PA regulator output voltage                                                                |  |  |  |

| Interrupt | Interrupt Parameters Configuration Registers: Size – 3 Bytes, Start Address – 13 |                  |                                                                        |                                                                                                                                                        |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SI. No.   | Register<br>Address                                                              | Register<br>Name | Register Description                                                   | Related Control Functions                                                                                                                              |  |  |  |  |  |

| 14.       | 13                                                                               | FTXRXIREG        | FIFO, Transmit and Receive Interrupt<br>Request Configuration Register | Interrupt request ('0' and '1') in<br>Receive mode, interrupt request ('1')<br>in Transmit mode, interrupt request for<br>FIFO full, empty and overrun |  |  |  |  |  |

| 15.       | 14                                                                               | FTPRIREG         | FIFO Transmit PLL and RSSI<br>Interrupt Configuration Register         | FIFO fill method, FIFO fill, interrupt request for TX start and end, interrupt request for RSSI, PLL lock enable and status                            |  |  |  |  |  |

| 16.       | 15                                                                               | RSTHIREG         | RSSI Threshold Interrupt Request Configuration Register                | RSSI threshold for interrupt                                                                                                                           |  |  |  |  |  |

TABLE 2-2: CONFIGURATION/CONTROL/STATUS REGISTER DESCRIPTION (CONTINUED)

| Receiver | Receiver Parameters Configuration Registers: Size – 6 Bytes, Start Address – 16 |           |                                            |                                                                                                                                                    |  |  |  |  |

|----------|---------------------------------------------------------------------------------|-----------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SI. No.  | No. Register Register Address Name Register Description                         |           | Register Description                       | Related Control Functions                                                                                                                          |  |  |  |  |

| 17.      | 16                                                                              | FILCONREG | Filter Configuration Register              | Passive filter bandwidth selection, sets the receiver bandwidth (Butterworth filter),                                                              |  |  |  |  |

| 18.      | 17                                                                              | PFCONREG  | Polyphase Filter Configuration<br>Register | Selects the central frequency of the polyphase filter                                                                                              |  |  |  |  |

| 19.      | 18                                                                              | SYNCREG   | Sync Control Register                      | Enables polyphase filter (in OOK receive mode, bit synchronizer control, Sync word recognition, Sync word size, Sync word error                    |  |  |  |  |

| 20.      | 19                                                                              | RESVREG   | Reserved Register                          | Reserved for future use                                                                                                                            |  |  |  |  |

| 21.      | 20                                                                              | RSTSREG   | RSSI Status Read Register                  | RSSI output                                                                                                                                        |  |  |  |  |

| 22.      | 21                                                                              | OOKCREG   | OOK Configuration Register                 | RSSI threshold size in OOK demodu-<br>lator, RSSI threshold period in OOK<br>demodulator, cut-off frequency of the<br>OOK threshold in demodulator |  |  |  |  |

| Sync Wo | Sync Word Parameters Configuration Registers: Size – 4 Bytes, Start Address – 22 |                  |                                                        |                                                             |  |  |  |  |

|---------|----------------------------------------------------------------------------------|------------------|--------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| SI. No. | Register<br>Address                                                              | Register<br>Name | Register Description                                   | Related Control Functions                                   |  |  |  |  |

| 23.     | 22                                                                               | SYNCV31REG       | Sync Value 1 <sup>st</sup> Byte Configuration Register | Configuring 1 <sup>st</sup> byte of the 32-bit<br>Sync word |  |  |  |  |

| 24.     | 23                                                                               | SYNCV23REG       | Sync Value 2 <sup>nd</sup> Byte Configuration Register | Configuring 2 <sup>nd</sup> byte of the 32-bit<br>Sync word |  |  |  |  |

| 25.     | 24                                                                               | SYNCV15REG       | Sync Value 3 <sup>rd</sup> Byte Configuration Register | Configuring 3 <sup>rd</sup> byte of the 32-bit<br>Sync word |  |  |  |  |

| 26.     | 25                                                                               | SYNCV07REG       | Sync Value 4 <sup>th</sup> Byte Configuration Register | Configuring 4 <sup>th</sup> byte of the 32-bit<br>Sync word |  |  |  |  |

| Transmitter Parameters Configuration Registers: Size – 1 Byte, Start Address – 26 |                  |   |                                            |                                                        |  |  |  |  |

|-----------------------------------------------------------------------------------|------------------|---|--------------------------------------------|--------------------------------------------------------|--|--|--|--|

| SI. No. Register Address Register Name                                            |                  | _ | Register Description                       | Related Control Functions                              |  |  |  |  |

| 27.                                                                               | 27. 26 TXPARCREG |   | Transmit Parameters Configuration Register | Transmit interpolation cut-off frequency, power output |  |  |  |  |

| Oscillator Parameters Configuration Registers: Size – 1 Byte, Start Address – 27 |  |           |                               |                              |  |  |  |  |

|----------------------------------------------------------------------------------|--|-----------|-------------------------------|------------------------------|--|--|--|--|

| SI. No. Register Address Name                                                    |  |           | Register Description          | Related Control Functions    |  |  |  |  |

| 28. 27 CLKOUTREG C                                                               |  | CLKOUTREG | Clock Output Control Register | Clock-out control, frequency |  |  |  |  |

## TABLE 2-2: CONFIGURATION/CONTROL/STATUS REGISTER DESCRIPTION (CONTINUED)

| Packet Handling Parameters Configuration Registers: Size – 4 Bytes, Start Address – 28 |                     |                  |                                 |                                                                                                               |  |  |  |

|----------------------------------------------------------------------------------------|---------------------|------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| SI. No.                                                                                | Register<br>Address | Register<br>Name | Register Description            | Related Control Functions                                                                                     |  |  |  |

| 29.                                                                                    | 28                  | PLOADREG         | Payload Configuration Register  | Enable Manchester encoding/decoding, payload length                                                           |  |  |  |

| 30.                                                                                    | 29                  | NADDSREG         | Node Address Set Register       | Node's local address for filtering of received packets                                                        |  |  |  |

| 31.                                                                                    | 30                  | PKTCREG          | Packet Configuration Register   | Packet format, size of the preamble, whitening, CRC on/off, address filtering of received packets, CRC status |  |  |  |

| 32.                                                                                    | 31                  | FCRCREG          | FIFO CRC Configuration Register | FIFO auto-clear (if CRC failed), FIFO access                                                                  |  |  |  |

TABLE 2-3: CONFIGURATION/CONTROL/STATUS REGISTER MAP

| Register<br>Function/<br>Parameter<br>Type | Register<br>Address | Register Name | Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1    | Bit 0    | Value on<br>POR |

|--------------------------------------------|---------------------|---------------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|-----------------|

| General                                    | 0                   | GCONREG       | CMOD2     | CMOD1     | CMOD0     | FBS1      | FBS0      | VCOT1     | VCOT0    | RPS      | 0x28            |

| General                                    | 1                   | DMODREG       | MODSEL1   | MODSEL0   | DMODE0    | OOKTYP1   | OOKTYP0   | DMODE1    | IFGAIN1  | IFGAIN   | 0x88            |

|                                            | 2                   | FDEVREG       | FDVAL7    | FDVAL6    | FDVAL5    | FDVAL4    | FDVAL3    | FDVAL2    | FDVAL1   | FDVAL0   | 0x03            |

|                                            | 3                   | BRSREG        | Reserved  | BRVAL6    | BRVAL5    | BRVAL4    | BRVAL3    | BRVAL2    | BRVAL1   | BRVAL0   | 0x07            |

|                                            | 4                   | FLTHREG       | FTOVAL7   | FTOVAL6   | FTOVAL5   | FTOVAL4   | FTOVAL3   | FTOVAL2   | FTOVAL1  | FTOVAL0  | 0x0C            |

|                                            | 5                   | FIFOCREG      | FSIZE1    | FSIZE0    | FTINT5    | FTINT4    | FTINT3    | FTINT2    | FTINT1   | FTINT0   | 0x0F            |

|                                            | 6                   | R1CNTSREG     | R1CVAL7   | R1CVAL6   | R1CVAL5   | R1CVAL4   | R1CVAL3   | R1CVAL2   | R1CVAL1  | R1CVAL0  | 0x77            |

|                                            | 7                   | P1CNTSREG     | P1CVAL7   | P1CVAL6   | P1CVAL5   | P1CVAL4   | P1CVAL3   | P1CVAL2   | P1CVAL1  | P1CVAL0  | 0x64            |

|                                            | 8                   | S1CNTSREG     | S1CVAL7   | S1CVAL6   | S1CVAL5   | S1CVAL4   | S1CVAL3   | S1CVAL2   | S1CVAL1  | S1CVAL0  | 0x32            |

|                                            | 9                   | R2CNTSREG     | R2CVAL7   | R2CVAL6   | R2CVAL5   | R2CVAL4   | R2CVAL3   | R2CVAL2   | R2CVAL1  | R2CVAL0  | 0x74            |

|                                            | 10                  | P2CNTSREG     | P2CVAL7   | P2CVAL6   | P2CVAL5   | P2CVAL4   | P2CVAL3   | P2CVAL2   | P2CVAL1  | P2CVAL0  | 0x62            |

|                                            | 11                  | S2CNTSREG     | S2CVAL7   | S2CVAL6   | S2CVAL5   | S2CVAL4   | S2CVAL3   | S2CVAL2   | S2CVAL1  | S2CVAL0  | 0x32            |

|                                            | 12                  | PACONREG      | Reserved  | Reserved  | Reserved  | PARC1     | PARC0     | Reserved  | Reserved | Reserved | 0x38            |

|                                            | 13                  | FTXRXIREG     | IRQ0RXS1  | IRQ0RXS0  | IRQ1RXS1  | IRQ1RXS0  | TXIRQ1    | FIFOFULL  | FIFOMTY  | FOVRRUN  | 0x00            |

| Interrupt                                  | 14                  | FTPRIREG      | FIFOFM    | FIFOSC    | TXDONE    | TXSTIRQ0  | Reserved  | RIRQS     | LSTSPLL  | LENPLL   | 0x01            |

|                                            | 15                  | RSTHIREG      | RTIVAL7   | RTIVAL6   | RTIVAL5   | RTIVAL4   | RTIVAL3   | RTIVAL2   | RTIVAL1  | RTIVAL0  | 0x00            |

|                                            | 16                  | FILCONREG     | PASFILV3  | PASFILV2  | PASFILV1  | PASFILV0  | BUTFILV3  | BUTFILV2  | BUTFILV1 | BUTFILV0 | 0xA3            |

| Receiver                                   | 17                  | PFCONREG      | POLCFV3   | POLCFV2   | POLCFV1   | POLCFV0   | Reserved  | Reserved  | Reserved | Reserved | 0x38            |

|                                            | 18                  | SYNCREG       | POLFILEN  | BSYNCEN   | SYNCREN   | SYNCWSZ1  | SYNCWSZ0  | SYNCTEN1  | SYNCTEN0 | Reserved | 0x18            |

|                                            | 19                  | RESVREG       | Reserved  | Reserved  | Reserved  | Reserved  | Reserved  | Reserved  | Reserved | Reserved | 0x07            |

|                                            | 20                  | RSTSREG       | RSSIVAL7  | RSSIVAL6  | RSSIVAL5  | RSSIVAL4  | RSSIVAL3  | RSSIVAL2  | RSSIVAL1 | RSSIVAL0 | Read-only       |

|                                            | 21                  | OOKCREG       | OOKTHSV2  | OOKTHSV1  | OOKTHSV0  | OOKTHPV2  | OOKTHPV1  | OOKTHPV0  | OOKATHC1 | OOKATHC0 | 0x00            |

| Sync Word                                  | 22                  | SYNCV31REG    | SYNC1BV7  | SYNC1BV6  | SYNC1BV5  | SYNC1BV4  | SYNC1BV3  | SYNC1BV2  | SYNC1BV1 | SYNC1BV0 | 0x00            |

|                                            | 23                  | SYNCV23REG    | SYNC2BV7  | SYNC2BV6  | SYNC2BV5  | SYNC2BV4  | SYNC2BV3  | SYNC2BV2  | SYNC2BV1 | SYNC2BV0 | 0x00            |

|                                            | 24                  | SYNCV15REG    | SYNC3BV7  | SYNC3BV6  | SYNC3BV5  | SYNC3BV4  | SYNC3BV3  | SYNC3BV2  | SYNC3BV1 | SYNC3BV0 | 0x00            |

|                                            | 25                  | SYNCV07REG    | SYNC4BV7  | SYNC4BV6  | SYNC4BV5  | SYNC4BV4  | SYNC4BV3  | SYNC4BV2  | SYNC4BV1 | SYNC4BV0 | 0x00            |

| Transmitter                                | 26                  | TXPARCREG     | TXIPOLFV3 | TXIPOLFV2 | TXIPOLFV1 | TXIPOLFV0 | TXOPVAL2  | TXOPVAL1  | TXOPVAL0 | Reserved | 0x7C            |

| Clock-out                                  | 27                  | CLKOUTREG     | CLKOCNTRL | CLKOFREQ5 | CLKOFREQ4 | CLKOFREQ3 | CLKOFREQ2 | CLKOFREQ1 | Reserved | Reserved | 0xBC            |

| Packet                                     | 28                  | PLOADREG      | MCHSTREN  | PLDPLEN6  | PLDPLEN5  | PLDPLEN4  | PLDPLEN3  | PLDPLEN2  | PLDPLEN1 | PLDPLEN0 | 0x00            |

|                                            | 29                  | NADDSREG      | NLADDR7   | NLADDR6   | NLADDR5   | NLADDR4   | NLADDR3   | NLADDR2   | NLADDR1  | NLADDR0  | 0x00            |

|                                            | 30                  | PKTCREG       | PKTLENF   | PRESIZE1  | PRESIZE0  | WHITEN1   | CHKCRCEN  | ADDFIL1   | ADDFIL0  | STSCRCEN | 0x68            |

|                                            | 31                  | FCRCREG       | ACFCRC    | FRWAXS    | Reserved  | Reserved  | Reserved  | Reserved  | Reserved | Reserved | 0x00            |

## 3.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings(†)

| Ambient temperature under bias                                                           | 40°C to +85°C  |

|------------------------------------------------------------------------------------------|----------------|

| Storage temperature                                                                      | 55°C to +125°C |

| Lead temperature (soldering, max 10s)                                                    | +260°C         |

| Voltage on VDD with respect to Vss                                                       | 0.3V to 6V     |

| Voltage on any combined digital and analog pin with respect to Vss (except RFIO and VDD) |                |

| Voltage on open-collector outputs (RFIO) <sup>(1)</sup>                                  | 0.3V to 3.7V   |

| Input current into pin (except VDD and Vss)                                              | 25 mA to 25 mA |

| Electrostatic discharge with human body model                                            | 1000V          |

Note 1: At maximum, voltage on RFIO cannot be higher than 6V.

† **NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 3.1 ESD Notice

The MRF89XA is a high-performance radio frequency device. It satisfies:

- Class II of the JEDEC standard JESD22-A114-B (Human Body Model) of 2 KV, except on all of the RF pins where it satisfies Class 1A.

- Class III of the JEDEC standard JESD22-C101C (Charged Device Model) on all pins.

It should thus be handled with all the necessary ESD precautions to avoid any permanent damage.

TABLE 3-1: RECOMMENDED OPERATING CONDITIONS

| Parameter                                                     | Min       | Тур | Max       | Unit | Condition |

|---------------------------------------------------------------|-----------|-----|-----------|------|-----------|

| Ambient Operating Temperature                                 | -40       | _   | +85       | °C   | _         |

| Supply Voltage for RF, Analog and Digital Circuits            | 2.1       | _   | 3.6       | V    | _         |

| Supply Voltage for Digital I/O                                | 2.1       |     | 3.6       | V    | _         |

| Input High Voltage (VIH)                                      | 0.5 * VDD | _   | VDD + 0.3 | V    | _         |

| Input Low Voltage (VIL)                                       | -0.3V     | _   | 0.2 * VDD | V    | _         |

| DC Voltage on Open Collector Outputs (RFIO) <sup>(1,2)</sup>  | VDD - 1.5 | _   | VDD + 1.5 | V    | _         |

| AC Peak Voltage on Open Collector Outputs (IO) <sup>(1)</sup> | VDD - 1.5 | -   | VDD + 1.5 | V    | _         |

**Note 1:** At minimum, VDD – 1.5V should not be lower than 1.8V.

2: At maximum, VDD + 1.5V should not be higher than 3.7V.

TABLE 3-2: CURRENT CONSUMPTION<sup>(3)</sup>

| Chip Mode             | Min | Тур | Max | Unit | Condition                                      |

|-----------------------|-----|-----|-----|------|------------------------------------------------|

| Sleep                 | _   | 0.1 | 2   | μΑ   | Sleep clock disabled, all blocks disabled      |

| Idle                  | _   | 65  | 80  | μA   | Oscillator and baseband enabled <sup>(2)</sup> |

| Frequency Synthesizer | _   | 1.3 | 1.7 | mA   | Frequency synthesizer running                  |

| TX                    | _   | 25  | 30  | mA   | Output power = +10 dBm                         |

| TX                    | _   | 16  | 21  | mA   | Output power = +1 dBm <sup>(1)</sup>           |

| RX                    | _   | 3.0 | 3.5 | mA   | _                                              |

Note 1: Guaranteed by design and characterization.

2: Crystal CLOAD = 10 pF, C0 = 2.5 pF, RM = 15 Ohms.

**3:** Measurement Conditions: Temp = 25°C, VDD = 3.3V, crystal frequency = 12.8 MHz, carrier frequency = 869 or 915 MHz, modulation FSK, data rate = 25 kb/s, FDEV = 50 kHz, fc = 100 kHz, unless otherwise specified.

TABLE 3-3: DIGITAL I/O PIN INPUT SPECIFICATIONS(1)

| Symbol | Characteristic                           | Min       | Тур | Max       | Unit | Condition            |

|--------|------------------------------------------|-----------|-----|-----------|------|----------------------|

| VIL    | Input Low Voltage                        | _         | -   | 0.2 * VDD | V    | _                    |

| VIH    | Input High Voltage                       | 0.8 * VDD | _   | _         | V    | _                    |

| lıL    | Input Low Leakage Current <sup>(2)</sup> | -0.5      | _   | 0.5       | μA   | VIL = 0V             |

| Iн     | Input High Leakage Current               | -0.5      | _   | 0.5       | μA   | VIH = VDD, VDD = 3.7 |

| Vol    | Digital Low Output Voltage               | _         | _   | 0.1 * VDD | _    | IOL = 1 mA           |

| Voн    | Digital Low Output                       | 0.9 * VDD | ı   | _         | ٧    | IOH = -1 mA          |

- **Note 1:** Measurement Conditions: TA = 25°C, VDD = 3.3V, crystal frequency = 12.8 MHz, unless otherwise specified.

- 2: Negative current is defined as the current sourced by the pin.

- 3: On Pin 10 (OSC1) and 11 (OSC2), maximum voltages of 1.8V can be applied.

TABLE 3-4: PLL PARAMETERS AC CHARACTERISTICS(1)

| Parameter                                                                | Min  | Тур  | Max | Unit | Condition                            |

|--------------------------------------------------------------------------|------|------|-----|------|--------------------------------------|

| Frequency Ranges                                                         | 863  | _    | 870 | MHz  | Programmable but requires specific   |

|                                                                          | 902  | _    | 928 | MHz  | ВОМ                                  |

|                                                                          | 950  | _    | 960 | MHz  |                                      |

| Bit Rate (FSK)                                                           | 1.56 | _    | 200 | kb/s | NRZ                                  |

| Bit Rate (OOK)                                                           | 1.56 |      | 32  | kb/s | NRZ                                  |

| Frequency Deviation (FSK)                                                | 33   | 50   | 200 | kHz  | _                                    |

| Crystal Oscillator Frequency                                             | 9    | 12.8 | 15  | MHz  | _                                    |

| Frequency Synthesizer Step                                               |      | 2    |     | kHz  | Variable, depending on the frequency |

| Oscillator Wake-up Time                                                  | _    | 1.5  | 5   | ms   | From Sleep mode <sup>(1)</sup>       |

| Frequency Synthesizer Wake-up Time; at most, 10 kHz away from the Target |      | 500  | 800 | μs   | From Stand-by mode                   |

| Frequency Synthesizer Hop Time; at                                       | _    | 180  | _   | μs   | 200 kHz step                         |

| most, 10 kHz away from the Target                                        | _    | 200  | _   | μs   | 1 MHz step                           |

|                                                                          |      | 250  |     | μs   | 5 MHz step                           |

|                                                                          | _    | 260  | _   | μs   | 7 MHz step                           |

|                                                                          |      | 290  |     | μs   | 12 MHz step                          |

|                                                                          | _    | 320  | _   | μs   | 20 MHz step                          |

|                                                                          | _    | 340  | _   | μs   | 27 MHz step                          |

Note 1: Guaranteed by design and characterization

TABLE 3-5: RECEIVER AC CHARACTERISTICS<sup>(1)</sup>

| Parameter                                     | Min | Тур  | Max    | Unit | Condition                                                 |

|-----------------------------------------------|-----|------|--------|------|-----------------------------------------------------------|

| Sensitivity (FSK)                             | _   | -107 | _      | dBm  | 869 MHz, BR = 25 kb/s,<br>Fdev = 50 kHz, fc = 100 kHz     |

|                                               | _   | -103 | _      | dBm  | 869 MHz, BR = 66.7 kb/s,<br>Fdev = 100 kHz, fc = 200 kHz  |

|                                               | _   | -105 | _      | dBm  | 915 MHz, BR = 25 kb/s, Fdev = 50 kHz, fc = 100 kHz        |

|                                               | _   | -101 | _      | dBm  | 915 MHz, BR = 66.7 kb/s,<br>Fdev = 100 kHz, fc = 200 kHz  |

| Sensitivity (OOK)                             | _   | -113 | _      | dBm  | 869 MHz, 2kb/s NRZ<br>fc – fo = 50 kHz, fo = 50 kHz       |

|                                               | _   | -106 | _      | dBm  | 869 MHz, 16.7 kb/s NRZ<br>fc – fo = 100 kHz, fo = 100 kHz |

|                                               | _   | -111 | _      | dBm  | 915 MHz, 2 kb/s NRZ<br>fc – fo = 50 kHz, fo = 50 kHz      |

|                                               | _   | -105 | _      | dBm  | 915 MHz, 16.7 kb/s NRZ<br>fc – fo = 100 kHz, fo = 100 kHz |

| Co-Channel Rejection                          | _   | -12  | _      | dBc  | Modulation as wanted signal                               |

| Adjacent Channel Rejection                    | _   | 27   | _      | dB   | Offset = 300 kHz, unwanted tone is not modulated          |

|                                               | _   | 52   | _      | dB   | Offset = 600 kHz, unwanted tone is not modulated          |

|                                               | _   | 57   | _      | dB   | Offset = 1.2 MHz, unwanted tone is not modulated          |

| Blocking Immunity                             | _   | -48  | _      | dBm  | Offset = 1 MHz, unmodulated                               |

|                                               | _   | -37  | _      | dBm  | Offset = 2 MHz, unmodulated, no SAW                       |

|                                               | _   | -33  | _      | dBm  | Offset = 10 MHz, unmodulated, no SAW                      |

| Receiver Bandwidth in FSK Mode <sup>(2)</sup> | 50  | _    | 250    | kHz  | Single side BW, Polyphase Off                             |

| Receiver Bandwidth in OOK Mode <sup>(2)</sup> | 50  | _    | 400    | kHz  | Single side BW, Polyphase On                              |

| Input Third Order Intercept Point             | _   | -28  | _      | dBm  | Interferers at 1 MHz and 1.950 MHz offset                 |

| Receiver Wake-up Time                         | _   | 280  | 500    | μs   | From FS to RX ready                                       |

| Receiver Wake-up Time                         | _   | 600  | 900    | μs   | From Stand-by to RX ready                                 |

| Receiver Hop Time from RX                     | _   | 400  | _      | μs   | 200 kHz step                                              |

| Ready to RX Ready with a                      |     | 400  | _      | μs   | 1 MHz step                                                |

| Frequency Hop                                 | _   | 460  | _      | μs   | 5 MHz step                                                |

|                                               |     | 480  | _      | μs   | 7 MHz step                                                |

|                                               | _   | 520  | _      | μs   | 12 MHz step                                               |

|                                               | _   | 550  | _      | μs   | 20 MHz step                                               |

|                                               | _   | 600  | _      | μs   | 27 MHz step                                               |

| RSSI Sampling Time                            | _   | _    | 1/Fdev | S    | From RX ready                                             |

| RSSI Dynamic Range                            | _   | 70   | _      | dB   | Ranging from sensitivity                                  |

**Note 1:** Guaranteed by design and characterization.

<sup>2:</sup> This reflects the whole receiver bandwidth, as described by conditions for active and passive filters.

TABLE 3-6: TRANSMITTER AC CHARACTERISTICS<sup>(1)</sup>

| Description                   | Min | Тур   | Max | Unit   | Condition                                                                      |

|-------------------------------|-----|-------|-----|--------|--------------------------------------------------------------------------------|

| RF Output Power, Programmable | _   | +12.5 | _   | dBm    | Maximum power setting.                                                         |

| with 8 Steps of typ. 3 dB     | _   | -8.5  | _   | dBm    | Minimum power setting.                                                         |

| Phase Noise                   | _   | -112  | _   | dBc/Hz | Measured with a 600 kHz offset at the transmitter output.                      |

| Transmitted Spurious          | _   | _     | -47 | dBc    | At any offset between 200 kHz and 600 kHz, unmodulated carrier, Fdev = 50 kHz. |

| Transmitter Wake-up Time      | _   | 120   | 500 | μs     | From FS to TX ready.                                                           |

| Transmitter Wake-up Time      | _   | 600   | 900 | μs     | From standby to TX ready.                                                      |

Note 1: Guaranteed by design and characterization.

## 3.2 Timing Specification and Diagram

TABLE 3-7: SPI TIMING SPECIFICATION<sup>(1,2,3)</sup>

| Parameter                                                          | Min | Тур | Max | Unit | Condition |

|--------------------------------------------------------------------|-----|-----|-----|------|-----------|

| SPI Configure Clock Frequency                                      | _   | _   | 6   | MHz  | _         |

| SPI Data Clock Frequency                                           | _   | _   | 1   | MHz  | _         |

| Data Hold and Setup Time                                           | 2   | _   | _   | μs   | _         |

| SDI Setup Time for SPI Configure                                   | 250 | _   | _   | ns   | _         |

| SDI Setup Time for SPI Data                                        | 312 | _   | _   | ns   | _         |

| CSCON Low to SCK Rising Edge;<br>SCK Falling Edge to /CSCON High   | 500 | _   | _   | ns   | -         |

| CSDATA Low to SCK Rising Edge;<br>SCK Falling Edge to /CSDATA High | 625 | _   | _   | ns   | _         |

| CSCON Rising to Falling Edge                                       | 500 | _   | _   | ns   | _         |

| CSDATA Rising to Falling Edge                                      | 625 | _   | _   | ns   | _         |

**Note 1:** Typical Values: TA = 25°C, VDD = 3.3V, crystal frequency = 12.8 MHz, unless otherwise specified.

<sup>2:</sup> Negative current is defined as the current sourced by the pin.

<sup>3:</sup> On Pin 10 (OSC1) and 11 (OSC2), maximum voltages of 1.8V can be applied.

NOTES:

## APPENDIX A: REVISION HISTORY

## Revision A (January 2010)

This is the initial released version of this document.

NOTES:

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

- · Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| lo:  | Technical Publications Manager          | Total Pages Sent                                      |

|------|-----------------------------------------|-------------------------------------------------------|

| RE:  | Reader Response                         |                                                       |

| Fron | n: Name                                 |                                                       |

|      | • •                                     |                                                       |

|      |                                         |                                                       |

|      |                                         | FAV. (                                                |

| Annl | Telephone: ()<br>lication (optional):   | FAX: ()                                               |

|      | ıld you like a reply?YN                 |                                                       |

|      |                                         | "                                                     |

| Devi | ice: MRF89XA                            | Literature Number: DS70622A                           |

| Que  | stions:                                 |                                                       |

| 1. \ | What are the best features of this doc  | ument?                                                |

| -    |                                         |                                                       |

| -    |                                         |                                                       |

| 2. I | How does this document meet your ha     | ardware and software development needs?               |

| -    |                                         |                                                       |

| -    |                                         |                                                       |

| 3. I | Do you find the organization of this do | cument easy to follow? If not, why?                   |

| -    |                                         |                                                       |

|      |                                         |                                                       |

| 4.   | what additions to the document do yo    | u think would enhance the structure and subject?      |

| -    |                                         |                                                       |

| 5. \ | What deletions from the document co     | uld be made without affecting the overall usefulness? |

| J.   | what deletions from the document con    | aid be made without affecting the overall decidiness: |

| -    |                                         |                                                       |

| 6. I | Is there any incorrect or misleading in | formation (what and where)?                           |

| •    | is another any most containing in       |                                                       |

| -    |                                         |                                                       |

| 7. I | How would you improve this documen      | t?                                                    |

|      | · ·                                     |                                                       |

| -    |                                         |                                                       |

| -    |                                         |                                                       |

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO<br>Device    | $^ ^{\dagger}$ $^{\dagger}$                                       | Example:  a) MRF89XA-I/MQ: Industrial temperature, QFN package.  b) MRF89XAT-I/MQ: Industrial temperature, QFN package, tape and reel. |

|----------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Device               | MRF89XA: Ultra Low-Power, Integrated ISM Band Sub-GHz Transceiver |                                                                                                                                        |

| Temperature<br>Range | I = -40°C to +85°C (Industrial)                                   |                                                                                                                                        |

| Package              | MQ = QFN (Quad Flat, No Lead) T = Tape and Reel                   |                                                                                                                                        |

## WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

Corporate Office

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca. IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario, Canada

Tel: 905-673-0699

Fax: 905-673-6509

### **ASIA/PACIFIC**

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200

Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung

Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 **UK - Wokingham**

Tel: 44-118-921-5869 Fax: 44-118-921-5820

01/05/10

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Microchip: