# PI7C8152A & PI7C8152B 2-Port PCI-to-PCI Bridge REVISION 1.11

2380 Bering Drive, San Jose, CA 95131 Telephone: 1-877-PERICOM, (1-877-737-4266) Fax: 408-435-1100

Email: <a href="mailto:solutions@pericom.com">solutions@pericom.com</a>

Internet: <a href="http://www.pericom.com">http://www.pericom.com</a>

#### LIFE SUPPORT POLICY

Pericom Semiconductor Corporation's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of PSC.

- 1) Life support devices or system are devices or systems which:

- a) Are intended for surgical implant into the body or

- b) Support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2) A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Pericom Semiconductor Corporation reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. Pericom Semiconductor does not assume any responsibility for use of any circuitry described other than the circuitry embodied in a Pericom Semiconductor product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Pericom Semiconductor Corporation.

All other trademarks are of their respective companies.

# **REVISION HISTORY**

| Date     | Revision Number | Description                                                    |  |  |

|----------|-----------------|----------------------------------------------------------------|--|--|

| 08/13/03 | 0.01            | First draft of datasheet                                       |  |  |

| 08/14/03 | 0.02            | Revised bit[4] offset 48h                                      |  |  |

| 09/19/03 | 1.00            | Datasheet release to the web                                   |  |  |

|          |                 |                                                                |  |  |

|          |                 | Revised revision ID register bit[7:0] offset 08h from 0h to 1h |  |  |

| 09/25/03 | 1.10            | Added descriptions for 8152A synchronous device                |  |  |

|          |                 |                                                                |  |  |

|          |                 | Revised T <sub>DELAY</sub> in sections 14.4 and 14.5           |  |  |

|          |                 |                                                                |  |  |

|          |                 | Revised Power Consumption in section 14.7                      |  |  |

| 10/16/03 | 1.11            | Revised Product Description in section 1.                      |  |  |

|          |                 | •                                                              |  |  |

|          |                 | Revised pin description for S CLKIN in section 2.2.3.          |  |  |

|          |                 |                                                                |  |  |

|          |                 | Corrected Primary Clock Input description in section 9.1.      |  |  |

This page intentionally left blank.

# TABLE OF CONTENTS

| 1 | INTRO          | DUCTION                                                                           | 11 |

|---|----------------|-----------------------------------------------------------------------------------|----|

| 2 | SIGNA          | L DEFINITIONS                                                                     | 12 |

|   | 2.1 SIG        | NAL TYPES                                                                         | 12 |

|   |                | NALS                                                                              |    |

|   | 2.2.1          | PRIMARY BUS INTERFACE SIGNALS                                                     | 12 |

|   | 2.2.3          | CLOCK SIGNALS                                                                     |    |

|   | 2.2.4          | MISCELLANEOUS SIGNALS                                                             |    |

|   | 2.2.5          | POWER AND GROUND                                                                  |    |

|   |                | VLIST – 160-PIN MQFP                                                              |    |

| 3 | PCI BU         | S OPERATION                                                                       | 17 |

|   | 3.1 TY         | PES OF TRANSACTIONS                                                               | 17 |

|   | 3.2 SIN        | IGLE ADDRESS PHASE                                                                | 18 |

|   | 3.3 DU         | AL ADDRESS PHASE                                                                  | 18 |

|   | 3.4 DE         | VICE SELECT (DEVSEL_L) GENERATION                                                 | 19 |

|   |                | TA PHASE                                                                          |    |

|   | 3.6 WI         | RITE TRANSACTIONS                                                                 |    |

|   | 3.6.1          | MEMORY WRITE TRANSACTIONS                                                         |    |

|   | 3.6.2          | MEMORY WRITE AND INVALIDATE                                                       |    |

|   | 3.6.3          | DELAYED WRITE TRANSACTIONS                                                        |    |

|   | 3.6.4          | WRITE TRANSACTION ADDRESS BOUNDARIES                                              |    |

|   | 3.6.5          | BUFFERING MULTIPLE WRITE TRANSACTIONS                                             |    |

|   | 3.6.6          | FAST BACK-TO-BACK WRITE TRANSACTIONS                                              |    |

|   |                | AD TRANSACTIONS                                                                   |    |

|   | 3.7.1          | PREFETCHABLE READ TRANSACTIONS                                                    |    |

|   | 3.7.2          | NON-PREFETCHABLE READ TRANSACTIONS                                                |    |

|   | 3.7.3          | READ PREFETCH ADDRESS BOUNDARIES                                                  |    |

|   | 3.7.4          | DELAYED READ REQUESTS                                                             |    |

|   | 3.7.5          | DELAYED READ COMPLETION ON TARGET BUS                                             |    |

|   | 3.7.6          | DELAYED READ COMPLETION ON INITIATOR BUS                                          |    |

|   | 3.7.7          | FAST BACK-TO-BACK READ TRANSACTION                                                |    |

|   |                | NFIGURATION TRANSACTIONS                                                          |    |

|   | 3.8.1          | TYPE 0 ACCESS TO PI7C8152x                                                        |    |

|   | 3.8.2          | TYPE 1 TO TYPE 0 CONVERSION                                                       |    |

|   | 3.8.3          | TYPE 1 TO TYPE 1 FORWARDING                                                       |    |

|   | 3.8.4          | SPECIAL CYCLES                                                                    |    |

|   |                | ANSACTION TERMINATION                                                             |    |

|   |                |                                                                                   |    |

|   | 3.9.2<br>3.9.3 | MASTER ABORT RECEIVED BY PI7C8152xTARGET TERMINATION RECEIVED BY PI7C8152x        |    |

|   | 3.9.3<br>3.9.4 | TARGET TERMINATION RECEIVED BY PI7C8152XTARGET TERMINATION INITIATED BY PI7C8152X |    |

| 4 |                | CSS DECODING                                                                      |    |

|   |                | DRESS RANGES                                                                      |    |

|   |                | ADDRESS DECODING.                                                                 |    |

|   | 4.2.1          | I/O BASE AND LIMIT ADDRESS REGISTER                                               |    |

|   | 4.2.2          | ISA MODE                                                                          |    |

|   |                | MORY ADDRESS DECODING                                                             |    |

|   |                | MEMORY-MAPPED I/O BASE AND LIMIT ADDRESS REGISTERS                                |    |

|   |                | PREFETCHABLE MEMORY BASE AND LIMIT ADDRESS REGISTERS                              |    |

|    | 4.4 VG  | A SUPPORT                                               | 41 |

|----|---------|---------------------------------------------------------|----|

|    | 4.4.1   | VGA MODE                                                |    |

|    | 4.4.2   | VGA SNOOP MODE                                          | 42 |

| 5  | TRANS   | ACTION ORDERING                                         | 42 |

|    | 5.1 TR. | ANSACTIONS GOVERNED BY ORDERING RULES                   | 42 |

|    |         | NERAL ORDERING GUIDELINES                               |    |

|    |         | DERING RULES                                            |    |

|    |         | TA SYNCHRONIZATION                                      |    |

| 6  |         | HANDLING                                                |    |

| ·  |         | DRESS PARITY ERRORS                                     |    |

|    |         | TA PARITY ERRORS                                        |    |

|    | 6.2.1   | CONFIGURATION WRITE TRANSACTIONS TO CONFIGURATION SPACE |    |

|    | 6.2.2   | READ TRANSACTIONS                                       |    |

|    | 6.2.3   | DELAYED WRITE TRANSACTIONS                              | 48 |

|    | 6.2.4   | POSTED WRITE TRANSACTIONS                               |    |

|    | 6.3 DA  | TA PARITY ERROR REPORTING SUMMARY                       |    |

|    |         | STEM ERROR (SERR_L) REPORTING                           |    |

| 7  | EXCLU   | SIVE ACCESS                                             | 57 |

| /  |         |                                                         |    |

|    |         | NCURRENT LOCKS                                          |    |

|    |         | QUIRING EXCLUSIVE ACCESS ACROSS PI7C8152x               |    |

|    | 7.2.1   | LOCKED TRANSACTIONS IN DOWNSTREAM DIRECTION             |    |

|    | 7.2.2   | LOCKED TRANSACTION IN UPSTREAM DIRECTION                |    |

|    |         | DING EXCLUSIVE ACCESS                                   |    |

| 8  | PCI BU  | S ARBITRATION                                           | 60 |

|    |         | MARY PCI BUS ARBITRATION                                |    |

|    | 8.2 SEC | CONDARY PCI BUS ARBITRATION                             |    |

|    | 8.2.1   | SECONDARY BUS ARBITRATION USING THE INTERNAL ARBITER    |    |

|    | 8.2.2   | PREEMPTION                                              |    |

|    | 8.2.3   | SECONDARY BUS ARBITRATION USING AN EXTERNAL ARBITER     |    |

|    | 8.2.4   | BUS PARKING                                             |    |

| 9  | CLOCK   | S                                                       | 63 |

|    | 9.1 PRI | MARY CLOCK INPUT                                        | 63 |

|    | 9.2 SEC | CONDARY CLOCK OUTPUTS                                   | 63 |

|    | 9.3 AS  | YNCHRONOUS MODE (PI7C8152B ONLY)                        | 63 |

|    | 9.4 SY  | NCHRONOUS MODE                                          | 64 |

| 10 | 0 PCI P | OWER MANAGEMENT                                         | 64 |

| 1  | 1 DECE  | Т                                                       | 65 |

| 1. |         |                                                         |    |

|    |         | MARY INTERFACE RESET                                    |    |

|    |         | CONDARY INTERFACE RESET                                 |    |

|    | 11.3 CH | IP RESET                                                | 66 |

| 12 | 2 CONI  | FIGURATION REGISTERS                                    | 66 |

|    | 12.1 CO | NFIGURATION REGISTER                                    | 67 |

|    | 12.1.1  | VENDOR ID REGISTER – OFFSET 00h                         |    |

|    | 12.1.2  | DEVICE ID REGISTER - OFFSET 00h                         |    |

|    | 12.1.3  | COMMAND REGISTER - OFFSET 04h                           |    |

|    | 12.1.4  | PRIMARY STATUS REGISTER – OFFSET 04h                    | 69 |

| 12.1.5           | REVISION ID REGISTER – OFFSET 08h                                                                                   | 70  |

|------------------|---------------------------------------------------------------------------------------------------------------------|-----|

| 12.1.6           | CLASS CODE REGISTER – OFFSET 08h                                                                                    | 70  |

| 12.1.7           | CACHE LINE SIZE REGISTER – OFFSET OCh                                                                               | 70  |

| 12.1.8           | PRIMARY LATENCY TIMER REGISTER – OFFSET 0Ch                                                                         | 70  |

| 12.1.9           | HEADER TYPE REGISTER – OFFSET OCh                                                                                   |     |

| 12.1.10          | PRIMARY BUS NUMBER REGISTSER – OFFSET 18h                                                                           |     |

| 12.1.11          | SECONDARY BUS NUMBER REGISTER – OFFSET 18h                                                                          |     |

| 12.1.12          | SUBORDINATE BUS NUMBER REGISTER – OFFSET 18h                                                                        |     |

| 12.1.13          | SECONDARY LATENCY TIMER REGISTER – OFFSET 18h                                                                       |     |

| 12.1.14          | I/O BASE ADDRESS REGISTER – OFFSET 1Ch                                                                              |     |

| 12.1.15          | I/O LIMIT ADDRESS REGISTER – OFFSET 1Ch                                                                             |     |

| 12.1.16          | SECONDARY STATUS REGISTER - OFFSET 1Ch                                                                              |     |

| 12.1.17          | MEMORY BASE ADDRESS REGISTER – OFFSET 20h                                                                           |     |

| 12.1.17          | MEMORY LIMIT ADDRESS REGISTER - OFFSET 20h                                                                          |     |

| 12.1.19          | PEFETCHABLE MEMORY BASE ADDRESS REGISTER – OFFSET 24h                                                               |     |

| 12.1.19          | PREFETCHABLE MEMORY LIMIT ADDRESS REGISTER – OF FSET 24h                                                            |     |

| 12.1.20          | PREFETCHABLE MEMORY BASE ADDRESS REGISTER – OF FSET 2411  PREFETCHABLE MEMORY BASE ADDRESS UPPER 32-BITS REGISTER – |     |

|                  | T 28h                                                                                                               |     |

|                  | PREFETCHABLE MEMORY LIMIT ADDRESS UPPER 32-BITS REGISTER -                                                          |     |

| 12.1.22<br>OFFSE |                                                                                                                     |     |

|                  | T 2Ch                                                                                                               |     |

| 12.1.23          | I/O BASE ADDRESS UPPER 16-BITS REGISTER – OFFSET 30h                                                                |     |

| 12.1.24          | I/O LIMIT ADDRESS UPPER 16-BITS REGISTER – OFFSET 30h                                                               |     |

| 12.1.25          | ECP POINTER REGISTER – OFFSET 34h                                                                                   |     |

| 12.1.26          | INTERRUPT PIN REGISTER – OFFSET 3Ch                                                                                 |     |

| 12.1.27          | BRIDGE CONTROL REGISTER - OFFSET 3Ch                                                                                |     |

| 12.1.28          | DIAGNOSTIC / CHIP CONTROL REGISTER – OFFSET 40h                                                                     |     |

| 12.1.29          | ARBITER CONTROL REGISTER – OFFSET 40h                                                                               |     |

| 12.1.30          | EXTENDED CHIP CONTROL REGISTER – OFFSET 48h                                                                         |     |

| 12.1.31          | SECONDARY BUS ARBITER PREEMPTION CONTROL REGISTER – OFFSE                                                           |     |

| 4Ch              |                                                                                                                     |     |

| 12.1.32          | P_SERR_L EVENT DISABLE REGISTER – OFFSET 64h                                                                        |     |

| 12.1.33          | SECONDARY CLOCK CONTROL REGISTER – OFFSET 68h                                                                       |     |

| 12.1.34          | P_SERR_L STATUS REGISTER – OFFSET 68h                                                                               |     |

| 12.1.35          | PORT OPTION REGISTER – OFFSET 74h                                                                                   |     |

| 12.1.36          | PRIMARY MASTER TIMEOUT COUNTER - OFFSET 80h                                                                         |     |

| 12.1.37          | SECONDARY MASTER TIMEOUT COUNTER - OFFSET 80h                                                                       | 84  |

| 12.1.38          | CAPABILITY ID REGISTER – OFFSET DCh                                                                                 | 84  |

| 12.1.39          | NEXT ITEM POINTER REGISTER – OFFSET DCh                                                                             |     |

| 12.1.40          | POWER MANAGEMENT CAPABILITIES REGISTER – OFFSET DCh                                                                 | 84  |

| 12.1.41          | POWER MANAGEMENT DATA REGISTER - OFFSET E0h                                                                         | 84  |

| 12.1.42          | PPB SUPPORT EXTENSIONS REGISER - OFFSET E0h                                                                         | 85  |

| 12 BBIB          | CE DELLA MOD                                                                                                        | 0.5 |

| 13 BRID          | GE BEHAVIOR                                                                                                         | 85  |

| 13.1 BR          | IDGE ACTIONS FOR VARIOUS CYCLE TYPES                                                                                | 85  |

|                  | NORMAL TERMINATION (INITIATED BY BRIDGE MASTER)                                                                     |     |

| 13.2.1           | MASTER ABORT                                                                                                        |     |

|                  | PARITY AND ERROR REPORTING                                                                                          |     |

|                  | REPORTING PARITY ERRORS                                                                                             |     |

| 13.2.4           |                                                                                                                     |     |

|                  |                                                                                                                     |     |

| 14 ELEC          | CTRICAL AND TIMING SPECIFICATIONS                                                                                   | 87  |

|                  |                                                                                                                     |     |

| 14.1 MA          | XIMUM RATINGS                                                                                                       | 27  |

|                  | XIMUM RATINGS                                                                                                       |     |

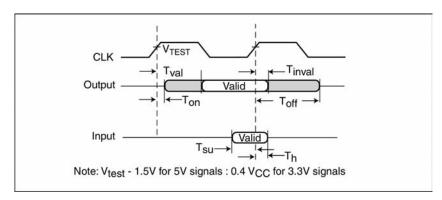

| 14.4 66MHZ PCI SIGNALING TIMING                                       | 88 |

|-----------------------------------------------------------------------|----|

| 14.5 33MHZ PCI SIGNALING TIMING                                       | 88 |

| 14.6 RESET TIMING                                                     | 88 |

| 14.7 POWER CONSUMPTION                                                | 89 |

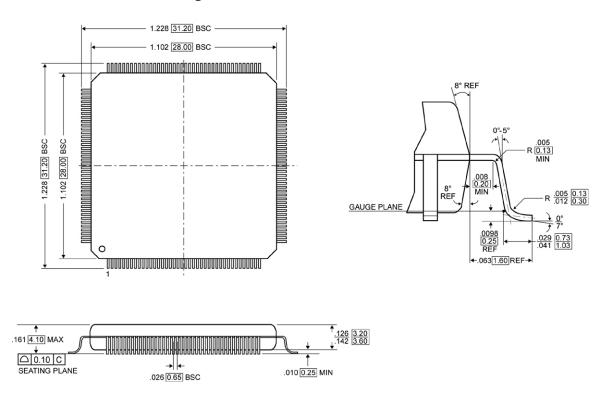

| 15 PACKAGE INFORMATION                                                | 89 |

| 15.1 160-PIN MQFP PACKAGE DIAGRAM                                     | 89 |

| 15.2 PART NUMBER ORDERING INFORMATION                                 |    |

|                                                                       |    |

| LIST OF TABLES                                                        |    |

|                                                                       |    |

| Table 2-1 PIN LIST – 160-PIN MQFP                                     | 16 |

| Table 3-1 PCI TRANSACTIONS                                            |    |

| Table 3-2 WRITE TRANSACTION FORWARDING                                |    |

| Table 3-3 WRITE TRANSACTION DISCONNECT ADDRESS BOUNDARIES             |    |

| Table 3-4 READ PREFETCH ADDRESS BOUNDARIES                            |    |

| Table 3-5 READ TRANSACTION PREFETCHING                                |    |

| Table 3-6 DEVICE NUMBER TO IDSEL S_AD PIN MAPPING                     |    |

| Table 3-7 DELAYED WRITE TARGET TERMINATION RESPONSE                   |    |

| Table 3-8 RESPONSE TO POSTED WRITE TARGET TERMINATION                 |    |

| Table 3-9 RESPONSE TO DELAYED READ TARGET TERMINATIOIN                |    |

| Table 5-1 SUMMARY OF TRANSACTION ORDERING                             |    |

| Table 6-1 SETTING THE PRIMARY INTERFACE DETECTED PARITY ERROR BIT     |    |

| Table 6-2 SETTING SECONDARY INTERFACE DETECTED PARITY ERROR BIT       | 52 |

| Table 6-3 SETTING PRIMARY BUS MASTER DATA PARITY ERROR DETECTED BIT   |    |

| Table 6-4 SETTING SECONDARY BUS MASTER DATA PARITY ERROR DETECTED BIT | 54 |

| Table 6-5 ASSERTION OF P_PERR_L                                       | 54 |

| Table 6-6 ASSERTION OF S PERR L                                       | 55 |

| Table 6-7 ASSERTION OF P SERR L FOR DATA PARITY ERRORS                | 55 |

| Table 10-1 POWER MANAGEMENT TRANSITIONS                               | 64 |

| LIST OF FIGURES                                                       |    |

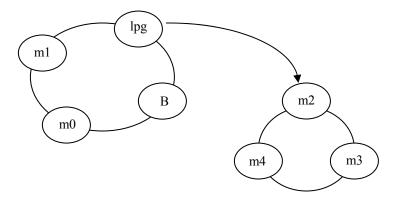

| Figure 8-1 SECONDARY ARBITER EXAMPLE                                  | 61 |

| Figure 14-1 PCI SIGNAL TIMING MEASUREMENT CONDITIONS                  |    |

| Figure 15-1 160-PIN MOFP PACKAGE OUTLINE                              |    |

| 1 ISW C 15 1 100 1 II VIIQI 1 ACKAOL OUTLINE                          | 09 |

This page intentionally left blank.

This page intentionally left blank.

## 1 INTRODUCTION

#### **Product Description**

The PI7C8152A and PI7C8152B (PI7C8152x) are Pericom Semiconductor's PCI-to-PCI Bridge that are designed to be fully compliant with the 32-bit, 66MHz implementation of the *PCI Local Bus Specification, Revision 2.2.* The PI7C8152B supports both synchronous and asynchronous bus transactions between devices on the Primary Bus and the Secondary Buses operating up to 66MHz. The PI7C8152A supports synchronous transactions only. In synchronous mode, both buses must operate at the same frequency. The Primary and Secondary Bus can also operate in concurrent mode, resulting in added increase in system performance.

#### **Product Features**

- 32-bit Primary and Secondary Ports run up to 66MHz

- Compliant with the PCI Local Bus Specification, Revision 2.2

- Compliant with PCI-to-PCI Bridge Architecture Specification, Revision 1.1.

- All I/O and memory commands

- Type 1 to Type 0 configuration conversion

- Type 1 to Type 1 configuration forwarding

- Type 1 configuration write to special cycle conversion

- Compliant with the Advanced Configuration Power Interface (ACPI) Specification.

- Compliant with the PCI Power Management Specification, Revision 1.1.

- Synchronous and Asynchronous operation support

- Supported modes of Asynchronous operation (PI7C8152B ONLY)

| Primary        | Secondary      |

|----------------|----------------|

| 25MHz to 66MHz | 25MHz to 66MHz |

- Supported modes of Synchronous operation

| Primary | Secondary |

|---------|-----------|

| 66MHz   | 66MHz     |

| 50MHz   | 50MHz     |

| 33MHz   | 33MHz     |

| 25MHz   | 25MHz     |

- Provides internal arbitration for four secondary bus masters

- Programmable 2-level priority arbiter

- Disable control for use of external arbiter

- Supports posted write buffers in all directions

- Four 128 byte FIFO's for delay transactions

- Two 128 byte FIFO's for posted memory transactions

- Enhanced address decoding

- 32-bit I/O address range

- 32-bit memory-mapped I/O address range

- 64-bit prefetchable address range

- ISA-aware mode for legacy support in the first 64KB of I/O address range

- Extended commercial temperature range 0°C to 85°C

- 3.3V core; 3.3V and 5V signaling

- 160-pin MQFP package

# 2 SIGNAL DEFINITIONS

# 2.1 Signal Types

| Signal Type | Description                                                                 |

|-------------|-----------------------------------------------------------------------------|

| I           | Input Only                                                                  |

| 0           | Output Only                                                                 |

| P           | Power                                                                       |

| TS          | Tri-State bi-directional                                                    |

| STS         | Sustained Tri-State. Active LOW signal must be pulled HIGH for 1 cycle when |

|             | deasserting.                                                                |

| OD          | Open Drain                                                                  |

# 2.2 Signals

Note: Signal names that end with "\_L" are active LOW.

## 2.2.1 PRIMARY BUS INTERFACE SIGNALS

| Name       | Pin #                                                                                                                                          | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_AD[31:0] | 70, 72, 73, 74, 76, 77, 78, 79, 84, 85, 87, 88, 89, 91, 92, 93, 109, 110, 111, 113, 114, 115, 117, 118, 123, 124, 126, 127, 129, 130, 132, 133 | TS   | Primary Address / Data: Multiplexed address and data bus. Address is indicated by P_FRAME_L assertion. Write data is stable and valid when P_IRDY_L is asserted and read data is stable and valid when P_TRDY_L is asserted. Data is transferred on rising clock edges when both P_IRDY_L and P_TRDY_L are asserted. During bus idle, PI7C8152x drives P_AD to a valid logic level when P_GNT_L is asserted.                                                                                                                                                                                          |

| P_CBE[3:0] | 82, 95, 107, 122                                                                                                                               | TS   | Primary Command/Byte Enables: Multiplexed command field and byte enable field. During address phase, the initiator drives the transaction type on these pins. After that, the initiator drives the byte enables during data phases. During bus idle, PI7C8152x drives P_CBE[3:0] to a valid logic level when P_GNT_L is asserted.                                                                                                                                                                                                                                                                     |

| P_PAR      | 106                                                                                                                                            | TS   | Primary Parity. Parity is even across P_AD[31:0], P_CBE[3:0], and P_PAR (i.e. an even number of 1's). P_PAR is an input and is valid and stable one cycle after the address phase (indicated by assertion of P_FRAME_L) for address parity. For write data phases, P_PAR is an input and is valid one clock after P_IRDY_L is asserted. For read data phase, P_PAR is an output and is valid one clock after P_TRDY_L is asserted. Signal P_PAR is tri-stated one cycle after the P_AD lines are tri-stated. During bus idle, PI7C8152x drives P_PAR to a valid logic level when P_GNT_L is asserted. |

| P_FRAME_L  | 96                                                                                                                                             | STS  | Primary FRAME (Active LOW). Driven by the initiator of a transaction to indicate the beginning and duration of an access. The de-assertion of P_FRAME_L indicates the final data phase requested by the initiator. Before being tri-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                        |

#### PI7C8152A & PI7C8152B 2-PORT PCI-TO-PCI BRIDGE ADVANCE INFORMATION

| Name       | Pin # | Type | Description                                                                                                            |

|------------|-------|------|------------------------------------------------------------------------------------------------------------------------|

| P_IRDY_L   | 97    | STS  | Primary IRDY (Active LOW). Driven by the initiator                                                                     |

|            |       |      | of a transaction to indicate its ability to complete current                                                           |

|            |       |      | data phase on the primary side. Once asserted in a data                                                                |

|            |       |      | phase, it is not de-asserted until the end of the data                                                                 |

|            |       |      | phase. Before tri-stated, it is driven to a de-asserted state                                                          |

| D TDDV I   | 99    | STS  | for one cycle.  Primary TRDV (Active LOW) Driven by the target of                                                      |

| P_TRDY_L   | 99    | 515  | <b>Primary TRDY (Active LOW).</b> Driven by the target of                                                              |

|            |       |      | a transaction to indicate its ability to complete current data phase on the primary side. Once asserted in a data      |

|            |       |      | phase, it is not de-asserted until the end of the data                                                                 |

|            |       |      | phase. Before tri-stated,                                                                                              |

|            |       |      | it is driven to a de-asserted state for one cycle.                                                                     |

| P_DEVSEL_L | 100   | STS  | Primary Device Select (Active LOW). Asserted by the                                                                    |

|            |       |      | target indicating that the device is accepting the                                                                     |

|            |       |      | transaction. As a master, PI7C8152x waits for the                                                                      |

|            |       |      | assertion of this signal within 5 cycles of P_FRAME_L                                                                  |

|            |       |      | assertion; otherwise, terminate with master abort. Before                                                              |

|            |       |      | tri-stated, it is driven to a                                                                                          |

| P STOP L   | 101   | I    | de-asserted state for one cycle.  Primary STOP (Active LOW). Asserted by the target                                    |

| 1_5101_L   | 101   | 1    | indicating that the target is requesting the initiator to stop                                                         |

|            |       |      | the current transaction. Before tri-stated, it is driven to a                                                          |

|            |       |      | de-asserted state for one cycle.                                                                                       |

| P_LOCK_L   | 102   | STS  | Primary LOCK (Active LOW). Asserted by an                                                                              |

|            |       |      | initiator, one clock cycle after the first address phase of a                                                          |

|            |       |      | transaction, attempting to perform an operation that may                                                               |

|            |       |      | take more than one PCI transaction to complete.                                                                        |

| P_IDSEL    | 83    | I    | Primary ID Select. Used as a chip select line for Type                                                                 |

|            |       |      | 0 configuration access to PI7C8152x configuration                                                                      |

| P_PERR_L   | 104   | CTC  | space.                                                                                                                 |

| P_PERK_L   | 104   | STS  | <b>Primary Parity Error (Active LOW).</b> Asserted when a data parity error is detected for data received on the       |

|            |       |      | primary interface. Before being tri-stated, it is driven to                                                            |

|            |       |      | a de-asserted state for one cycle.                                                                                     |

| P SERR L   | 105   | OD   | Primary System Error (Active LOW). Can be driven                                                                       |

|            |       |      | LOW by any device to indicate a system error condition.                                                                |

|            |       |      | PI7C8152x drives this pin on:                                                                                          |

|            |       |      | <ul> <li>Address parity error</li> </ul>                                                                               |

|            |       |      | Posted write data parity error on target bus                                                                           |

|            |       |      | Secondary S_SERR_L asserted     Meater short during neeted write transaction                                           |

|            |       |      | <ul> <li>Master abort during posted write transaction</li> <li>Target abort during posted write transaction</li> </ul> |

|            |       |      | Posted write transaction discarded                                                                                     |

|            |       |      | Delayed write request discarded                                                                                        |

|            |       |      | Delayed read request discarded                                                                                         |

|            |       |      | <ul> <li>Delayed transaction master timeout</li> </ul>                                                                 |

|            |       |      | This signal requires an external pull-up resistor for                                                                  |

|            |       |      | proper operation.                                                                                                      |

| P_REQ_L    | 69    | TS   | Primary Request (Active LOW): This is asserted by                                                                      |

|            |       |      | PI7C8152x to indicate that it wants to start a transaction                                                             |

|            |       |      | on the primary bus. PI7C8152x de-asserts this pin for at                                                               |

| P_GNT_L    | 68    | I    | least 2 PCI clock cycles before asserting it again.  Primary Grant (Active LOW): When asserted.                        |

| 1_GN1_L    | 00    | 1    | PI7C8152x can access the primary bus. During idle and                                                                  |

|            |       |      | P GNT L asserted, PI7C8152x will drive P AD,                                                                           |

|            |       |      | P CBE, and P PAR to valid logic levels.                                                                                |

| P_RESET_L  | 64    | I    | Primary RESET (Active LOW): When P_RESET_L is                                                                          |

|            |       |      | active, all PCI signals should be asynchronously tri-                                                                  |

|            |       |      | stated.                                                                                                                |

# 2.2.2 SECONDARY BUS INTERFACE SIGNALS

| Name        | Pin #               | Type | Description                                                                                                              |

|-------------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------|

| S_AD[31:0]  | 36, 35, 33, 32, 31, | TS   | Secondary Address/Data: Multiplexed address and data                                                                     |

|             | 29, 28, 26, 24, 22, |      | bus. Address is indicated by S_FRAME_L assertion.                                                                        |

|             | 21, 20, 18, 17, 16, |      | Write data is stable and valid when S_IRDY_L is                                                                          |

|             | 14, 156, 155, 153,  |      | asserted and read data is stable and valid when                                                                          |

|             | 152, 150, 149,      |      | S_IRDY_L is asserted. Data is transferred on rising                                                                      |

|             | 148, 146, 144,      |      | clock edges when both S_IRDY_L and S_TRDY_L are                                                                          |

|             | 142, 141, 140,      |      | asserted. During bus idle, PI7C8152x drives S_AD to a                                                                    |

|             | 138, 137, 136, 134  |      | valid logic level when S_GNT_L is asserted                                                                               |

|             |                     |      | respectively.                                                                                                            |

| S_CBE[3:0]  | 25, 13, 158, 145    | TS   | Secondary Command/Byte Enables: Multiplexed                                                                              |

|             |                     |      | command field and byte enable field. During address                                                                      |

|             |                     |      | phase, the initiator drives the transaction type on these                                                                |

|             |                     |      | pins. The initiator then drives the byte enables during                                                                  |

|             |                     |      | data phases. During bus idle, PI7C8152x drives                                                                           |

|             |                     |      | S_CBE[3:0] to a valid logic level when the internal grant                                                                |

| S PAR       | 2                   | TS   | is asserted.  Secondary Parity: Parity is even across S AD[31:0],                                                        |

| S_FAK       | 2                   | 13   | S CBE[3:0], and S PAR (i.e. an even number of 1's).                                                                      |

|             |                     |      | S PAR is an input and is valid and stable one cycle after                                                                |

|             |                     |      | the address phase (indicated by assertion of                                                                             |

|             |                     |      | S FRAME L) for address parity. For write data phases,                                                                    |

|             |                     |      | S PAR is an input and is valid one clock after                                                                           |

|             |                     |      | S IRDY L is asserted. For read data phase, S PAR is                                                                      |

|             |                     |      | an output and is valid one clock after S_TRDY_L is                                                                       |

|             |                     |      | asserted. Signal S_PAR is tri-stated one cycle after the                                                                 |

|             |                     |      | S_AD lines are tri-stated. During bus idle, PI7C8152x                                                                    |

|             |                     |      | drives S_PAR to a valid logic level when the internal                                                                    |

|             |                     |      | grant is asserted.                                                                                                       |

| S_FRAME_L   | 11                  | STS  | Secondary FRAME (Active LOW): Driven by the                                                                              |

|             |                     |      | initiator of a transaction to indicate the beginning and                                                                 |

|             |                     |      | duration of an access. The de-assertion of S_FRAME_L                                                                     |

|             |                     |      | indicates the final data phase requested by the initiator.                                                               |

|             |                     |      | Before being tri-stated, it is driven to a de-asserted state for one cycle.                                              |

| S_IRDY_L    | 10                  | STS  | Secondary IRDY (Active LOW): Driven by the                                                                               |

| S_IKD1_L    | 10                  | 313  | initiator of a transaction to indicate its ability to                                                                    |

|             |                     |      | complete current data phase on the secondary side. Once                                                                  |

|             |                     |      | asserted in a data phase, it is not de-asserted until the end                                                            |

|             |                     |      | of the data phase. Before tri-stated, it is driven to a de-                                                              |

|             |                     |      | asserted state for one cycle.                                                                                            |

| S_TRDY_L    | 9                   | STS  | Secondary TRDY (Active LOW): Driven by the target                                                                        |

|             |                     |      | of a transaction to indicate its ability to complete current                                                             |

|             |                     |      | data phase on the secondary side. Once asserted in a                                                                     |

|             |                     |      | data phase, it is not de-asserted until the end of the data                                                              |

|             |                     |      | phase. Before tri-stated, it is driven to a de-asserted state                                                            |

| a periary y | 7                   | ama  | for one cycle.                                                                                                           |

| S_DEVSEL_L  | 7                   | STS  | Secondary Device Select (Active LOW): Asserted by                                                                        |

|             |                     |      | the target indicating that the device is accepting the                                                                   |

|             |                     |      | transaction. As a master, PI7C8152x waits for the                                                                        |

|             |                     |      | assertion of this signal within 5 cycles of S_FRAME_L                                                                    |

|             |                     |      | assertion; otherwise, terminate with master abort. Before tri-stated, it is driven to a de-asserted state for one cycle. |

| S STOP L    | 6                   | STS  | Secondary STOP (Active LOW): Asserted by the                                                                             |

| 5_5101_L    |                     | 515  | target indicating that the target is requesting the initiator                                                            |

|             |                     |      | to stop the current transaction. Before tri-stated, it is                                                                |

|             |                     |      | driven to a de-asserted state for one cycle.                                                                             |

| S_LOCK_L    | 5                   | STS  | Secondary LOCK (Active LOW): Asserted by an                                                                              |

|             | -                   | -10  | initiator, one clock cycle after the first address phase of a                                                            |

|             |                     |      | transaction, when it is propagating a locked transaction                                                                 |

|             |                     |      | downstream. PI7C8152x does not propagate locked                                                                          |

|             |                     |      | transactions upstream.                                                                                                   |

|             |                     |      | •                                                                                                                        |

#### PI7C8152A & PI7C8152B 2-PORT PCI-TO-PCI BRIDGE ADVANCE INFORMATION

| Name         | Pin #          | Type | Description                                                                                                                                                                                                                                                                                                  |

|--------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_PERR_L     | 4              | STS  | Secondary Parity Error (Active LOW): Asserted when a data parity error is detected for data received on the secondary interface. Before being tri-stated, it is driven to a de-asserted state for one cycle.                                                                                                 |

| S_SERR_L     | 3              | I    | Secondary System Error (Active LOW): Can be driven LOW by any device to indicate a system error condition.                                                                                                                                                                                                   |

| S_REQ_L[3:0] | 42, 39, 38, 37 | I    | Secondary Request (Active LOW): This is asserted by an external device to indicate that it wants to start a transaction on the secondary bus. The input is externally pulled up through a resistor to VDD.                                                                                                   |

| S_GNT_L[3:0] | 47, 45, 44, 43 | TS   | Secondary Grant (Active LOW): PI7C8152x asserts these pins to allow external masters to access the secondary bus. PI7C8152x de-asserts these pins for at least 2 PCI clock cycles before asserting it again. During idle and S_GNT_L deasserted, PI7C8152x will drive S_AD, S_CBE, and S_PAR.                |

| S_RESET_L    | 48             | O    | Secondary RESET (Active LOW): Asserted when any of the following conditions are met:  1. Signal P_RESET_L is asserted.  2. Secondary reset bit in bridge control register in configuration space is set.  When asserted, all control signals are tri-stated and zeroes are driven on S_AD, S_CBE, and S_PAR. |

| S_CFN_L      | 49             | I    | Secondary Bus Central Function Control Pin: When tied LOW, it enables the internal arbiter. When tied HIGH, an external arbiter must be used. S_REQ_L[0] is reconfigured to be the secondary bus grant input, and S_GNT_L[0] is reconfigured to be the secondary bus request output.                         |

# 2.2.3 CLOCK SIGNALS

| Name          | Pin #              | Type | Description                                                                                                                                                                                                              |

|---------------|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_CLK         | 66                 | I    | Primary Clock Input: Provides timing for all                                                                                                                                                                             |

|               |                    |      | transactions on the primary interface.                                                                                                                                                                                   |

| S_CLKIN       | 51                 | I    | Secondary Clock Input: Provides timing for all                                                                                                                                                                           |

|               |                    |      | transactions on the secondary interface.                                                                                                                                                                                 |

| S_CLKOUT[4:0] | 61, 59, 57, 55, 53 | О    | <b>Secondary Clock Output:</b> Provides secondary clocks phase synchronous with the P_CLK.                                                                                                                               |

|               |                    |      | In synchronous mode, one of the clock outputs must be fed back to S_CLKIN. Unused outputs may be disabled by:  1. Writing the secondary clock disable bits in the configuration space  2. Terminating them electrically. |

|               |                    |      | In asynchronous mode, these pins may not be used.  Devices on the secondary interface should use the same clock source that is used for S CLKIN.                                                                         |

# 2.2.4 MISCELLANEOUS SIGNALS

| Name  | Pin # | Type | Description                                                                                                                                                                                                                |

|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_VIO | 67    | Ĭ    | Primary I/O Voltage: This pin is used to determine either 3.3V or 5V signaling on the primary bus. P_VIO must be tied to 3.3V only when all devices on the primary bus use 3.3V signaling. Otherwise, P_VIO is tied to 5V. |

### PI7C8152A & PI7C8152B 2-PORT PCI-TO-PCI BRIDGE ADVANCE INFORMATION

| S_VIO     | 52  | I   | Secondary I/O Voltage: This pin is used to determine either 3.3V or 5V signaling on the secondary bus. S_VIO must be tied to 3.3V only when all devices on the secondary bus use 3.3V signaling. Otherwise, S_VIO is tied to 5V.                                                                                                                                                                                      |

|-----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ВРССЕ     | 159 | I   | Bus/Power Clock Control Management Pin: When this pin is tied HIGH and the PI7C8152x is placed in the D2 or D3 <sub>HOT</sub> power state, it enables the PI7C8152x to place the secondary bus in the B2 power state. The secondary clocks are disabled and driven to 0. When this pin is tied LOW, there is no effect on the secondary bus clocks when the PI7C8152x enters the D2 or D3 <sub>HOT</sub> power state. |

| SCAN_EN   | 62  | I/O | Full-Scan Enable Control: When SCAN_EN is LOW, full-scan is in shift operation. When SCAN_EN_H is HIGH, full-scan is in parallel operation. If SCAN_TM_L is HIGH, SCAN_EN is an output with logic 0. For normal operation, SCAN_TM_L should be pulled HIGH and SCAN_EN becomes an output.                                                                                                                             |

| SCAN_TM_L | 63  | I   | Full-Scan Teset Mode Enable: When SCAN_TM_L is active (LOW), the scan chains will be enabled. For normal operation, pull SCAN_TM_L to HIGH.                                                                                                                                                                                                                                                                           |

## 2.2.5 POWER AND GROUND

| Name | Pin #               | Type | Description                 |

|------|---------------------|------|-----------------------------|

| VDD  | 8, 15, 23, 30, 40,  | P    | Power: +3.3V Digital power. |

|      | 46, 56, 60, 75, 80, |      |                             |

|      | 90, 98, 108, 116,   |      |                             |

|      | 120, 125, 131,      |      |                             |

|      | 139, 147, 154, 160  |      |                             |

| VSS  | 1, 12, 19, 27, 34,  | P    | Ground: Digital ground.     |

|      | 41, 50, 54, 58, 65, |      |                             |

|      | 71, 81, 86, 94,     |      |                             |

|      | 103, 112, 119,      |      |                             |

|      | 121, 128, 135,      |      |                             |

|      | 143, 151, 157       |      |                             |

# 2.3 PIN LIST – 160-PIN MQFP

Table 2-1 PIN LIST – 160-PIN MQFP

| Pin<br>Number | Name       | Туре | Pin<br>Number | Name       | Type | Pin<br>Number | Name       | Type |

|---------------|------------|------|---------------|------------|------|---------------|------------|------|

| 1             | VSS        | P    | 2             | S_PAR      | TS   | 3             | S_SERR_L   | I    |

| 4             | S_PERR_L   | STS  | 5             | S_LOCK_L   | STS  | 6             | S_STOP_L   | STS  |

| 7             | S_DEVSEL_L | STS  | 8             | VDD        | P    | 9             | S_TRDY_L   | STS  |

| 10            | S_IRDY_L   | STS  | 11            | S_FRAME_L  | STS  | 12            | VSS        | P    |

| 13            | S_CBE_L[2] | TS   | 14            | S_AD[16]   | TS   | 15            | VDD        | P    |

| 16            | S_AD[17]   | TS   | 17            | S_AD[18]   | TS   | 18            | S_AD[19]   | TS   |

| 19            | VSS        | P    | 20            | S_AD[20]   | TS   | 21            | S_AD[21]   | TS   |

| 22            | S_AD[22]   | TS   | 23            | VDD        | P    | 24            | S_AD[23]   | TS   |

| 25            | S_CBE_L[3] | TS   | 26            | S_AD[24]   | TS   | 27            | VSS        | P    |

| 28            | S_AD[25]   | TS   | 29            | S_AD[26]   | TS   | 30            | VDD        | P    |

| 31            | S_AD[27]   | TS   | 32            | S_AD[28]   | TS   | 33            | S_AD[29]   | TS   |

| 34            | VSS        | P    | 35            | S_AD[30]   | TS   | 36            | S_AD[31]   | TS   |

| 37            | S_REQ_L[0] | I    | 38            | S_REQ_L[1] | I    | 39            | S_REQ_L[2] | I    |

| 40            | VDD        | P    | 41            | VSS        | P    | 42            | S_REQ_L[3] | I    |

| 43            | S_GNT_L[0] | TS   | 44            | S_GNT_L[1] | TS   | 45            | S_GNT_L[2] | TS   |

| 46            | VDD        | P    | 47            | S_GNT_L[3] | TS   | 48            | S_RESET_L  | О    |

| Pin    | Name        | Type | Pin    | Name        | Туре | Pin    | Name        | Туре |

|--------|-------------|------|--------|-------------|------|--------|-------------|------|

| Number |             | **   | Number |             |      | Number | - 100       |      |

| 49     | S_CFN_L     | I    | 50     | VSS         | P    | 51     | S_CLKIN     | I    |

| 52     | S_VIO       | I    | 53     | S_CLKOUT[0] | O    | 54     | VSS         | P    |

| 55     | S_CLKOUT[1] | 0    | 56     | VDD         | P    | 57     | S_CLKOUT[2] | O    |

| 58     | VSS         | P    | 59     | S_CLKOUT[3] | 0    | 60     | VDD         | P    |

| 61     | S_CLKOUT[4] | O    | 62     | SCAN_EN     | I/O  | 63     | SCAN_TM_L   | I    |

| 64     | P_RESET_L   | I    | 65     | VSS         | P    | 66     | P_CLK       | I    |

| 67     | P_VIO       | I    | 68     | P_GNT_L     | I    | 69     | P_REQ_L     | TS   |

| 70     | P_AD[31]    | TS   | 71     | VSS         | P    | 72     | P_AD[30]    | TS   |

| 73     | P_AD[29]    | TS   | 74     | P_AD[28]    | TS   | 75     | VDD         | P    |

| 76     | P_AD[27]    | TS   | 77     | P_AD[26]    | TS   | 78     | P_AD[25]    | TS   |

| 79     | P_AD[24]    | TS   | 80     | VDD         | P    | 81     | VSS         | P    |

| 82     | P_CBE_L[3]  | TS   | 83     | P_IDSEL     | I    | 84     | P_AD[23]    | TS   |

| 85     | P_AD[22]    | TS   | 86     | VSS         | P    | 87     | P_AD[21]    | TS   |

| 88     | P_AD[20]    | TS   | 89     | P_AD[19]    | TS   | 90     | VDD         | P    |

| 91     | P_AD[18]    | TS   | 92     | P_AD[17]    | TS   | 93     | P_AD[16]    | TS   |

| 94     | VSS         | P    | 95     | P_CBE_L[2]  | TS   | 96     | P_FRAME_L   | STS  |

| 97     | P IRDY L    | STS  | 98     | VDD         | P    | 99     | P TRDY L    | STS  |

| 100    | P DEVSEL L  | STS  | 101    | P STOP L    | STS  | 102    | P LOCK L    | I    |

| 103    | VSS         | P    | 104    | P PERR L    | STS  | 105    | P SERR L    | OD   |

| 106    | P PAR       | TS   | 107    | P CBE L[1]  | TS   | 108    | VDD         | P    |

| 109    | P AD[15]    | TS   | 110    | P AD[14]    | TS   | 111    | P AD[13]    | TS   |

| 112    | VSS         | P    | 113    | P AD[12]    | TS   | 114    | P AD[11]    | TS   |

| 115    | P AD[10]    | TS   | 116    | VDD         | P    | 117    | P AD[9]     | TS   |

| 118    | P AD[8]     | TS   | 119    | VSS         | P    | 120    | VDD         | P    |

| 121    | VSS         | P    | 122    | P CBE L[0]  | TS   | 123    | P AD[7]     | TS   |

| 124    | P AD[6]     | TS   | 125    | VDD         | P    | 126    | P AD[5]     | TS   |

| 127    | P AD[4]     | TS   | 128    | VSS         | P    | 129    | P AD[3]     | TS   |

| 130    | P AD[2]     | TS   | 131    | VDD         | P    | 132    | P AD[1]     | TS   |

| 133    | P AD[0]     | TS   | 134    | S_AD[0]     | TS   | 135    | VSS         | P    |

| 136    | S_AD[1]     | TS   | 137    | S_AD[2]     | TS   | 138    | S AD[3]     | TS   |

| 139    | VDD         | P    | 140    | S_AD[4]     | TS   | 141    | S AD[5]     | TS   |

| 142    | S AD[6]     | TS   | 143    | VSS         | P    | 144    | S AD[7]     | TS   |

| 145    | S CBE L[0]  | TS   | 146    | S AD[8]     | TS   | 147    | VDD         | P    |

| 148    | S_AD[9]     | TS   | 149    | S AD[10]    | TS   | 150    | S AD[11]    | TS   |

| 151    | VSS         | P    | 152    | S_AD[12]    | TS   | 153    | S AD[13]    | TS   |

| 154    | VDD         | P    | 155    | S AD[14]    | TS   | 156    | S AD[15]    | TS   |

| 157    | VSS         | P    | 158    | S CBE L[1]  | TS   | 159    | BPCCE       | I    |

| 160    | VDD         | P    |        |             |      |        |             |      |

# 3 PCI BUS OPERATION

This Chapter offers information about PCI transactions, transaction forwarding across PI7C8152x, and transaction termination. The PI7C8152x has two 128-byte buffers for read data buffering of upstream and downstream transactions. Also, PI7C8152x has two 128-byte buffers for write data buffering of upstream and downstream transactions.

## 3.1 TYPES OF TRANSACTIONS

This section provides a summary of PCI transactions performed by PI7C8152x. *Table 3-1* lists the command code and name of each PCI transaction. The Master and Target columns indicate support for each transaction when PI7C8152x initiates transactions as a master, on the primary and secondary buses, and when PI7C8152x responds to transactions as a target, on the primary and secondary buses.

Table 3-1 PCI TRANSACTIONS

| Types o | of Transactions             | Initiates as Maste | r         | Responds as Target |                 |  |

|---------|-----------------------------|--------------------|-----------|--------------------|-----------------|--|

|         |                             | Primary            | Secondary | Primary            | Secondary       |  |

| 0000    | Interrupt Acknowledge       | N                  | N         | N                  | N               |  |

| 0001    | Special Cycle               | Y                  | Y         | N                  | N               |  |

| 0010    | I/O Read                    | Y                  | Y         | Y                  | Y               |  |

| 0011    | I/O Write                   | Y                  | Y         | Y                  | Y               |  |

| 0100    | Reserved                    | N                  | N         | N                  | N               |  |

| 0101    | Reserved                    | N                  | N         | N                  | N               |  |

| 0110    | Memory Read                 | Y                  | Y         | Y                  | Y               |  |

| 0111    | Memory Write                | Y                  | Y         | Y                  | Y               |  |

| 1000    | Reserved                    | N                  | N         | N                  | N               |  |

| 1001    | Reserved                    | N                  | N         | N                  | N               |  |

| 1010    | Configuration Read          | N                  | Y         | Y                  | N               |  |

| 1011    | Configuration Write         | Y (Type 1 only)    | Y         | Y                  | Y (Type 1 only) |  |

| 1100    | Memory Read Multiple        | Y                  | Y         | Y                  | Y               |  |

| 1101    | Dual Address Cycle          | Y                  | Y         | Y                  | Y               |  |

| 1110    | Memory Read Line            | Y                  | Y         | Y                  | Y               |  |

| 1111    | Memory Write and Invalidate | Y                  | Y         | Y                  | Y               |  |

As indicated in *Table 3-1*, the following PCI commands are not supported by PI7C8152x:

- PI7C8152x never initiates a PCI transaction with a reserved command code and, as a target, PI7C8152x ignores reserved command codes.

- PI7C8152x does not generate interrupt acknowledge transactions. PI7C8152x ignores interrupt acknowledge transactions as a target.

- PI7C8152x does not respond to special cycle transactions. PI7C8152x cannot guarantee delivery of a special cycle transaction to downstream buses because of the broadcast nature of the special cycle command and the inability to control the transaction as a target. To generate special cycle transactions on other PCI buses, either upstream or downstream, Type 1 configuration write must be used.

- PI7C8152x neither generates Type 0 configuration transactions on the primary PCI bus nor responds to Type 0 configuration transactions on the secondary PCI bus.

#### 3.2 SINGLE ADDRESS PHASE

A 32-bit address uses a single address phase. This address is driven on P\_AD[31:0], and the bus command is driven on P\_CBE[3:0]. PI7C8152x supports the linear increment address mode only, which is indicated when the lowest two address bits are equal to zero. If either of the lowest two address bits is nonzero, PI7C8152x automatically disconnects the transaction after the first data transfer.

#### 3.3 DUAL ADDRESS PHASE

A 64-bit address uses two address phases. The first address phase is denoted by the asserting edge of FRAME\_L. The second address phase always follows on the next clock cycle.

For a 32-bit interface, the first address phase contains dual address command code on the CBE\_L[3:0] lines, and the low 32 address bits on the AD[31:0] lines. The second address

phase consists of the specific memory transaction command code on the CBE\_L[3:0] lines, and the high 32 address bits on the AD[31:0] lines. In this way, 64-bit addressing can be supported on 32-bit PCI buses.

The *PCI-to-PCI Bridge Architecture Specification* supports the use of dual address transactions in the prefetchable memory range only. See Section 4.3.2 for a discussion of prefetchable address space. The PI7C8152x supports dual address transactions in both the upstream and the downstream direction. The PI7C8152x supports a programmable 64-bit address range in prefetchable memory for downstream forwarding of dual address transactions. Dual address transactions falling outside the prefetchable address range are forwarded upstream. Prefetching and posting are performed in a manner consistent with the guidelines given in this specification for each type of memory transaction in prefetchable memory space.

# 3.4 DEVICE SELECT (DEVSEL\_L) GENERATION

PI7C8152x always performs positive address decoding (medium decode) when accepting transactions on either the primary or secondary buses. PI7C8152x never does subtractive decode.

## 3.5 DATA PHASE

The address phase of a PCI transaction is followed by one or more data phases. A data phase is completed when IRDY\_L and either TRDY\_L or STOP\_L are asserted. A transfer of data occurs only when both IRDY\_L and TRDY\_L are asserted during the same PCI clock cycle. The last data phase of a transaction is indicated when FRAME\_L is de-asserted and both TRDY\_L and IRDY\_L are asserted, or when IRDY\_L and STOP\_L are asserted. See Section 3.9 for further discussion of transaction termination.

Depending on the command type, PI7C8152x can support multiple data phase PCI transactions. For detailed descriptions of how PI7C8152x imposes disconnect boundaries, see Section 3.6.4 for write address boundaries and Section 3.7.3 read address boundaries.

#### 3.6 WRITE TRANSACTIONS

Write transactions are treated as either posted write or delayed write transactions. *Table 3-2* shows the method of forwarding used for each type of write operation.

Table 3-2 WRITE TRANSACTION FORWARDING

| Type of Transaction         | Type of Forwarding         |

|-----------------------------|----------------------------|

| Memory Write                | Posted (except VGA memory) |

| Memory Write and Invalidate | Posted                     |

| Memory Write to VGA memory  | Delayed                    |

| I/O Write                   | Delayed                    |

| Type 1 Configuration Write  | Delayed                    |

#### 3.6.1 MEMORY WRITE TRANSACTIONS

Posted write forwarding is used for "Memory Write" and "Memory Write and Invalidate" transactions.

When PI7C8152x determines that a memory write transaction is to be forwarded across the bridge, PI7C8152x asserts DEVSEL\_L with medium decode timing and TRDY\_L in the next cycle, provided that enough buffer space is available in the posted memory write queue for the address and at least one DWORD of data. Under this condition, PI7C8152x accepts write data without obtaining access to the target bus. The PI7C8152x can accept one DWORD of write data every PCI clock cycle. That is, no target wait state is inserted. The write data is stored in an internal posted write buffers and is subsequently delivered to the target. The PI7C8152x continues to accept write data until one of the following events occurs:

- The initiator terminates the transaction by de-asserting FRAME L and IRDY L.

- An internal write address boundary is reached, such as a cache line boundary or an aligned 4KB boundary, depending on the transaction type.

- The posted write data buffer fills up.

When one of the last two events occurs, the PI7C8152x returns a target disconnect to the requesting initiator on this data phase to terminate the transaction.

Once the posted write data moves to the head of the posted data queue, PI7C8152x asserts its request on the target bus. This can occur while PI7C8152x is still receiving data on the initiator bus. When the grant for the target bus is received and the target bus is detected in the idle condition, PI7C8152x asserts FRAME\_L and drives the stored write address out on the target bus. On the following cycle, PI7C8152x drives the first DWORD of write data and continues to transfer write data until all write data corresponding to that transaction is delivered, or until a target termination is received. As long as write data exists in the queue, PI7C8152x can drive one DWORD of write data in each PCI clock cycle; that is, no master wait states are inserted. If write data is flowing through PI7C8152x and the initiator stalls, PI7C8152x will signal the last data phase for the current transaction at the target bus if the queue empties. PI7C8152x will restart the follow-on transactions if the queue has new data.

PI7C8152x ends the transaction on the target bus when one of the following conditions is met:

- All posted write data has been delivered to the target.

- The target returns a target disconnect or target retry (PI7C8152x starts another transaction to deliver the rest of the write data).

- The target returns a target abort (PI7C8152x discards remaining write data).

- The master latency timer expires, and PI7C8152x no longer has the target bus grant (PI7C8152x starts another transaction to deliver remaining write data).

Section 3.9.3.2 provides detailed information about how PI7C8152x responds to target termination during posted write transactions.

#### 3.6.2 MEMORY WRITE AND INVALIDATE

Posted write forwarding is used for Memory Write and Invalidate transactions.

The PI7C8152x disconnects Memory Write and Invalidate commands at aligned cache line boundaries. The cache line size value in the cache line size register gives the number of DWORD in a cache line.

If the value in the cache line size register does meet the memory write and invalidate conditions, the PI7C8152x returns a target disconnect to the initiator on a cache line boundary.

#### 3.6.3 DELAYED WRITE TRANSACTIONS

Delayed write forwarding is used for I/O write transactions and Type 1 configuration write transactions.

A delayed write transaction guarantees that the actual target response is returned back to the initiator without holding the initiating bus in wait states. A delayed write transaction is limited to a single DWORD data transfer.